|

Author: 윤 범진 기자 (Senior Reporter / Techworld, Inc.) Author: 윤 범진 기자 (Senior Reporter / Techworld, Inc.)

Source: 월간 전자부품 (Electronic Parts & Components Monthly), Jan. 2001 / 통권 155호 Source: 월간 전자부품 (Electronic Parts & Components Monthly), Jan. 2001 / 통권 155호

Date: 2001.3.16 Date: 2001.3.16

빠른 타임 투 마켓,

설계 융통성 제공으로 SoC 개발 지원

전략은 달라도 목표는 SoC

수많은 주문형반도체(ASIC) 회사들이 성공적으로 SoC(System on Chip)를 구현하여 차기 반도체시장에서 대박을 터뜨리기를 기대한다. 하지만, 실제 많은 임베디드 시스템 업체들이 ASIC 개발업체들의 초기개발비용(NRE)을 충분히 보장해 줄만큼 대량생산을 하지 못하는 실정이다. 따라서, NRE와 최소구매요구수량(MOQ)에 대한 부담이 거의 없는 프로그래머블로직디바이스(PLD)가 SoC 구현을 위한 합리적인 솔루션으로 주목을 받고 있다. 본지는 최근 왕성한 활동으로 SoC 시장을 개척하고 있는 PLD 업계를 둘러봤다. 수많은 주문형반도체(ASIC) 회사들이 성공적으로 SoC(System on Chip)를 구현하여 차기 반도체시장에서 대박을 터뜨리기를 기대한다. 하지만, 실제 많은 임베디드 시스템 업체들이 ASIC 개발업체들의 초기개발비용(NRE)을 충분히 보장해 줄만큼 대량생산을 하지 못하는 실정이다. 따라서, NRE와 최소구매요구수량(MOQ)에 대한 부담이 거의 없는 프로그래머블로직디바이스(PLD)가 SoC 구현을 위한 합리적인 솔루션으로 주목을 받고 있다. 본지는 최근 왕성한 활동으로 SoC 시장을 개척하고 있는 PLD 업계를 둘러봤다.

반도체 제조공정 기술의 발달로 집적도가 향상됨에 따라서 하나의 시스템을 이루는 프로세서, 메모리, 주변장치(Peripheral), 그리고 주변 로직들이 원 칩으로 구현 가능한 시대가 열렸다. 가장 유력한 솔루션이라 할 수 있는 ASIC의 경우, 시스템 전체가 집적화 됨으로써 설계부터 시작하여 그 이후 테스트 단계에 이르기까지 검증해야 할 시간 및 양적인 부분 또한 함께 증가되므로 개발기간의 장기화와 비용증가를 피할 수 없다. 이러한 틈새를 노린 프로그래머블 로직 업체들의 최근 행보가 주목된다.

주요 PLD 벤더들은 자사의 디바이스에 프로세서 코어를 임베디드하여 사용자가 직접 SoC를 만들 수 있도록 하고 있다. PLD 벤더들은 이것을 자사의 전략에 따라 서로 다른 이름으로 부르고 있지만, SoC 구현을 위한 최적의 솔루션을 제공한다는 데는 일치한다.

알테라는 이러한 솔루션을 SoPC (System on a Programmable Chip)로, 퀵로직은 ESP(Embedded Standard Products)라 부르고 있다. 한편, 자일링스는 IBM의 명령어축약형컴퓨팅(RISC) 방식의 PowerPC 프로세서 코어와 코어커넥트 버스를 라이선스하여 자사 버텍스(Virtex)-II FPGA에 내장시켜 올 중반경 샘플 출시할 계획이며, 액텔은 임베디드 FPGA 디자인을 ASIC에 구현하는 색다른 전략을 구사하고 있다.

알테라는 SOPC를 구현할 수 있는 Excalibur 임베디드 프로세서 솔루션과 IP 코어, 그리고 고집적화 된 디바이스 및 효과적인 툴 지원과 같은 분야에 알테라의 자본과 기술력을 집중하고 있다.

알테라의 SoPC는 PLD의 장점인 유연성과 SoC가 가지는 시스템 통합의 장점을 결합하여 사용자가 설계하고자 하는 로직은 PLD 영역에 기존과 동일한 공정에 따라 구현하고, 구현된 로직과 시스템과의 인터페이스 및 시스템의 설정 등은 툴 상에서 사용자 요구대로 선택만 하면 빠른 시간 내에 하나의 시스템을 설계할 수 있다.

뿐만 아니라, SoPC에서는 H/W적인 문제 못지 않게 S/W에 대한 비중도 높아지게 되는데 시스템에 동반되는 내부 프로세서들로 인하여 시스템 운영에 필요한 운영체제(OS), 그리고 전체 기능(function)의 일부분을 소프트웨어로 구현할 경우 등을 포함하여 S/W 개발에 필요한 툴 및 환경을 제공하게 된다.

H/W 및 S/W 개발 툴 & 환경

알테라의 MAX+PLUS II나 Quartus에서는 설계 입력의 형태로 schematic capture와 HDL 방식을 모두 지원하고 있으나, SoPC의 설계를 효율적으로 진행하기 위하여 하드웨어 설계 언어인 HDL에 최적화 되어 있다. 알테라는 H/W 개발 툴인 Quartus에 SoPC 지원기능을 한층 강화한 Quartus II를 이 달중에 출시할 예정이다.

H/W 개발환경은 최근 추세에 따라 HDL을 근간으로 하며 SoPC Builder라는 system configurator가 포함될 예정이다. 따라서, H/W 설계자는 기존의 Megafunction Wizard와 함께 알테라가 제공하는 IP 코어 등을 이용하여 PLD 영역을 다양하게 활용 가능하며, 전체 설계를 구현하여 Quartus에 입력, PLD에 원하는 로직을 만들 수 있다.

S/W인 경우, 가장 중요한 부분은 내장된 프로세서에 맞는 컴파일러와 디버깅 툴이다. 알테라의 Quartus 차기 버전에서는 기존에 있던 compiler/Simulation mode 외에 Software mode를 추가하여 Quartus 내부 자체에 C/C++ compiler /assembler/linker 등의 기능을 지원한다. 기존에 HDL을 입력하여 H/W를 설계하듯이 Quartus Text Editor에서 C/C++ code를 입력한 후 이후의 모든 과정을 Quartus 내부에서 처리 가능하며 이를 디바이스로 내부의 RAM 혹은 외부 SDRAM 등으로 프로그래밍 할 수 있다.

최초의 SoC 제품 Excalibur

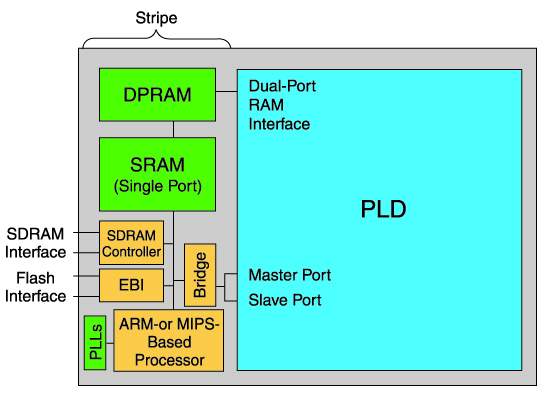

Excalibur란, PLD 업계에서 최초로 SoPC를 구현한 알테라의 최신 디바이스 제품군 이름으로 내부에 사용된 RISC 코어의 종류에 따라 다음 3가지로 분류된다(그림 1 참조).

그림 1. ARM/MIPS Excalibur의 블록 다이어그램

■ Nios

Nios는 알테라가 개발한 소프트코어 RISC 프로세서이다. 이 프로세서는 설계자가 툴에서 지정한 spec에 맞는 RISC 코어 및 주변 블록들의 HDL code가 자동적으로 생성되고 로직 synthesis 과정을 거쳐 Quartus에서 선택한 디바이스에 fitting을 마치면 최종적으로 디바이스를 프로그래밍하는 binary data를 이용하여 실질적인 시스템 회로를 PLD에 구현하게 된다.

따라서, PLD 영역에 적용시켜 프로세서를 포함한 각종 주변의 인터페이스 블록을 구현할 수 있다. 약 50MIPS 정도의 연산능력을 가지고 있으며 소프트코어이므로 향후 다양한 알테라 디바이스에 적용 가능한 장점을 가지고 있다.

■ ARM

ARM사로부터 32비트 RISC 아키텍처인 ARM9TDMI(ARM922T) 코어를 라이선스하여 기존의 PLD 영역 이외의 스트라이프(stripe)라고 부르는 실리콘 상의 특정 영역에 ARM 코어, AHB 버스(ARM High performance Bus로 AMBA 제품군 중 최근에 발표된 버스로 성능향상을 위하여 모든 동작을 클록 rising에 동기되도록 설계되어 있다), 내부 메모리 및 UART, 외부 메모리 컨트롤러 등을 집적했다.

Nios와는 달리 하드코어(Hardcore) 프로세서가 내장되어 있고, ARM9의 경우 ARM7에 비하여 코어 자체에 각각 8Kbyte의 데이터와 명령 캐시(instruction cache)를 가지고 있으며 200MHz에서 동작하도록 설계되어 있어 200MIPS 정도의 연산 성능을 가지고 있다.

■ MIPS

ARM 코어가 MIPS사의 MIPS32 4Kc 코어로 바뀐 디바이스로 스트라이프 영역의 나머지 부분이나 PLD 부분은 ARM과 동일하다. MIPS 코어는 ARM9 코어보다 많은 캐시 메모리를 포함하고 있으며(16Kbyte), 연산능력은 클록 한 주기 동안에 32bit×16bit MAC(곱셈과 덧셈을 동시에 수행하는 연산)을 수행한다. 또한 S/W 디버깅 시에 외부 디버그 툴과 서로 인터페이스 할 목적으로 EJTAG라는 내장 모듈을 포함하고 있다.

그림 2. 알테라의 SOPC 보드 외형

<자료지원: 손선미 차장>

자일링스, FPGA 플랫폼 디자인 방법론 공개

|

1백만 게이트 집적도 FPGA가 등장함에 따라 PLD 분야에 새로운 가능성과 잠재력을 지닌 애플리케이션 세계가 열리고 있다. 그러나, 이러한 새로운 기회들과 함께 많은 도전들이 다가오고 있다.

자일링스의 Virtex-Ⅱ FPGA의 프로그래머블 로직 회로 및 소프트코어와, 저가 -고성능의 PowerPC(그리고 기타 하드코어)를 결합한다는 것은, ASIC 설계자들이 SoC ASIC으로 이전할 때 직면하는 문제와 유사한 것이다.

수백만 게이트급 FPGA 시장의 모든 관련자들은 점점 더 복잡해지는 기술, 개발비용 증가, 표준 변화, 디자인 엔지니어의 부족, 점점 더 빨라지는 디자인 사이클과 같은 문제에 봉착해 있다. 또한 복잡성이 증가함에 따라 제품 출시의 신속성은 제조측면보다는 디자인 시간에 좌우되는데, 이는 FPGA의 가장 중요한 경쟁력 중 하나이다.

이러한 문제점을 극복하기 위해서는 공통의 아키텍처, 혹은 플랫폼을 공유해야 한다는 주장이 강하게 제기되고 있다. 특히 유사한 애플리케이션을 타깃으로 하는 플랫폼들의 경우에는 더욱 그러하다.

플랫폼이란, 셀룰러폰 기지국이나 셋톱박스와 같은 특정 애플리케이션에 맞게 형성된 하나의 베이직시스템 아키텍처이다. 플랫폼은 소프트웨어와 주문형 로직, IP의 통합을 통해 주문 생산된다.

FPGA 플랫폼은 통합 FPGA 패브릭을 사용하는 주문형 로직과 IP를 통합함으로써 제품 차별화를 가능하게 한다. 수백만 게이트급 FPGA 시대에 이러한 플랫폼들은 표준 부품을 재창출함으로써 시간과 자원의 낭비없이 디자이너들이 주문형 IP를 통한 부가가치 창출에 주력할 수 있게 한다는 점에 그 중요성이 있다.

플랫폼 기반 설계

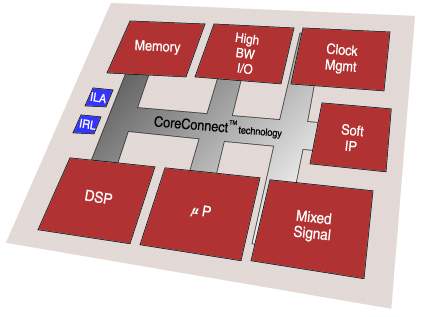

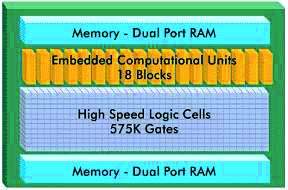

자일링스 플랫폼의 핵심은 Virtex-Ⅱ 플랫폼에 있는 IBM의 PowerPC 프로세서 코어와 같은 임베디드 프로세서이다. 전형적인 플랫폼은 버스, DSP, I/O 채널, 다양한 신호처리 기능, 메모리 및 구성 가능한(Configurable) 로직을 포함하고 있다(그림 3 참조).

그림 3. PowerPC 프로세서가 내장된 자일링스의 Virtex-II

FPGA 디자인은 단순히 게이트 디자인이라기보다는 플랫폼 디자인이다. 따라서 이제는 전체 시스템의 디자인에 초점을 맞춰야 한다. 시스템 레벨 디자인을 통한 효과적인 플랫폼 개발을 위해서는 다음의 4가지 사항이 고려되어야 한다.

- 하드웨어 디자인

- 소프트웨어 디자인

- 하드웨어, 소프트웨어, IP의 통합

- 전체 시스템(온 칩) 검사

IP 통합

플랫폼 기반 디자인의 장점은 서로 다른 전용 로직과 써드파티 IP들을 통합할 수 있도록 지원한다는 것이다. 모든 시스템온칩 ASIC 또는 플랫폼 FPGA 상의 주문형 부분이 바로 다른 디바이스와의 경쟁력과 차별화를 제공하고 있는 것이다.

이제는 단일 FPGA 상에서 구현될 수 있는 게이트 수가 크게 증가하면서 이러한 게이트들을 만들어낼 때 어떻게 하면 더 생산적이 될 수 있느냐 하는 문제에 직면하게 되었다. 이에 대한 한 가지 확실한 방법은 디자인 재사용을 통해 기존 게이트를 활용하는 방법이다. 자일링스는 재사용 가능한 빌딩 블록 및 방법론 활동을 통해 ASIC 및 FPGA 디자이너들이 다양한 IP를 재활용함으로써 시간을 절약할 수 있는 여러 가지 옵션을 제공한다.

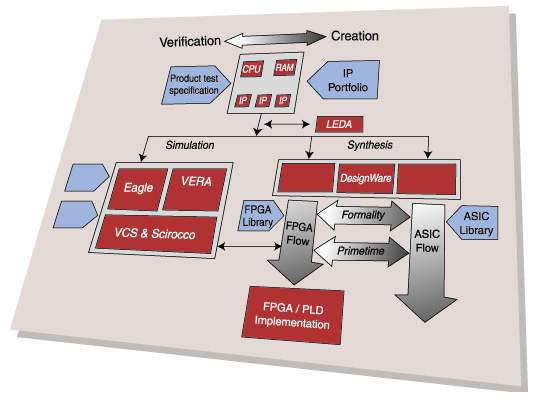

시스템 검증

시스템온칩 FPGA의 과제는 시스템을 구성하는 개별 블록 뿐만 아니라, 프로세서 코어를 포함한 전체 시스템을 검증할 수 있는 방법이다. 이를 위해서는 고속 시뮬레이션 뿐만 아니라 완전한 고급 검증 툴 어레이가 필요하다. 특히, 테스트벤치 생성, 커버리지 툴, 정식(formal) 검증, 프로세서 및 기타 IP의 시뮬레이션 모델, 정적(static) 타이밍 분석 툴이 플랫폼 기반 디자인 시 필수적이다(그림 4 참조).

그림 4. 플랫폼 검증 툴

임베디드 프로세서를 위한 참조 디자인

자일링스는 Virtex와 Spartan 시리즈 FPGA를 타깃으로 한 IBM의 PowerPC, 인텔의 StrongARM, Pentium class와 QED 프로세서를 위한 참조 디자인을 최근 발표했다.

이번에 발표한 참조 디자인들은 자일링스의 플랫폼인 Xilinx Empower!의 일환으로 제공되며, 이는 임베디드 프로세서에 프로그래머블 시스템을 제공하는 한편 커스텀 솔루션을 추가로 제공한다.

이로 인해 설계자들은 성능 및 가격과 디자인 환경 측면 모두를 관리할 수 있게 된다.

■ PowerPC 60X 멀티 프로세서 bus 인터페이스

멀티 PowerPC 프로세서에 인터페이스 하기 위한 참조 디자인이며 이는 Virtex-E나 Virtex-II FPGA에 구현된 bus arbiter와 프로토콜, SDRAM, 플래시메모리 컨트롤러를 포함한다.

■ StrongARM 디자인과 개발 킷

인텔의 StrongARM SA-1110 프로세서용 32-bit/33-MHz PCI와 100MHz SDRAM 인터페이스는 현재 구매 가능하다. 이 디자인은 1십만 게이트 Spartan-II FPGA를 사용했다.

■ Pentium과 QED 프로세서를 위한 고성능 인터페이스

Virtex-E와 Virtex-II FPGA에 집접 인터페이스 하기 위하여 250MHz QED RM7000A 프로세서와 850MHz Pentium class 프로세서용 인터페이스 참조 디자인이다. Spartan-II 제품군 또한 Pentium 디자인을 지원한다.

■ Virtex-II 디바이스에 임베디드 되어 있는 PowerPC 코어

자일링스는 IBM의 하드코어 PowerPC 405 마이크로프로세서를 Virtex-II 아키텍처에 임베디드 하고 있으며 300MHz에서 동작하여 420 Dhrystone Mips 이상의 성능을 구현한다. PowerPC 405 코어는 6Gbyte peak 이상의 통신 대역폭을 제공한다.

이상의 참조용 디자인들은 자일링스 웹사이트(Virtex 페이지)를 통해 무료로 이용 가능하다.

결론적으로 임베디드 프로세서 코어와 특정 애플리케이션 부품들을 포함하고 있는 FPGA는 플랫폼 기반 디자인이 필요하다. 플랫폼 기반 디자인이란 오늘날 이미 사용되고 있는 일종의 RTL 로직 디자인 툴과, 대부분의 FPGA 설계자들에게는 아직 낯선 시스템 차원의 포괄적인 디자인 툴 스위트이다.

이제 FPGA 디자인은 단순한 로직 시대를 넘어서고 있다. PowerPC와 같이 임베디드 프로세서 코어를 포함하고 있는 FPGA의 도래와 함께, ASIC 디자이너들과 마찬가지로 FPGA 디자이너는 통합 시스템 디자인이라는 도전에 직면하게 될 것이다.

<자료지원: 변형구 기술부장>

퀵로직, ESP 제품 전략으로 SoC 개발 지원

|

ESP(Embedded Standard Products) 기술의 선구자를 자체하는 퀵로직(QuickLogic)은 다양한 ESP 제품군을 제공한다. 기본 구조는 산업계에서 널리 사용되는 표준 기능들을 기존 PLD 제품의 로직 게이트와 주변구성에 필요한 부가 기능을 원칩화시킨 SoC 형태의 구조를 갖는다. ESP(Embedded Standard Products) 기술의 선구자를 자체하는 퀵로직(QuickLogic)은 다양한 ESP 제품군을 제공한다. 기본 구조는 산업계에서 널리 사용되는 표준 기능들을 기존 PLD 제품의 로직 게이트와 주변구성에 필요한 부가 기능을 원칩화시킨 SoC 형태의 구조를 갖는다.

FPGA(Field Programmable Gate Array)를 기본으로 성장해 온 퀵로직은 향후 회사의 모든 정책과 방향을 ESP 제품쪽에 집중하기로 하고, 기존 FPGA(PLD 시장포함)와 표준칩 시장의 상당 부분을 공략 대상으로 삼고 있다.

퀵로직사의 국내 총판 대리점인 와이케이로직(YK Logic)의 하철용 차장은 “국내시장의 경우, 최근 SoC 개념의 칩 수요가 증가 추세에 있으며 매년 평균 10% 이상씩 성장할 것으로 예상된다.”면서 “특히 인터넷, 통신장비 관련 시장에서 많은 수요가 있을 것으로 예측돼 퀵로직은 새로운 제품을 이 시장을 타깃으로 출시 예정이며 모든 마케팅 전략을 집중할 계획이다.”라고 말했다.

이와 관련, 와이케이로직은 퀵로직의 ESP 전략에 발맞춰 ESP 관련 전문인력을 구성하고, 특히 핵심 요소인 엔지니어링 기술지원을 위해 전문인력을 집중 양성하고 있다. 현재 퀵로직은 ESP 제품군으로 다음의 6가지를 발표했다.

■ QuickRAM

QuickRAM은 RAM 블록이 Hardwired(ASIC) 형태로 임베디드 되어 있으며 최대 90K 게이트 용량의 구성 가능한 로직이 함께 원칩으로 제공된다.

■ QuickDSP

실시간 고속연산을 필요로 하는 애플리케이션에 널리 이용되는 DSP 코어 블록, RAM 블록이 임베디드 되어 있으며 최대 700K 게이트 용량의 구성 가능한 로직이 함께 원칩으로 제공된다. 향후 FIR, IIR Filter와 같은 하이엔드급 애플리케이션에 사용될 것으로 예상된다.

그림 5. QuickDSP 블록도

■ QuickSD

고속 시리얼 데이터 전송에 응용되는 최대 8채널 용량의 버스 LVDS SERDES(Low Voltage Differential Signaling Serializer/Deserializer), RAM 블록, PLL 블록이 임베디드 되어 있으며 최대 700K 게이트 용량의 구성 가능한 로직이 함께 원칩으로 제공된다. 고속 통신 전송시스템을 타깃으로 하고 있다.

■ QuickFC

주로 RAID와 같은 범용(mass) 스토리지 애플리케이션에 고속 데이터 입·출력 인터페이스에 응용되는 Fibre Channel ENDEC(Encoder/Decoder), RAM 블록이 임베디드 되어 있다. 최대 150K 게이트 용량의 구성 가능한 로직이 함께 원칩으로 제공되며 SCSI, IDE 인터페이스 방식을 대체할 제품으로 퀵로직은 개발하고 있다.

■ QuickMIPS

프로세서 코어가 임베디드 되는 추세에 맞춰 개발된 QuickMIPS는 MIPS32 4Kc 프로세서 코어, RAM 블록이 임베디드 되어 있으며 최대 700K 게이트 용량의 구성 가능한 로직이 함께 원칩으로 제공된다. 150에서 200MHz에서 구동하는 이 프로세서 외에 퀵로직은 64비트 MIPS64 5Kc 코어를 내장하는 옵션을 제공한다. 이 회사는 공식적인 발표는 하지 않았지만, 버스 인터커넥트로 AMBA 버스를 사용할 것으로 알려졌다.

■ QuickPCI

현재 표준 버스로서 각광을 받고있는 PCI interface/controller, RAM 블록이 임베디드 되어 있으며 크게 2가지 형태로 32비트와 64비트가 지원된다.

32비트의 경우 Master/Target, Target Only Version이 제공된다. 현재 PCI 버스를 응용하고자 하는 모든 분야에서 사용이 가능하며, PCI 버스 브릿지 기능 외에 주변 로직 게이트와 메모리 부분을 1개의 칩에 원칩화 시킬 수 있는 특징을 가지고 있다. DVR, VoIP와 같은 시스템에 적용할 수 있다.

표 1. 퀵로직의 QuickPCI 제품군

|

Device

|

PCI Function

|

PCI Speed

|

PCI Width

|

RAM Bits

|

FPGA Gates

|

Packages

|

|

QL5030-33

|

Target

|

33MHz

|

32-Bits

|

11.5K

|

4.5K

|

144-TQFP

|

|

QL5032-33

|

Master / Target

|

33MHz

|

32-Bits

|

16K

|

14.5K

|

208-PQFP

256-PBGA

|

|

QL5064-33

|

Master / Target

|

33MHz

|

32-or 64-Bits

|

12.7K

|

30K

|

456-PBGA

|

|

QL5064-66

|

Master / Target

|

66MHz

|

32-or 64-Bits

|

12.7K

|

30K

|

456-PBGA

|

|

QL5064-75

|

Master / Target

|

75MHz

|

32-or 64-Bits

|

12.7K

|

30K

|

456-PBGA

|

<자료지원: 하철용 차장/와이케이로직>

액텔은 지난해 ASIC과 ASSP에 임베디드 FPGA 디자인을 지원하기 위한 전략을 공개했다. 오는 2004년까지 이 시장규모가 24억 달러에 이를 것으로 전망되는 가운데, 액텔은 선두적인 ASIC 및 ASSP 제공업체들과 시스템 디자인너들에 의해 지지되는 SoC 시장을 지원하기 위해서 요구되는 구성요소 확보에 전력하고 있다.

액텔의 목표는 디자이너들에게 임베디드 FPFA 솔루션을 제공하는 것으로 기술, 제품, 디자인 툴, 그리고 방법론과 중요한 EDA 및 ASIC 협력 등을 포함한다. 이러한 전략 추진의 일환으로 액텔은 임베디드 FPGA IP(Intellectual Property) 선두업체인 프로스 테크놀로지사(Prosys Technology)를 인수했다. 프로스를 인수한 입찰가격에 대해서는 아직 공개되지 않았다. 이외에도 최근 FPGA 공급업체로서 액텔의 코어 능력을 향상시키기 위해 플래시에 기반한 FPGA 기술인 유사 ASIC(ASIC-like) 개발업체인 게이트필드사(GateField)를 인수하는데 합의했다. 액텔의 임베디드 FPGA 전략의 일부로서, 이러한 인수는 이 분야에서 기존의 FPGA 공급업체들의 솔루션과는 아주 다른 제품을 선보이게 될 것으로 전망된다.

액텔이 추구하고 있는 임베디드 FPGA 시장은 4년 후에는 대규모의 시장을 창출할 것으로 시장조사 기관은 내다보고 있다. 따라서, 아직 열리지 않은 임베디드 FPGA 시장에서 향후 액텔은 중요한 역할을 담당하게 될 것으로 전망된다.

액텔의 전략은 최초로 완벽한 임베디드 FPGA 솔루션을 위해 하부구조(framework)를 산업계에 제공하는 것이다. 이를 위해 액텔은 핵심기술을 비롯해 협력관계 형성, 표준 방법론 및 디자인 플로의 채용에 대한 조정 업무를 담당하게 될 새로운 조직을 구상하고 있다. 새롭게 구성되는 조직은 신규시장을 선점하기 위해 액텔 IP 제품을 정의, 개발, 판매하게 된다.

액텔은 궁극적으로 임베디드 FPGA 시장에서 필요한 고부가가치의 ‘스타(star) IP’를 공급하는데 목표를 두고 있다. 그리고 이 회사는 점진적으로 임베디드 FPGA 솔루션에 유연성을 추가해 나갈 계획이다.

이를 위해, 액텔은 ASIC EDA S/W 공급업체에 의해 지원되고 있는 시시각각 변하는 기술, 기능성, 성능의 IP 코어를 포함하여 세계 주요 반도체 파운드리를 활용하기로 했다.

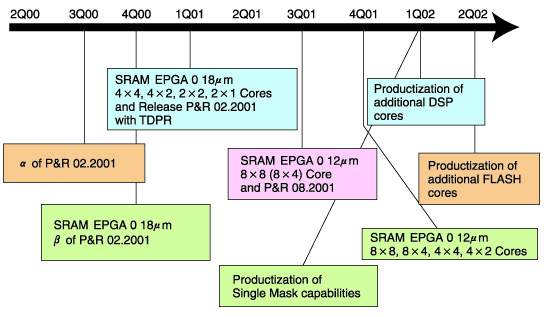

현재 액텔은 임베디드 FPGA 솔루션 전략의 일환으로 소위 프로젝트 ‘PegaSys’를 추진하고 있다(그림 6 참조). 이를 통해 개발된 제품군의 이름은 Varicore.

그림 6. 프로젝트 PegaSys 로드맵

액텔은 이 프로젝트에 따라 올 1사분기중에 0.18마이크론 SRAM EPGA 코어를 발표할 예정이며, 소프트웨어는 2사분기중에 발표할 계획이다.

액텔은 가장 빠르게 성장하는 시장이 표준셀 디자인을 위한 임베디드 프로그래머블 코어가 될 것이라는 확신 아래, ASIC이나 ASSP 디자인 업체를 대상으로 본 사업을 강화해 나갈 방침이다.

한편, 액텔은 최근 통신, 네트워킹, 텔레콤 시장을 겨냥해 새롭게 5개의 고성능 IP 코어를 발표했다. 이번에 발표한 새로운 솔루션은 8b/10b 엔코더/디코더, CRC(Configurable cyclic Redundancy Code), SDRAM 컨트롤러, PCI 버스 arbiter, UART 등을 포함한다.

이 회사는 자사의 고성능 FPGA 제품인 SX-A나 eX 디바이스를 디자인할 때, 새로운 코어를 적용하면 빠른 타임 투 마켓, 디자인 비용 절감, 고속 성능향상 등의 이점을 제공한다고 설명했다.

|

![]()