![]()

작성일: 2006.04.17

by 글: 존 타이터스(Jon Titus) 기자

FPGA, 마이크로프로세서, 마이크로컨트롤러 하나만으로는 주어진 작업을 수행할 수 없는 경우가 종종 있다. 설계팀이

성능을 과대 평가했거나 마케팅 부서에서 너무 많은 부가 기능을 더한 것이 원인일 수 있다. 이런 경우 FPGA와 프로세서 코어의

조합이 성공과 실패를 가름하게 된다. 최근 많은 FPGA 업체들이 FPGA에 내장되는 하드 프로세서 코어를 사용해 설계할 수 있는

길을 열어주고 있다. 또 다른 방편으로, FPGA로 시작해 소프트 프로세서 IP(intellectual property)를

추가함으로써 최종 디자인에 반영하도록 돕고 있다.

FPGA, 마이크로프로세서, 마이크로컨트롤러 하나만으로는 주어진 작업을 수행할 수 없는 경우가 종종 있다. 설계팀이

성능을 과대 평가했거나 마케팅 부서에서 너무 많은 부가 기능을 더한 것이 원인일 수 있다. 이런 경우 FPGA와 프로세서 코어의

조합이 성공과 실패를 가름하게 된다. 최근 많은 FPGA 업체들이 FPGA에 내장되는 하드 프로세서 코어를 사용해 설계할 수 있는

길을 열어주고 있다. 또 다른 방편으로, FPGA로 시작해 소프트 프로세서 IP(intellectual property)를

추가함으로써 최종 디자인에 반영하도록 돕고 있다.

자일링스 임베디드 개발 툴 사업부 마케팅팀 제이 구드는 “FPGA와 온칩 프로세서를 한데 묶으면 하드웨어나 소프트웨어를 세부적으로 조정할 수 있고 PCB를 새로 만들거나 프로세서를 추가하지 않고도 변경사항을 테스트할 수 있다”고 말했다. 그는 수정 작업 때문에 3개의 UART가 추가적으로 필요한 경우를 예로 들면서 다음과 같이 말한다. “마이크로컨트롤러 칩은 UART를 제공하지 못하지만 FPGA와 프로세서를 통합하면 주변기기를 무제한적으로 제공받을 수 있게 돼 아무런 문제 없이 UART를 추가할 수 있다.”

같은 회사에서 임베디드 마케팅 전문가로 일하고 있는 데릭 팔머는 “소프트웨어에서는 ‘Feature Creep(주: 기능을 하나씩 추가하다가 전체 프로젝트가 위험에 빠질 만큼 비대해지는 현상)’ 문제가 항상 일어난다”고 지적하고, “기능 추가에 필요한 코드가 많지 않기 때문에 언제든 소프트웨어에 추가할 수 있을 것으로 마케팅 직원들은 생각한다”고 말했다. 이에 따라, 설계팀은 본래의 사양에 필요한 것보다 서너 배 뛰어난 프로세서를 선택한다. 그러나 FPGA에 하나 이상의 프로세서를 내장하면 설계가 복잡해져 하드웨어와 소프트웨어를 분할해야 한다.

일반적으로 설계 엔지니어들은 프로세서를 하드 프로세서로 구현할 것인지 아니면 소프트 프로세서로 구현할 것인지 결정해야 한다. 래티스 세미컨덕터의 고든 핸즈 마케팅 디렉터는 “소프트 방식이 훨씬 더 유리하다”고 말했다. 이 회사는 최근 8비트 LatticeMICO-8 프로세서 아키텍처를 발표했다. 이 아키텍처는 래티스의 FPGA와 함께 동작하며, 무료 오픈소스 형식의 라이선스로 제공된다. 핸즈 마케팅 디렉터는 “우리는 래티스 FPGA 사용자를 지원하지만 이들은 MICO-8 디자인을 ASIC 또는 다른 FPGA 아키텍처로 얼마든지 전환할 수 있다”면서, “우리는 사용자들을 특정 디바이스 제품군 내에 묶어두지 않고 있다”고 말했다.

래티스는 또한 어셈블러와 시뮬레이터를 오픈소스 라이선스로 제공한다. 따라서 엔지니어는 마이크로컨트롤러의 아키텍처를 그들의 애플리케이션에 맞게 변경할 수 있다. 아키텍처가 수정될 경우 어셈블러도 수정할 수 있다.

표준 아키텍처 선택

래티스는 MICO8 아키텍처뿐 아니라 IP 업체인 DCD(Digital Core Design)의 8051 및 PIC 아키텍처도 지원한다. DCD는 자사 아키텍처가 래티스 FPGA 아키텍처에 잘 맞을 뿐 아니라, 래티스 FPGA 개발 툴 내에서 우수한 성능을 구현한다고 밝혔다.

많은 개발자들이 진부화(obsolescence)를 방지하기 위해 FPGA에 프로세서 코어를 통합하는 방법을 선택한다고 핸즈 마케팅 디렉터는 설명했다. 그는 “FPGA 내에서 마이크로컨트롤러를 IP로 구현함으로써 개발자들은 디자인의 미래를 보장받을 수 있다”고 말했다. FPGA 기술이 발전하면서 개발자들은 VHDL 코드를 신형 디바이스에 탑재할 수 있게 됐다. 마이크로컨트롤러 IP는 기존 코드와 함께 변함 없이 그대로 유지된다.

32비트로 이동

디자인에 별도의 처리 성능이 필요한 경우 약 2년 전 발표된 알테라 32비트 Nios II 프로세서를 통해 해결할 수 있다. 이 소프트 코어 프로세서는 최대 256개의 사용자 정의 명령어를 포함할 수 있다.

알테라의 IP 비즈니스 사업부 밥 가렛 수석 마케팅 매니저는 “XYZ라는 곱셈 연산과 같이 원하는 명령어를 RTL에 작성할 수 있다”며, “시스템은 XYZ라는 이름의 새로운 명령어를 인식하지만 이를 구현하기 위해 컴파일러를 수정하지는 않아도 된다”고 말했다. 빌드 프로세스에서 IDE는 XYZ를 위한 매크로를 생성하고, 개발자는 이 매크로를 ‘제로 오버헤드(zero-overhead)’ 서브루틴 호출과 마찬가지 방식으로 사용할 수 있다. 가렛 수석 마케팅 매니저에 따르면, 대부분의 엔지니어는 주로 데이터 처리 작업을 가속화하는데 사용되는 6~7개의 맞춤형 명령어를 코딩하고 있다고 한다.

“엔지니어들은 단순한 프로세서 이상의 것을 원한다. 따라서 우리는 개발자가 그들의 디자인을 위한 주변기기와 프로세서를 선택할 수 있게 하는 툴인 SOPC(시스템 온 프로그래머블 칩) 빌더를 제공하고 있다. 개발자는 이 툴을 사용해 프로세서를 메모리에 연결하고 DMA 채널을 주변기기에 연결할 수 있다.”

알테라는 Nios II 아키텍처를 두 가지 방법으로 라이선스한다. 대부분의 사람들은 Nios 라이선스, Nios 및 주변기기 IP, 개발 툴, 개발 보드, 레퍼런스 디자인 등이 포함된 개발 키트를 구매한다. 가렛 수석 마케팅 매니저에 따르면, 엔지니어는 학습과정을 금방 끝마칠 수 있다고 한다. 키트 가격은 1,000달러 이하로 책정됐다.

알테라의 이클립스(Eclipse) 기반 IDE는 타이머, UART와 같은 주변기기를 검사하고, 이를 위한 맞춤형 소프트웨어 라이브러리를 구축한다. 가렛 수석 마케팅 매니저는 “엔지니어는 샘플 프로그램을 통해 즉시 시작할 수 있다”면서, “이 프로그램은 입문과정부터 웹 서버와 네트워크 연결에 이르기까지 다양한 내용을 담고 있다”고 말했다.

또한 엔지니어는 알테라 웹 사이트에서 Nios IP와 툴을 무료로 다운받아 애플리케이션을 컴파일•실행•디버그•테스트할 수 있다. 이를 통해 설계에 필요한 로직 부품의 수와 메모리 용량 등 핵심 정보를 예비 연구기간 동안 얻을 수 있다. 엔지니어가 Nios 디자인을 채택하기로 결정한 경우 Nios IP를 라이선스하거나(495달러) 완전한 개발 키트를 구매하면 된다. 영구 라이선스를 통해 Nios II IP를 모든 알테라 FPGA 및 HardCopy 스트럭처드 ASIC에 적용할 수 있다.

FPGA에 탑재된 ARM7

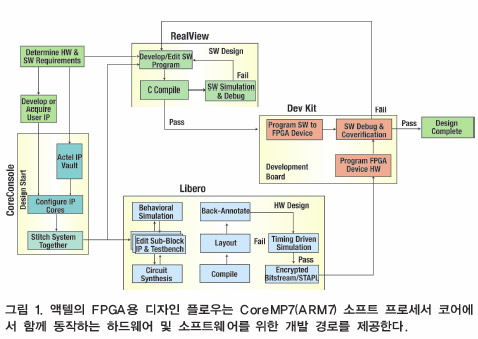

ARM7 프로세서가 인기를 끌면서 곧 FPGA 업체들이 이 프로세서를 FPGA 코어로 제공할 것으로 예측되는 가운데, 액텔은 ARM7을 소프트 코어로 제공하는 새로운 CorelMP7을 내놓았다. 액텔의 애플리케이션 및 IP 솔루션 담당 얀킨 타누한 수석 디렉터는 다음과 같이 말한다. “CoreMP7은 블랙박스와 같다. 이 제품은 우리의 FPGA 아키텍처와 잘 맞물리도록 조정됐다. 독자적인 RTL 또는 네트리스트는 전혀 포함되지 않았다. ARM7은 칩상에서 구현 정의 형태로 존재한다. 엔지니어가 개발 시스템에서 소프트웨어를 FPGA 칩으로 옮기면 우리는 AES(Advanced Encryption Standard)를 사용해 비트 스트림을 암호화한다.” CoreMP7은 ProASIC3 플래시 칩과 같은 ARM7 지원 FPGA에서만 실행된다. 이 칩을 구매하면 라이선스 요금이나 로열티 없이 ARM7을 무료로 얻게 된다.

2006년 초부터 판매되기 시작한 CoreMP7 개발 키트에는 600만 게이트 FPGA를 갖춘 스탠드얼론형 보드, 2MB 플래시 메모리, 2MB SRAM이 포함된다. I/O 포트는 이더넷, CANbus, RS-232C 연결을 제공한다.

타누한 수석 디렉터는 CoreMP7 프로세서에 대한 기존 ARM7 소프트웨어 구현의 편리함을 강조했다. “우리는 액텔의 CoreConsole IP 개발 플랫폼과 Libero IDE를 사용하기 때문에 FPGA 개발자는 다른 툴에 대한 사용법을 익힐 필요 없이 ARM7 코어를 사용할 수 있다. 이 과정은 아주 매끄럽게 진행된다.”

액텔은 독자적인 표준 ARM RealView 개발 키트를 제공하고 있다. 이 키트에는 C/C++ 컴파일러, 디버거, 링커, 명령어 세트 에뮬레이터, 임베디드 ICE(in-circuit emulator) 프로브가 포함돼 있다. “다른 프로세서를 사용해 왔고 C 코드가 있다면 액텔의 CoreConsole을 사용해 새로운 ARM7 기반 서브시스템을 쉽게 생성할 수 있다. 몇 시간 안에 프로세서 A용의 기존 코드를 ARM7 디바이스용 코드로 변환할 수 있다.” 타누한 수석 디렉터는 말했다.

이렇게 해서 나온 코드는 다른 ARM7 시스템에서와 똑같이 실행된다. 그는 “이 솔루션은 2가지 방식으로 호환성을 제공한다”며, “첫 번째는 사용자가 FPGA와 마이크로컨트롤러를 갖고 있고 프로세서를 FPGA에 내장하기로 결정한 경우 기존 소프트웨어를 변경하지 않고 사용할 수 있다는 점이며, 두 번째는 많은 ASIC 공급업체가 ARM7 코어를 제공하기 때문에 CoreMP7 디자인을 FPGA에서 ASIC로 신속히 옮길 수 있다는 점”이라고 말했다.

하드/소프트 프로세서 코어 혼합

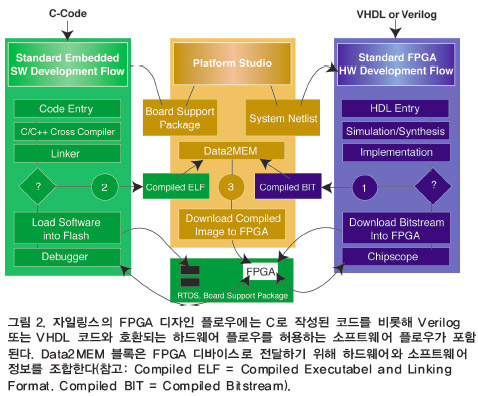

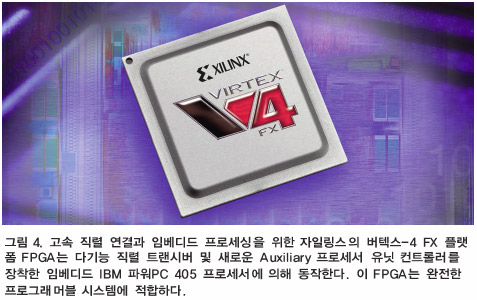

자일링스 FPGA로 작업하는 설계 엔지니어는 PicoBlaze(8비트) 또는 MicroBlaze(32비트) 소프트코어 프로세서를 선택하거나, 이 회사의 버텍스-4FX 및 버텍스-II 프로 FPGA에서 제공하는 업계 표준 32비트 파워PC 405 하드코어 프로세서를 선택할 수 있다.

자일링스 마케팅팀 제이 구드는 “종종 엔지니어들은 하나의 프로세서 코어로만 작업해야 하고 프로세서를 변경하면 다른 IP 라이브러리와 다른 개발 툴은 못쓰게 된다고 생각한다”고 지적했다. “자일링스의 FPGA 및 프로세서 코어에서는 미드레인지 MicroBlaze와 하이엔드 파워PC 프로세서 코어에 동일한 IP와 툴을 사용한다. 변경된 프로세서는 여전히 동일한 라이브러리와 툴을 사용하기 때문에, 설계팀이 이후에 다른 프로세서로 변경하더라도 기존 툴이나 과거의 설계 작업을 버릴 필요가 없다.”

그는 또 엔지니어가 파워PC 프로세서 코어를 제공하는 FPGA를 선택하면 이후에 MicroBlaze 프로세서 코어를 추가해 PowerPC가 담당하는 부하를 덜어줄 수 있다고 강조했다. 이러한 부하 분산(load balancing)은 유연성을 비롯해 많은 이점을 제공한다.

팔머는 “실시간 운영체제를 실행해야 하는 경우 엄격한 실시간 요구사항이 수반된다. 일부 경우에는 실시간 스레드를 FPGA의 여러 프로세서로 분할하는 방법이 더 쉽다”면서, “이 기술은 스레드를 격리 상태로 유지하기 때문에 다른 스레드를 방해하지 않으며, 따라서 우선 순위에 대한 RTOS를 결정할 필요가 없다”고 말했다.

For further reading

Maxfield, Clive,

“The Design Warrior’s Guide to FPGAs: Devices, Tools and Flows,” Newnes,

Burlington, MA. 2004. 542 pgs. Includes a CD-ROM. (Newnes is owned by the same

parent company as ECN magazine.) Yu, Helen, “Build and Optimize a MicroBlaze

Soft-Processor System Your Way,” Embedded Magazine, Xilinx, San Jose, CA.

September 2005, pp. 50--52.

출처

![]()