![]()

작성일: 2005.09.19

by 글: John Titus, ECN Magazine 수석 테크니컬 에디터

아직 FPGA(Field-Programmable Gate Array)를 도입하지 않은 설계가 있다면 아마도 곧 FPGA 기반 설계를 진행하게 될 것이다. 일부 엔지니어들은 많은 새로운 전자 제품들이 앞으로는 오직 메모리와 FPGA IC로만 동작하게 될 것이라고 믿는다(아날로그 회로는 외부와의 인터페이스의 역할을 한다). 이 생각에 따른다면 FPGA에 익숙하지 않은 엔지니어는 디지털 회로 설계 방식에 있어서 변화를 준비해야만 할 것이다.

Nallatech의 CTO인 Malachy Devlin의 말처럼, FPGA는 뛰어난 유연성 때문에 여타 디지털 회로에 비해 월등한 장점을 갖고 있다. 이와 같은 유연성은 다른 측면에서 본다면 FPGA의 가장 큰 단점이기도 하다고 그는 덧붙인다. "FPGA는 거의 모든 것을 할 수 있기 때문에 설계의 선택 폭이 상당히 넓다. 따라서 마이크로프로세서 기반 설계에서 엔지니어는 프로세서, 칩셋, 메모리 인터페이스 등에 대해 쉽게 타협할 수 있다"고 말했다. 즉, FPGA 설계는 점점 더 복잡해 진다. 예를 들면 엔지니어는 알고리즘과 메모리를 어떻게 구현해야 할지, I/O 포트를 어떻게 구성해야 할지 결정해야만 한다.

Devlin은 FPGA의 유연성에 대한 예를 들며 "동시에 여섯 개의 계수로 데이터를 처리해야 하는 알고리즘을 갖고 있다고 가정하자. 엔지니어는 FPGA를 여섯 개의 물리적 메모리 뱅크를 갖도록 해 여섯 번의 읽기 작업을 동시에 수행하도록 구성할 수 있다. 만일 더 긴 명령으로 동작하는 다른 알고리즘이 있다면 메모리를 세 개의 더블와이드 뱅크로 변환하면 된다. 이와 같은 유연성은 엔지니어가 다양한 알고리즘에 어떻게 FPGA의 메모리를 도입할 수 있는지 설명해 준다"고 설명했다. 하지만 FPGA를 공급 게이트나 간단한 함수로 생각하면 안 된다. 현재 FPGA는 메모리 구조, 프로세서, 특화된 I/O 컨트롤러까지 내장하고 있다.

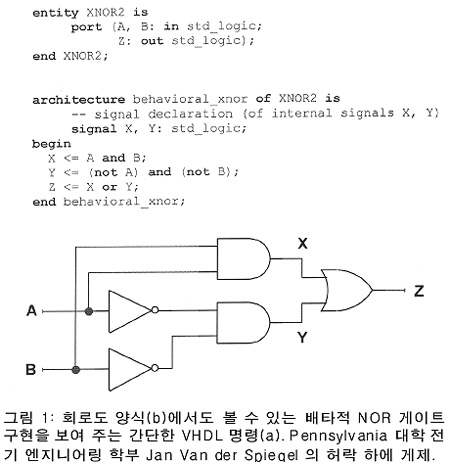

고맙게도 FPGA 회로를 설계하는 데 사용하는 툴 덕분에 엔지니어는 대부분의 세부 구현을 직접 하지 않아도 된다. 고수준 FPGA 설계 툴은 개별 기능에 대한 회로도 기호(schematic symbol)를 대신하기 위해 VHDL(그림 1) 및 Verilog 컴퓨터 언어를 사용하는 경우가 많다(이 기사의 온라인 버전에 있는 "FPGA Alphabet Soup" 참조). 하지만 처음 FPGA 회로를 만드는 디지털 디자이너라 해도 뭔가 새로운 것을 마스터할 필요는 없다.

Altium의 창업자이자 CEO인 Nick Martin은 "Verilog이나 VHDL 경험이 부족한 디지털 및 보드 수준 디자이너들의 이야기를 듣고 있다"며 "FPGA 회로를 설계하게 되면 이러한 경험이 부족한 엔지니어들은 이미 알고 있는 기술을 적용하려고 한다"고 말했다. 이 수요에 대응하기 위해 Altium은 엔지니어들이 FPGA에 "조립"만 하면 되는 블록 형태의 라이브러리를 공급하고 있다. 다른 FPGA 툴도 회로도를 사용해 설계할 수 있는 기능을 제공한다.

Martin은 "엔지니어는 Verilog이나 VHDL을 사용할 수도 있지만 필수는 아니다. 우리는 대신 회로도에 넣을 수 있는 마이크로프로세서 및 주변 장치와 같은 고수준 디바이스를 제공하고 있으며 엔지니어의 선택에 따라 코드를 작성할 수도 있다"고 설명했다. Altium 소프트웨어는 FPGA 판매 업체들이 제공하는 툴의 최상위에서 동작하기 때문에 엔지니어는 FPGA를 사용하기 위해 여러 업체들이 판매 중인 툴을 어떻게 운용해야 하는지 알 필요가 없다.

QuickLogic은 디자이너가 회로도에서 VHDL이나 Verilog 설계로 전환하는 것을 돕기 위해 상태 다이어그램으로 작업할 수 있는 설계 툴을 제공하고 있다. QuickLogic의 로직 제품 부문 수석 이사인 Brian Faith는 "이 툴이 생성하는 코드는 다른 QuickLogic 설계 소프트웨어에서 사용할 수 있다. 또한 이 툴을 사용하면 엔지니어는 결과 코드가 상태 기계(state-machine)와 어떻게 관계되어 있는지 확인할 수 있다. 비슷한 방식으로 엔지니어는 시뮬레이터가 설계의 입력에 적용하게 되는 디지털 파형을 그림으로써 '테스트 벤치'를 만들 수 있다"고 말했다.

QuickLogic QuickWorks 소프트웨어는 도움말 파일에 설계 흐름 설명서를 포함하고 있다. "회로도와 코드를 결합하는 혼성 모드 설계 흐름은 엔지니어가 VHDL이나 Verilog를 사용하기 쉽도록 해준다"고 Faith는 말했다. "예를 들어 설명서에는 Verilog에서 멀티플렉서를 코딩하거나 VHDL에서 간단한 상태 기계를 코딩하는 데 필요한 단계가 설명되어 있다. 따라서 엔지니어는 백지 상태에서 출발하지 않아도 되며 우리가 제공하는 코드를 받아서 수정함으로써 빠르게 시작할 수 있다."

VHDL이나 Verilog를 갓 배우기 시작한 엔지니어도 코드가 로직 소자 및 블럭에 어떻게 관계되는지 검사할 수 있다. Synplicity에서 FPGA 합성 부문 마케팅을 담당하고 있는 Jeff Garrison 이사는 "Synplify Pro 소프트웨어에 포함된 HDL Analyst는 VHDL이나 Verilog 코드를 읽고 이를 회로도로 변환한다"며 "엔지니어가 A+B=C 라는 함수를 코딩하면 가산기와 승산기 회로도가 생성된다. 함수를 클릭하면 해당 함수를 생성한 코드로 되돌아간다"고 설명했다. 그는 숙련된 엔지니어라 해도 의도대로 됐는지 확인하기 위해 그래픽 출력을 사용한다고 덧붙였다.

Altera의 소프트웨어 및 Nios 마케팅 이사인 Chris Balough는 "VHDL이나 Verilog를 잘 모르는 하드웨어 디자이너는 점점 찾기 어려워지고 있다. 우리가 만난 대부분의 로직 디자이너는 엔지니어링 교육 등을 통해 이들 언어에 대해 약간의 경험이나마 갖고 있었다. 일부는 아직 회로도로 설계하지만 이런 경우에도 회로도에 VHDL이나 Verilog 코드를 나타내는 기호가 포함된 경우가 많다"고 말했다. Balough는 FPGA 설계를 처음 시작하는 엔지니어라 해도 이러한 설계 언어를 접해 본 경험이 있을 것이라고 말했다.

Actel의 툴 마케팅 담당 이사인 Saloni Howard-Sarin은 "엔지니어가 Verilog나 VHDL에 익숙해져야만 하는 때가 올 것"이라며 "VHDL로 작업한 적이 없는 엔지니어라면 Actel이 진행하는 2일간의 VHDL 코딩 교육과 Libero 설계 툴을 사용한 3일간의 실습에 참여하는 방법이 있다"고 말했다.

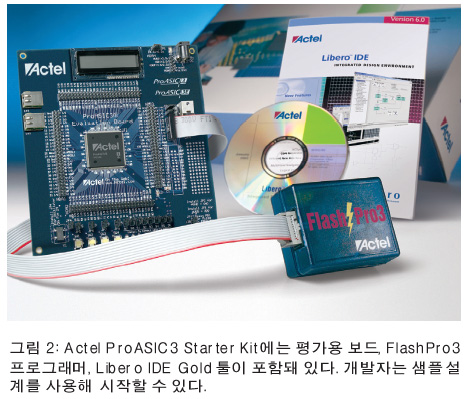

FPGA 공급업계와 툴 판매업계는 엔지니어들이 시작할 수 있도록 여러 형태의 I/O 디바이스가 포함되고 FPGA I/O 핀에 직접 액세스할 수 있는 다양한 개발 키트를 제공하고 있다(그림 2). 하지만 디자이너는 키트를 구매하기에 앞서 어떤 FPGA 제품군을 사용할 것인지 자세히 알아보고, 해당 제품군에서 소자를 시험해 볼 수 있는 키트를 구매해야 한다. 일반적으로 한 업체의 FPGA를 익힌 다음 최종 설계까지 붙잡고 있는 것이 좋다.

시작용 키트의 가격은 100달러 미만에서 수백 달러 수준이므로 비싸지 않은 가격에 FPGA 툴 및 디바이스에 대해 익힐 수 있다. 간단한 설명서를 통해 실제로 기능하는 FPGA 설계를 몇 시간이면 만들 수 있다. 키트에 포함된 툴은 설계의 크기와 툴로 작업할 수 있는 FPGA의 복잡성 측면에서 제한이 있다. 업체들은 자사 FPGA 툴의 키트 버전을 무료 소프트웨어로 엔지니어들이 받을 수 있도록 하는 경우가 많다.

키트를 사용하면 샘플 설계를 실행해 볼 수 있는 것 외에도 엔지니어는 개발 키트와 함께 레퍼런스 설계를 사용할 수 있다. Actel의 Howard-Sarin은 "레퍼런스 설계를 사용하는 추세가 강해지고 있는데, 이는 엔지니어들이 즉시 동작하는 것을 확인할 수 있기 때문"이라고 설명했다. FPGA 업체들은 웹 사이트에서도 레퍼런스 설계를 제공하고 있다.

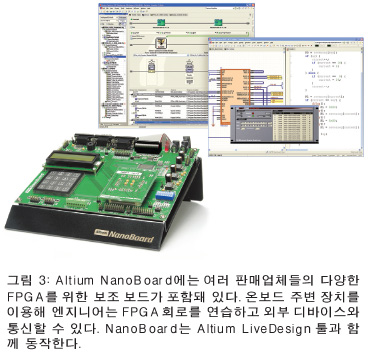

Altium의 NanoBoard 개발 시스템(그림 3)은 엔지니어에게 "디바이스 독립"을 제공한다. 15개의 보조 카드 덕분에 엔지니어는 Xilinx, Altera, Actel의 다양한 FPGA를 선택할 수 있다. 보조 보드를 바꾸면 다른 FPGA 군을 대상으로 작업할 수 있다. NanoBoard는 설계를 시험하기 쉽도록 LCD, LED, 스위치, 메모리 및 다양한 표준 주변 장치와 함께 제공된다. 시제품 또는 제품 단계로 이동해야 할 시점이 되면 Altium 툴의 구성 시스템은 업체의 디바이스로 매핑되는 FPGA-특화 파일을 생성한다. Martin은 "다양한 대상에 대해 다양한 구성을 할 수 있다"고 설명했다.

Altera의 Chris Balough는 ASIC 개발 경험이 있는 엔지니어는 FPGA 설계에서 뭔가 다른 점을 찾을 것이라고 말했다. "FPGA는 다른 방식으로 로직을 구현한다. FPGA는 조사(look-up) 테이블과 플립플롭의 매트릭스와 같으며, 바로 이 점이 툴 공급업체가 디바이스의 세부 사항으로부터 사용자를 분리시키는 이유다."

Synplicity의 Jeff Garrison은 특별한 설계 차이점을 제공한다. "ASIC 디자이너는 특정 메모리 구조를 실증 또는 증명할 수 있지만 우리는 FPGA 개발자에게 메모리를 포괄적으로 기술하도록 권장한다. 그러면 툴이 메모리 요구 사항을 추론할 수 있다. 이러한 접근 방식을 사용하면 툴이 성능과 사용 가능한 리소스에 기반해 이에 적합한 메모리 구현을 선택할 수 있다. 개발자는 상당한 수준의 이식성을 확보할 수 있다. 만일 A 업체의 RAM을 실증하면 A 업체의 FPGA 칩에 묶이기 쉽다.

ASIC를 개발하는 엔지니어는 또한 FPGA 설계가 하드웨어 설계보다는 소프트웨어 개발에 가깝다는 것을 알게 된다. "FPGA 디자이너는 데스크톱 PC 에 툴을 갖고 있기 때문에 작업 형태가 소프트웨어 프로그래머와 비슷하다"고 Actel의 Howard-Sarin은 말했다. 그는 "이들은 '시도해 보고 작동하는지 확인'하는 접근 방법을 사용한다. 작동하지 않으면 설계를 조정한다. FPGA를 접하는 ASIC 엔지니어는 '형식 검증(formal verification)'은 어떻게 해야 하지?'라는 의문을 갖지만 그냥 설계를 시도하기만 하면 된다"고 말했다(하지만 대규모 FPGA에는 일반적으로 형식 검증이 필요하다).

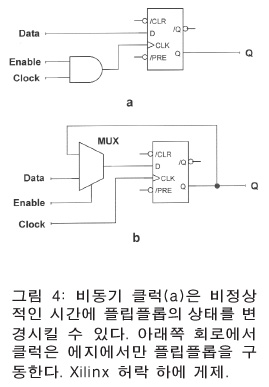

C/C++나 Java 배경 지식을 갖고 있는 엔지니어가 FPGA로 진출할 경우 타이밍에 대해 알아야 할 필요가 있다. Xilinx의 설계 팁에서는 FPGA 디자이너가 설계에 동기 회로를 사용하는 방법을 설명하고 있다. 첫 번째 회로(그림 4a)에서 동작 신호(enable signal)는 언제든 발생할 수 있기 때문에 이는 플립플롭의 클럭 신호에 결함을 일으킬 수 있다. 두 번째 회로(그림 4b)는 플립플롭을 직접 클러킹하며 동작 신호를 사용해 플립플롭의 D 입력을 선택한다. 클러킹은 클럭 엣지(clock edge)에서만 발생할 수 있다. 많은 설계 툴이 이런 형태의 동기 실행을 자동으로 처리하긴 하지만 디자이너는 FPGA의 타이밍 요구 사항을 이해하고 있어야 한다.

더 읽을 거리

Van der Spiegel, Jan, “VHDL Tutorial,” http://www.seas.upenn.edu/~ee201/vhdl/vhdl_primer.html

원본출처

![]() 한글판: http://www.ecnkoreamag.com/article.asp?id=1045

한글판: http://www.ecnkoreamag.com/article.asp?id=1045![]() 영문판: http://www.ecnasiamag.com/article.asp?id=3771

영문판: http://www.ecnasiamag.com/article.asp?id=3771

|

© 2005 Reed Business Information, a division of Reed Elsevier Inc. All rights reserved. Use of this web site is subject to its Terms and Conditions of Use. View our Privacy Policy. |

![]()