| Department of Electrical and Computer Engineering |                                  |  |  |  |  |  |  |

|---------------------------------------------------|----------------------------------|--|--|--|--|--|--|

| COEN 312                                          | Dec.4, 2008                      |  |  |  |  |  |  |

| Answer all Questions.                             | All questions carry equal marks. |  |  |  |  |  |  |

| Exam Duration 3 hour                              |                                  |  |  |  |  |  |  |

| No books or papers are allowed.                   | Examiner: Asim J. Al-Khalili     |  |  |  |  |  |  |

#### **Question** 1

Using **Boolean algebra**, minimize the following function:

a) F(A,B,C,D) = ABCD + (ABD)' + ABC'D

b) Given f(x,y,z) = xy + xz' + yzi) Implement f in <u>NOR-NOR</u> format ii) Implement f in <u>AND-OR-INVERT</u> format <u>Obtain optimum implementation.</u>

#### **Question 2**

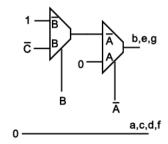

Design a combinational circuit decoder that examines a BCD digit and displays a letter "L" if the digit was less than or equal 5. Use the Display unit shown below. Implement the circuit using minimum 2\*1 MUXes.

$$\begin{bmatrix} b & \frac{a}{d} & c \\ c & \frac{d}{g} & f \\ \hline g & g \end{bmatrix}$$

## **Question 3**

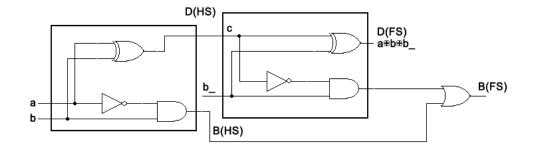

- a) Design a Half Subtractor.

- b) Design a Full Subtractor using two Half Subtractors.

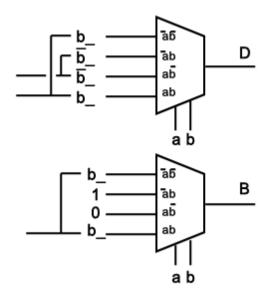

- c) Using two 4 \* 1 multiplexers implement the Full Subtractor

### **Question 4**

Design a BCD adder that adds two BCD digits and produces a sum digit in BCD. You may use 4-bit binary adders for your design. Give the circuit diagram.

### **Question 5**

Design a sequential circuit with two JK flip flops A & B and two inputs E & F. If E=0, the circuit remains in the same state regardless of the value of F. When E=1 and F=1, the circuit goes through the state transition from 00 to 01 to 10 to 11, back to 00 and repeats. When E=1 and F=0, the circuit goes through the state transitions from 00 to 11, to 10 to 01, back to 00 and repeats.

# **Question 6**

Analyze the circuit below fully. Derive the Transition Table, Excitation Table, State Diagram and the Output. Explain the function of the circuit.

# SOLUTION COEN312, DEC4 2008

Q1.

a. F(A,B,C,D) = ABCD+(ABD)'+ABC'D= ABD(C+C')+(ABD)'=ABD+(ABD)'=1

OR

=ABCD+(ABD)'+ABC'D =BCD+A'+B'+D'+BC'D =CD+A'+B'+D'+C'D =C+A'+B'+D'+C'D =A'+B'+D'+C+D =1

b.

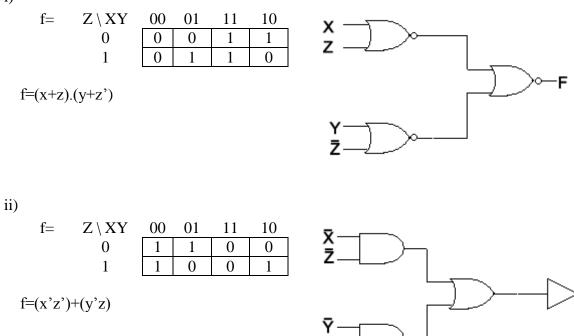

f(x,y,z) = xy+xz'+yz= xy(z+z')+xz'+yz= xyz+xyz'+xz'+yz= xz'+yz

i)

7

F

Q2.

|   | А | В | С | D | a | b | с | d | e | f | g |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 2 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 3 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 4 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 5 | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 6 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 7 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 8 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

Segments 'beg' has to be on in order to have 'L' on the seven-segments display.

a=c=d=f=0 b=e=g =A'B'+A'C' =A'(B'+C')

| f= | AB\CD | 00 | 01 | 11 | 10 |

|----|-------|----|----|----|----|

|    | 00    | 1  | 1  | 1  | 1  |

|    | 01    | 1  | 1  | 0  | 0  |

|    | 11    | Х  | Х  | Х  | Х  |

|    | 10    | 0  | 0  | 0  | Х  |

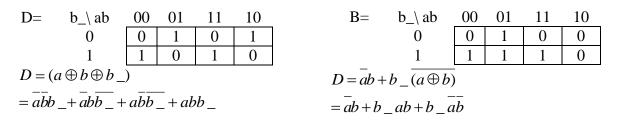

Q3.

|                             | For the half-subtractor, |   |   |   |  | For the full-subtractor, |   |   |    |   |   |  |

|-----------------------------|--------------------------|---|---|---|--|--------------------------|---|---|----|---|---|--|

| a.                          |                          |   |   |   |  | b.                       |   |   |    |   |   |  |

|                             | а                        | b | D | В |  |                          | a | b | B_ | D | В |  |

|                             | 0                        | 0 | 0 | 0 |  |                          | 0 | 0 | 0  | 0 | 0 |  |

|                             | 0                        | 1 | 1 | 1 |  |                          | 0 | 0 | 1  | 1 | 1 |  |

|                             | 1                        | 0 | 1 | 0 |  |                          | 0 | 1 | 0  | 1 | 1 |  |

|                             | 1                        | 1 | 0 | 0 |  |                          | 0 | 1 | 1  | 0 | 1 |  |

|                             |                          |   |   |   |  |                          | 1 | 0 | 0  | 1 | 0 |  |

|                             |                          |   |   |   |  |                          | 1 | 0 | 1  | 0 | 0 |  |

|                             |                          |   |   |   |  |                          | 1 | 1 | 0  | 0 | 0 |  |

|                             |                          |   |   |   |  |                          | 1 | 1 | 1  | 1 | 1 |  |

|                             |                          |   |   |   |  |                          |   |   |    |   |   |  |

| $D = (a \oplus b)$          |                          |   |   |   |  |                          |   |   |    |   |   |  |

| $D = (a \oplus b)$ $B = ab$ |                          |   |   |   |  |                          |   |   |    |   |   |  |

The K-map tables give:

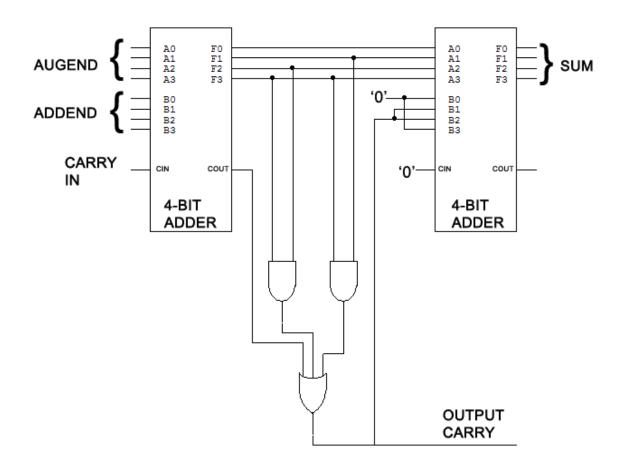

Q4.

The algorithm to do binary addition of two BCD numbers, with the result in BCD, involves a binary adder to do the actual arithmetic operation along with another adder to offset the result whenever the binary sum exceeds the BCD range, which is from 0 to 9. When this happens, the addition is scaled up by 6. The operation has to take care of the carry-out which will be asserted whenever the BCD range is exceeded or the actual binary addition generates a carry. The Boolean expression for the carry bit is:

$$C = K + Z_8 Z_4 + Z_8 Z_2$$

Q5.

State Diagram:

State Transition Table:

| Present | Next  |    |    |    |  |  |

|---------|-------|----|----|----|--|--|

| Y1 Y0   | EF 00 | 01 | 10 | 11 |  |  |

| 00      | 00    | 00 | 11 | 01 |  |  |

| 01      | 01    | 01 | 00 | 10 |  |  |

| 10      | 10    | 10 | 01 | 11 |  |  |

| 11      | 11    | 11 | 10 | 00 |  |  |

K-Maps for next state equations:

$Y_0^{+} = \overline{E}y_0 + E\overline{y}_0$

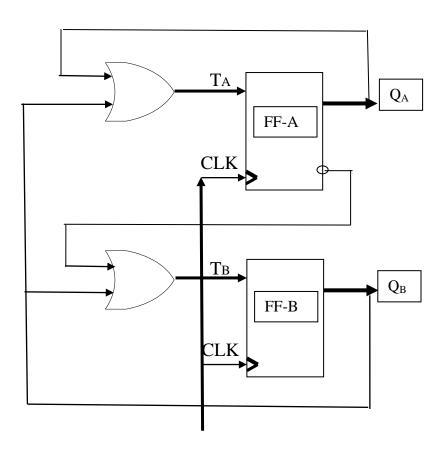

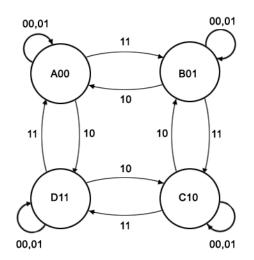

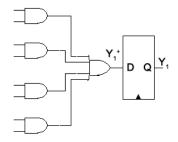

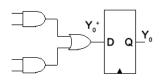

Q6.

Analysis:

$$T_A = Q_A + Q_B$$

$$T_B = \overline{Q}_A + Q_B$$

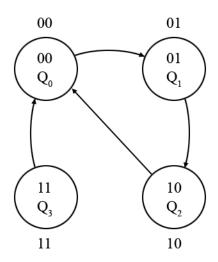

State transition table:

|    |                | CI             | LK             | NEXT STATE |         |  |

|----|----------------|----------------|----------------|------------|---------|--|

| QA | Q <sub>B</sub> | T <sub>A</sub> | T <sub>B</sub> | $Q_A^+$    | $Q_B^+$ |  |

| 0  | 0              | 0              | 1              | 0          | 1       |  |

| 0  | 1              | 1              | 1              | 1          | 0       |  |

| 1  | 0              | 1              | 0              | 0          | 0       |  |

| 1  | 1              | 1              | 1              | 0          | 0       |  |

State diagram:

Outputs are of the state itself.

This circuit is a counter "00"->"01"->"10" and back to "00"..., if ever started in "11" state, then the next state on the pulse will set state to "00", "01" and so on.