### Finite State Machine

## Outline

- 1. Overview

- 2. FSM representation

- 3. Timing and performance of an FSM

- 4. Moore machine versus Mealy machine

- 5. VHDL description of FSMs

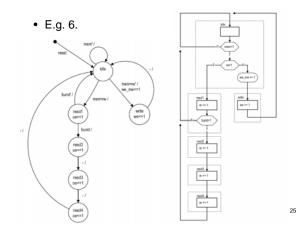

- 6. State assignment

- 7. Moore output buffering

- 8. FSM design examples

RTL Hardware Design by P. Chu

RTL Hardware Design by P. Chu

Chapter 10

### 1. Overview on FSM

- Contain "random" logic in next-state logic

- Used mainly used as a controller in a large system

- · Mealy vs Moore output

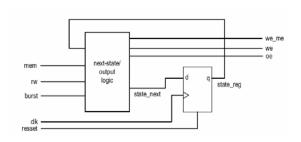

# • E.g.

a memory

controller

RTL Hardware Design by P. Chu

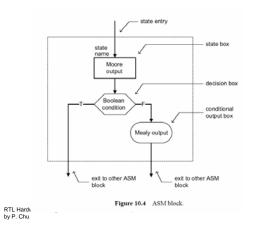

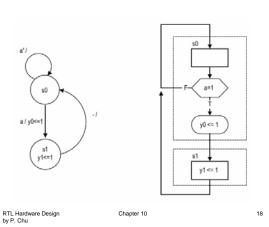

### 2. Representation of FSM

· State diagram

- ASM (algorithmic state machine) chart

- Flowchart-like diagram

- Provide the same info as an FSM

- More descriptive, better for complex description

- ASM block

- One state box

- One ore more optional decision boxes: with T or F exit path

- One or more conditional output boxes: for Mealy output

RTL Hardware Design Chapter 10 by P. Chu

1

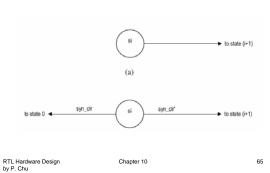

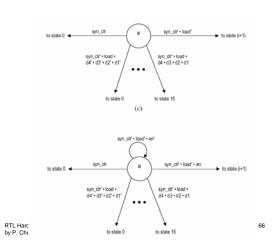

## State diagram and ASM chart conversion

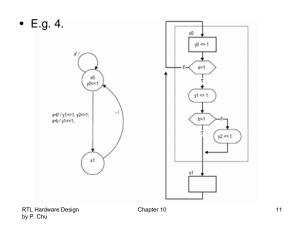

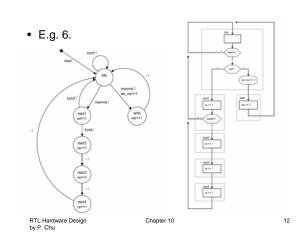

• E.g. 1.

• E.g. 3.

RTL Hardware Design by P. Chu

10

- Difference between a regular flowchart and ASM chart:

- Transition governed by clock

- Transition done between ASM blocks

- · Basic rules:

- For a given input combination, there is one unique exit path from the current ASM block

- The exit path of an ASM block must always lead to a state box. The state box can be the state box of the current ASM block or a state box of another ASM block.

RTL Hardware Design Chapter 10 1: by P. Chu

# RTL Hardware Des

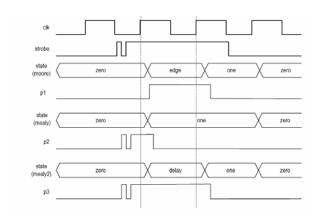

### • Sample timing diagram

### • Incorrect ASM charts:

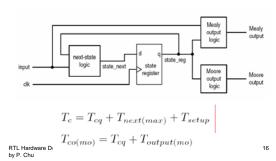

### 3. Performance of FSM

• Similar to regular sequential circuit

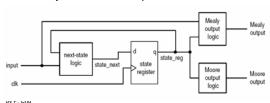

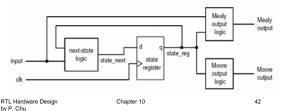

### 4. Moore vs Mealy output

- · Moore machine:

- output is a function of state

- Mealy machine:

- output function of state and output

- · From theoretical point of view

- Both machines have similar "computation capability"

Chapter 10

• Implication of FSM as a controller?

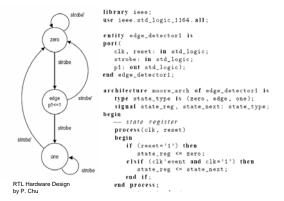

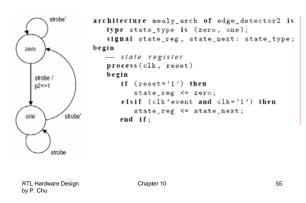

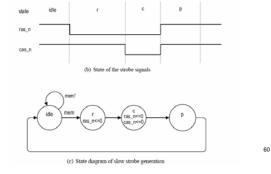

• E.g., edge detection circuit

A circuit to detect the rising edge of a slow "strobe" input and generate a "short" (about 1-clock period) output pulse.

RTL Hardware Design Chapter 10 20 by P. Chu

RTL Hardware Design by P. Chu

### • Three designs:

### Comparison

- Mealy machine uses fewer states

- Mealy machine responds faster

- Mealy machine may be transparent to glitches

- · Which one is better?

- · Types of control signal

- Edge sensitive

- E.g., enable signal of counter

- Both can be used but Mealy is faster

- Level sensitive

- E.g., write enable signal of SRAM

- Moore is preferred

RTL Hardware Design Chapter 10 23 by P. Chu

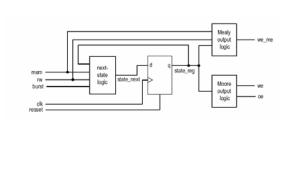

### VHDL Description of FSM

- Follow the basic block diagram

- Code the next-state/output logic according to the state diagram/ASM chart

- Use enumerate data type for states

RTL Hardware Design Chapter 10 24 by P. Chu

Chapter 10

26

RTL Hardware Design by P. Chu

```

library ieee;

use ieee.std_logic_1164.all;

entity mem_ctrl is

port (

clk, reset: in std_logic;

mem, rw, burst: in std_logic;

oe, we, we_me: out std_logic);

end mem_ctrl ;

architecture mult_seg_arch of mem_ctrl is

type mc_state_type is

(idle, read1, read2, read3, read4, write);

signal state_reg, state_next: mc_state_type;

-- state register

process(clk, reset)

begin

if (reset='1') then

state_reg <= idle;

elsif (clk'event and clk='1') then

state_reg <= state_next;

end if;</pre>

RTL Hardw

by P. Chu

end process;

```

```

-- next-state logic

process(state_reg, mem, rw, burst)

begin

case state_reg is

when idle =>

if mem = '1' then

if rw='1' then

state_next <= read1;</pre>

state_next <= write;

end if;

else

state_next <= idle;</pre>

end if;

when write =>

state_next <= idle;

```

when read1 => if (burst='1') then state\_next <= read2; state\_next <= idle; end if; when read2 => state\_next <= read3; when read3 => state\_next <= read4; when read4 => state\_next <= idle; end case; end process;

RTL Hardware Design by P. Chu Chapter 10

```

RTL Hardware Design by P. Chu

Chapter 10

29

```

```

-- moore output logic

process(state_reg)

begin

we <= '0'; -- default value

oe <= '0'; — default value

case state_reg is

when idle =>

when write =>

we <= '1';

when read1 =>

oe <= '1';

when read2 =>

oe <= '1';

when read3 =>

oe <= '1';

when read4 =>

oe <= '1';

end case;

end process;

RTL Hardware Design

by P. Chu

Chapter 10

```

30

```

-- mealy output logic

process(state_reg, mem, rw)

begin

we_me <= '0'; -- default value

case state_reg is

when idle =>

if (mem='1') and (rw='0') then

we_me <= '1';

end if;

when write =>

when read1 =>

when read2 =>

when read3 =>

when read3 =>

end case;

end process;

end mult_oeg_arch;

```

```

process ({\tt state\_reg} \;,\; {\tt mem} \;,\; {\tt rw} \;,\; {\tt burst})

begin

oe <= '0';

-- default values

we <= '0';

we_me <= ',0';

case state_reg is

when idle =>

if mem='1' then

if rw='1' then

state_next <= read1;

state_next <= write;

we_me <= '1';

end if;

else

state_next <= idle;

end if;

when write =>

state_next <= idle;

we <= '1';

RTL Hardware

by P. Chu

```

### • Combine next-state/output logic together

```

RTL Hardware Design Chapter 10 32 by P. Chu

```

```

when read1 =>

if (burst='1') then

state_next <= read2;

state_next <= idle;

end if;

oe <= '1';

when read2 =>

state_next <= read3;

oe <= '1';</pre>

when read3 =>

state_next <= read4;

when read4 =>

state_next <= idle;

oe <= '1';

end case;

end process;

Chapter 10

RTL Hardware Design by P. Chu

```

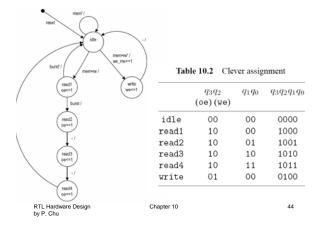

### 6. State assignment

- State assignment: assign binary representations to symbolic states

- In a synchronous FSM

- All assignments work

- Good assignment reduce the complexity of next-state/output logic

- · Typical assignment

- Binary, Gray, one-hot, almost one-hot

| RTL Hardware Design | Chapter 10 | 35 |

|---------------------|------------|----|

| by P. Chu           |            |    |

|       | Table                |                         |                       |                              |

|-------|----------------------|-------------------------|-----------------------|------------------------------|

|       | Binary<br>assignment | Gray code<br>assignment | One-hot<br>assignment | Almost one-hot<br>assignment |

| idle  | 000                  | 000                     | 000001                | 00000                        |

| read1 | 001                  | 001                     | 000010                | 00001                        |

| read2 | 010                  | 011                     | 000100                | 00010                        |

| read3 | 011                  | 010                     | 001000                | 00100                        |

| read4 | 100                  | 110                     | 010000                | 01000                        |

| write | 101                  | 111                     | 100000                | 10000                        |

RTL Hardware Design Chapter 10 36 by P. Chu

### State assignment in VHDL

• Implicit: use user attributes enum encoding

```

type mc_state_type is (idle,write,read1,read2,read3,read4);

attribute enum_encoding: string;

attribute enum_encoding of mc_state_type:

type is "0000 0100 1000 1001 1010 1011";

```

Explicit: use std\_logic\_vector for the register

```

RTL Hardware Design Chapter 10 37 by P. Chu

```

```

-- next-state logic

process(state_reg, mem, rw, burst)

begin

we_me <= '0';

case state_reg is

when idle =>

if mem='1' then

if rw='1' then

state_next <= read1;

state_next <= write

end if:

state_next <= idle;

end if;

state_next <= idle;

end case;

end process;

RTL Hardware Design by P. Chu

Chapter 10

```

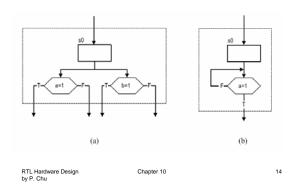

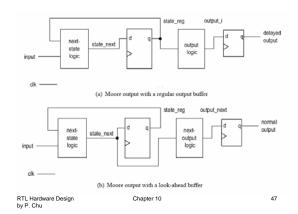

### 6. Moore output buffering

- · FSM as control circuit

- Sometimes fast, glitch-free signal is needed

- An extra output buffer can be added, but introduce one-clock delay

- Special schemes can be used for Moore output

- Clever state assignment

- Look-ahead output circuit

```

RTL Hardware Design Chapter 10 41 by P. Chu

```

### Handling the unused state

- · Many binary representations are not used

- What happens if the FSM enters an unused state?

- Ignore the condition

- Safe (Fault-tolerant) FSM: got to an error state or return to the initial state.

- Easy for the explicit state assignment

- No portable code for the enumerated data type

RTL Hardware Design Chapter 10 40 by P. Chu

- Potential problems of the Moore output logic:

- Potential hazards introduce glitches

- Increase the Tco delay (Tco = Tcq + Toutput)

- Can we get control signals directly from the register?

### Clever state assignment

- Assigning state according to output signal patterns

- Output can be obtained from register directly

- Extra register bits may be needed

- Must use explicit state assignment in VHDL code to access individual register bit

- · Difficult to revise and maintain

### • VHDL code

### Look-ahead output circuit

- · Output buffer introduces one-clock delay

- The "next" value of Moore output can be obtained by using state\_next signal

- Buffer the next value cancel out the one-clock delay

- More systematic and easier to revise and maintain

RTL Hardware Design Chapter 10 46 by P. Chu

- Modification over original VHDL code:

- Add output buffer

- Use state\_next to replace state\_reg in Moore output logic

```

-- output buffer

process(clk, reset)

begin

if (reset='1') then

oe_buf_reg <= '0';

we_buf_reg <= '0';

elsif (clk'event and clk='1') then

oe_buf_reg <= oe_next;

we_buf_reg <= we_next;

end if;

end process;

RTL Hardware Design Chapter 10 48

```

```

-- moore output logic

process(state_next)

begin

we_next <= '0'; -- default value

oe_next <= '0'; -- default value

case state_next is

when idle =>

when write =>

we_next <= '1';

when read1 =>

oe_next <= '1';

when read2 =>

oe_next <= '1';

when read3 =>

oe_next <= '1';

when read4 \Rightarrow

oe_next <= '1';

end case;

end process;

```

RTL Hardware Design Chapter 10 49 by P. Chu

### 7. FSM design examples

- Edge detector circuit

- Arbitrator (read)

- DRAM strobe signal generation

- Manchester encoding/decoding (read)

- FSM base binary counter

RTL Hardware Design Chapter 10 50 by P. Chu

### Edge detecting circuit (Moore)

### Use clever state assignment

|      | state_reg(1) (p1) | state_reg(0) |

|------|-------------------|--------------|

| zero | 0                 | 0            |

| edge | 1                 | 0            |

| one  | 0                 | 1            |

```

architecture clever_assign_buf_arch of edge_detector1 is constant zero: std_logic_vector(1 downto 0):= "00"; constant edge: std_logic_vector(1 downto 0):= "10"; constant one: std_logic_vector(1 downto 0):= "01"; signal state_reg_state_next: std_logic_vector(1 downto 0);

-- moore output logic

```

```

-- moore output togic

p1 <= state_reg(1);

RTL Hardware Design Chapter 10 53

by P. Chu

```

### Use look-ahead output

### Edge detecting circuit (Mealy)

```

-- next-state logic

process(state_reg, strobe)

begin

case state_reg is

when zero=>

if strobe= '1' then

state_next <= one;

clse

state_next <= zero;

end if;

when one =>

if strobe= '1' then

state_next <= one;

```

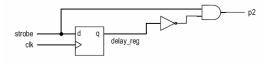

- Edge detecting circuit (direct implementation):

- edge occurs when previous value is 0 and new value is 1

- Same as Mealy design with state assignment: zero => 0, one => 1

Figure 10.19 Direct implementation of an edge detector.

RTL Hardware Design Chapter 10 58 by P. Chu

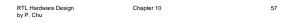

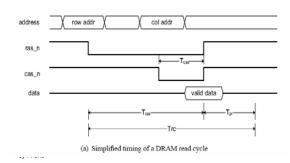

- DRAM strobe signal generation

- E.g.,120ns DRAM (Trc=120ns):Tras=85ns, Tcas=20ns, Tpr=35ns

- 3 intervals has to be at least 65ns, 20 ns, and 35 ns

- A slow design: use a 65ns clock period

195 ns (3\*65ns) read cycle

- · The control signal is level-sensitive

- -- output logic -- next-state logic process(state\_reg) process(state\_reg, mem) begin begin case state\_reg is

when idle =>

if mem='1' then

state\_next <= r;</pre> ras\_n <= '1'; case state\_reg is when idle => else when r =>state\_next <= idle; end if; ras\_n <= '0'; when c => when r =>

state\_next <=c;</pre> ras\_n <= '0'; cas\_n <= '0'; when c => state\_next <=p; when p => when p =>

state\_next <=idle;

end case;</pre> end case; end process; end fsm\_slow\_clk\_arch; end process;

- Should revise the code to obtain glitch-free output

RTL Hardware Design Chapter 10 62 by P. Chu

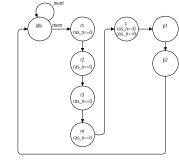

- A faster design: use a 20ns clock period

- 140 ns (7\*20ns) read cycle

RTL Hardware Design Chapter 10 by P. Chu

- FSM-based binary counter:

- Free-running mod-16 counter

RTL Hardware Design Chapter 10 64 by P. Chu

- 4-bit binary counter with features:

- Synchronous clear, load, enable