# 400 Mb/s/pin SLDRAM

### 4M x 18 SLDRAM

PIPELINED, EIGHT BANK, 2.5V OPERATION

#### **FEATURES**

- Very High Speed 400 MHz data rate

- 800 MB/s peak I/O Bandwidth provides very high bandwidth over narrow system memory bus

- Pipelined (Concurrent) Operation Up to 8 transactions (in one bank, or spread across multiple banks)

- Eight (this data sheet) or more internal banks for hiding row access/precharge

- · Programmable burst lengths of 4 or 8

- 100% peak bandwidth sustainable over random row as well as random column accesses, even with 8 byte bursts.

- Packet Oriented Protocol Provides pin compatibility across multiple densities

- Auto Refresh and Self Refresh

- Command Clock for commands and addresses;

Bidirectional Data Clocks for read and write data

- Dual Data Clocks provide smooth handoff from one data source to another

- Programmable Offset between Data and Data Clocks

- Programmable Read Delays Adjustable in coarse increments equal to one data bit time, and fine increments which are a fraction of a bit time; allows for specific temporal placement of data at the memory controller data pins

- Programmable Write Delays Adjustable in coarse increments equal to one data bit time. Allows for optimally adjusted write data temporal placement by the memory controller

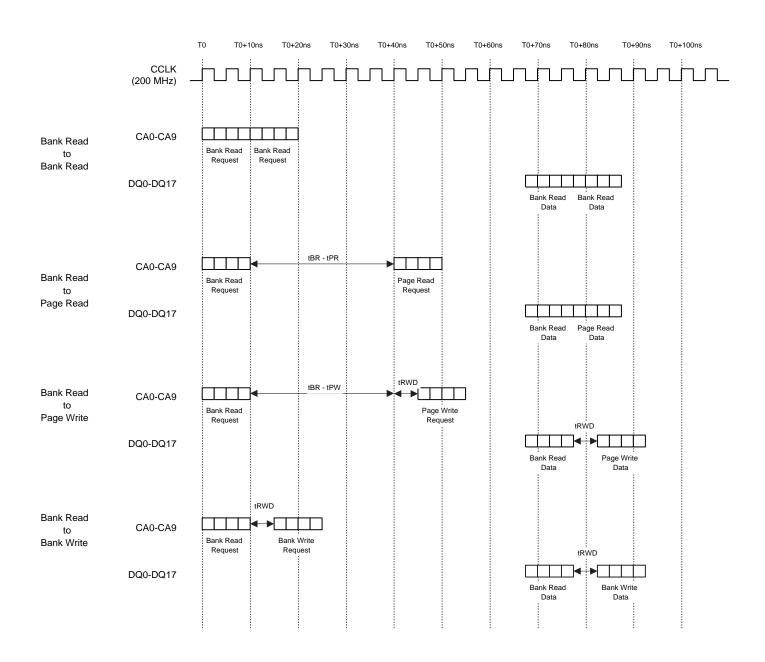

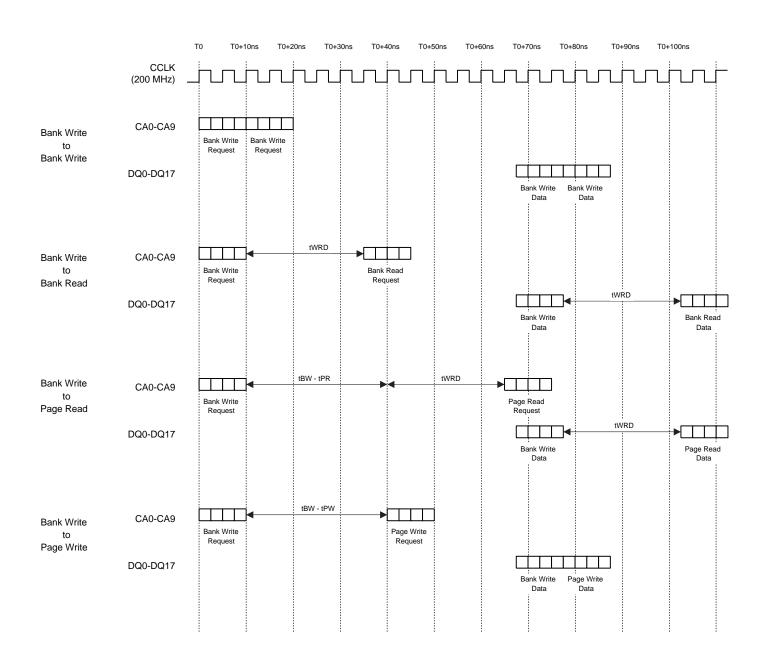

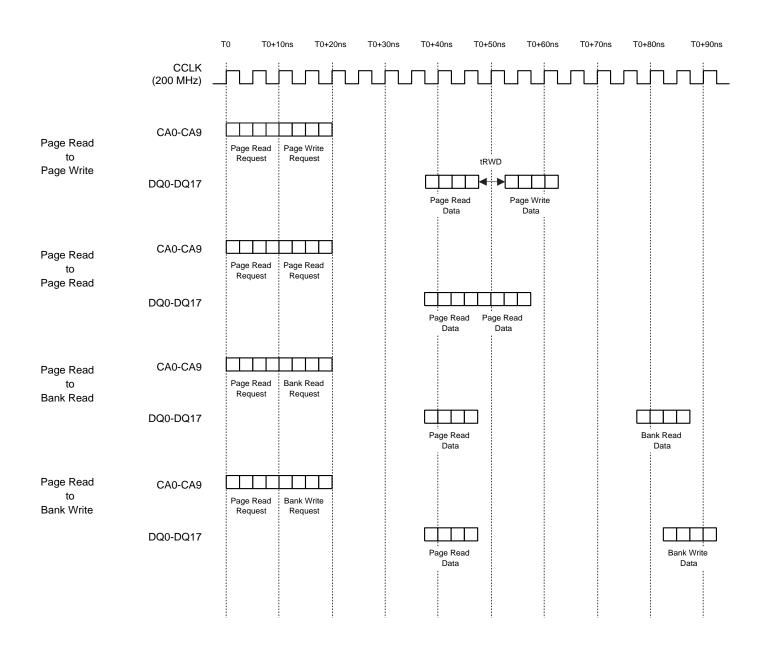

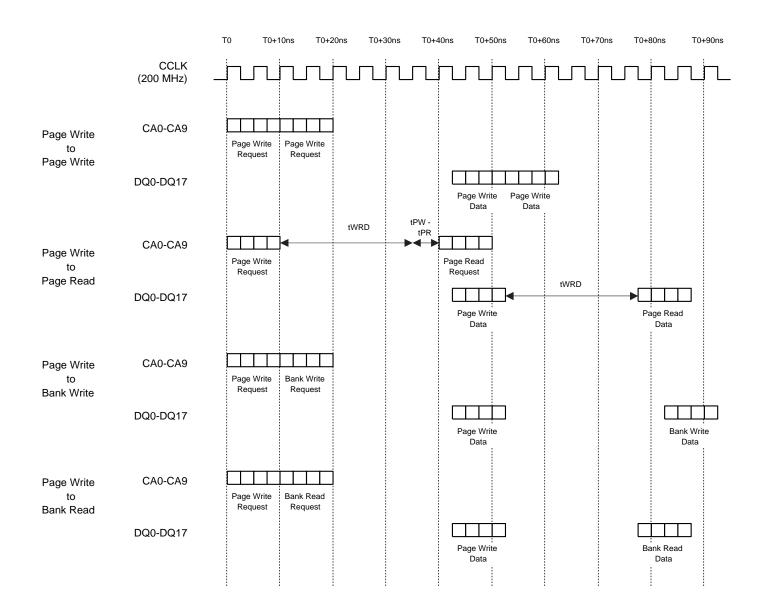

- Supports bank accesses (bank initially idle) and page accesses (bank active, row open)

- · 64ms, 8192-cycle refresh

- SLIO Interface Technology -Drivers : calibrated VOH and VOL levels, Receivers : narrow set-up and hold windows

- Single  $+2.5V \pm 5\%$  power supply

### **OPTIONS**

**MARKING**

• Timing 400 MHz data rate

- -400

- Plastic Package 64-pin VSMP (400mil width, .4/.8mm pitch) VS

- Part Number Example: SLD4M18DR400VS-400

### PIN ASSIGNMENT (TOP VIEW) 64-Pin VSMP

### **GENERAL DESCRIPTION**

The SLD4M18DR400 SLDRAM is a synchronous, very high-speed, packet-oriented, pipelined dynamic random access memory containing 75,497,472 bits. The SLD4M18DR400 SLDRAM is internally configured as eight banks of 128K x 72; each of the 128K x 72 banks is organized as 1024 rows by 128 columns by 72 bits. The 72 bits per column access are transferred over the I/O interface in a burst of four 18-bit words.

All transactions begin with a request packet. Read and write request packets contain the specific command and address information required. Read and write data are transferred in packets; a single-column access involves the transfer of a single data packet, which is a burst of four 18-bit words. Data from either one or two columns in a page may be accessed with a single request packet; the latter results in a continuous burst of eight 18-bit data words.

### **GENERAL DESCRIPTION (continued)**

Read or write requests may be issued to idle banks, or to the open row in active banks. Read or write requests indicate whether to leave the row open after the access, or to perform a self-timed precharge at the completion of the access (autoprecharge).

The SLD4M18DR400 uses a pipelined architecture and multiple internal banks to achieve high-speed operation and high effective bandwidth. Precharging one bank while accessing another bank will hide the precharge cycles, and provide seamless high-speed random access operation.

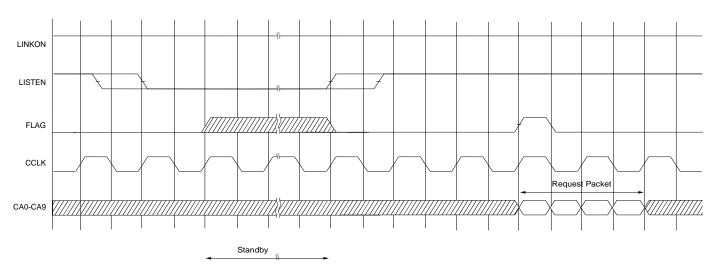

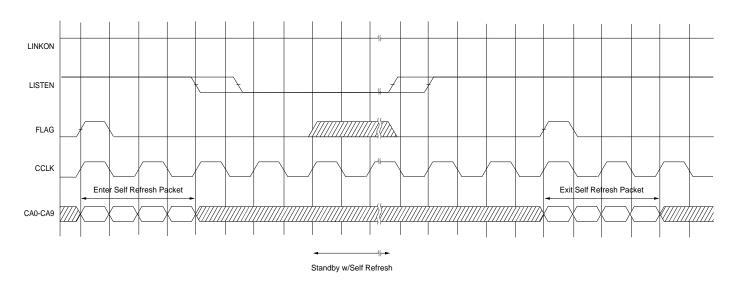

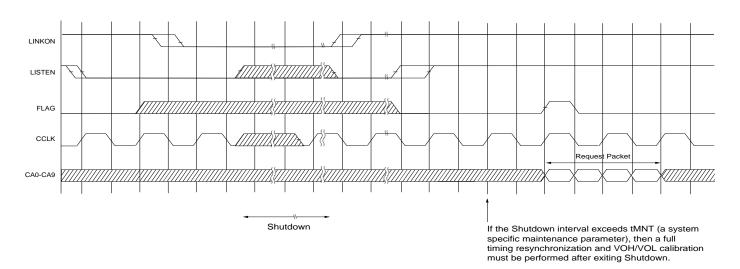

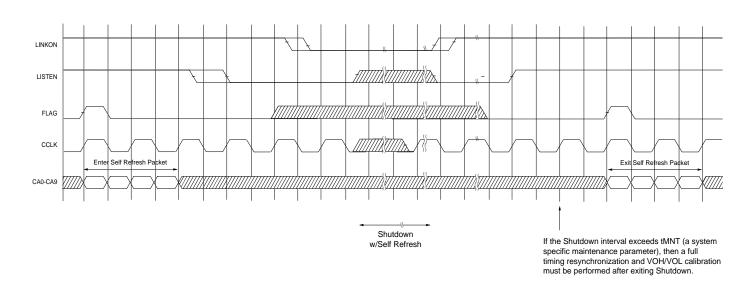

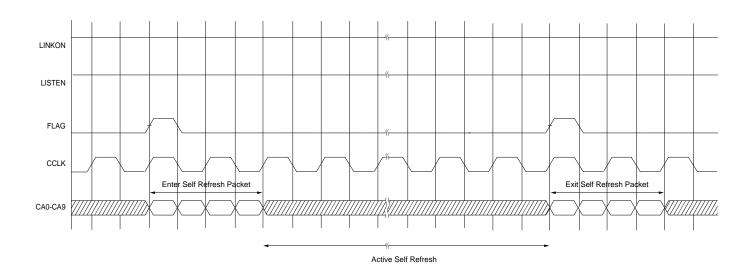

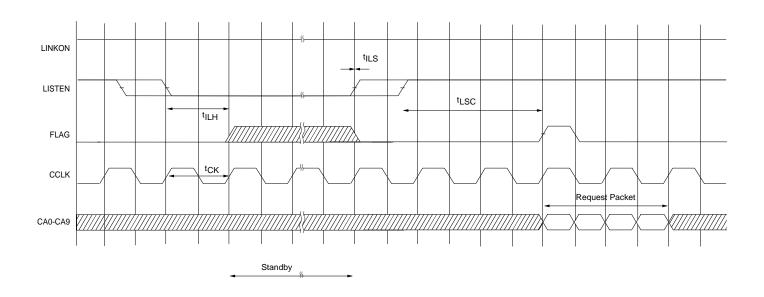

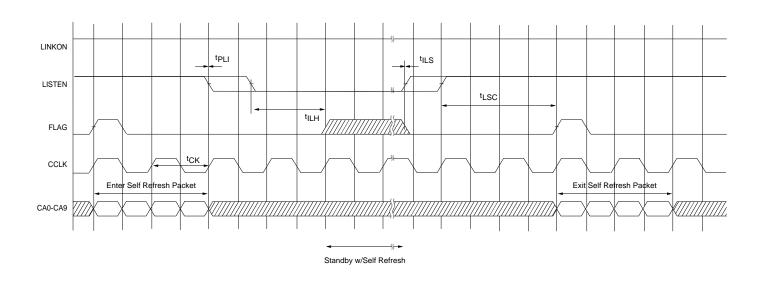

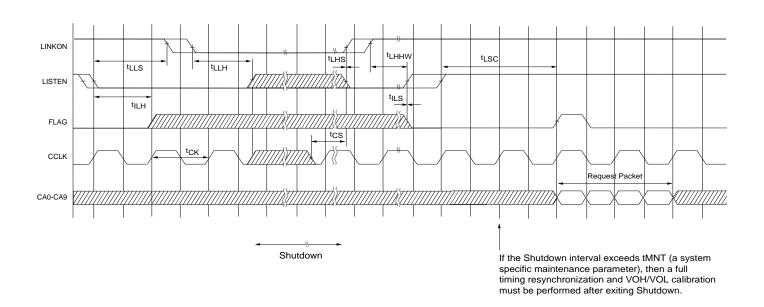

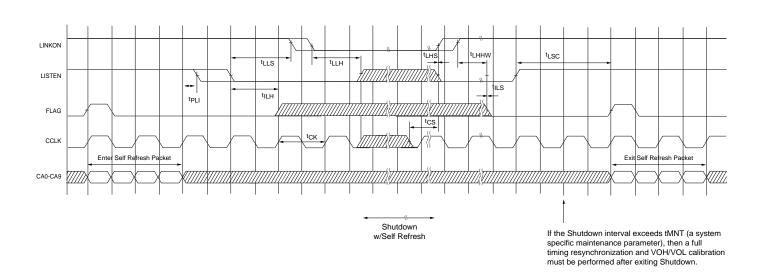

The SLD4M18DR400 is designed to operate in 2.5V memory systems. An auto-refresh mode is provided along with two power saving modes, standby and shutdown. Self-refresh is provided in the shutdown mode. The SLD4M18DR400 includes SLIO interface technology.

SLDRAMs offer substantial advances in DRAM operating performance, including the ability to synchronously burst data at a very high data rate with automatic column-

address generation, the ability to interleave between several internal banks in order to hide precharge time, and the capability to provide a continuous burst of data across random row and/or column locations, even with 8-byte granularity.

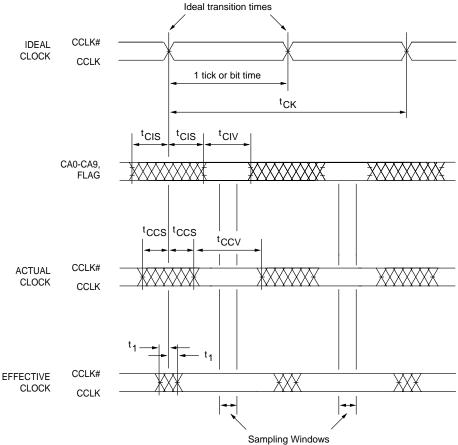

Terminology - the term "tick" is used throughout this data sheet as the equivalent of one-half of the CCLK clock period. Also, for simplicity, the clocks will be referred to and shown as CCLK, DCLK0 and DCLK1. It should be understood that these are differential clocks and that each has a complementary signal. Any reference to a specific edge of a particular clock refers to the true version of that clock (e.g. CCLK) not the complement (e.g. CCLK#).

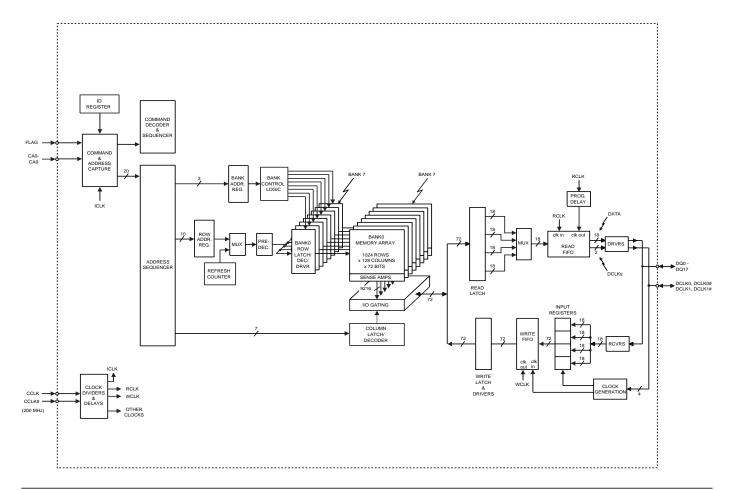

### **FUNCTIONAL BLOCK DIAGRAM**

### **PIN DESCRIPTIONS**

| VSMP<br>PIN NUMBERS                  | SYMBOL                                | TYPE                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|---------------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 29, 28                               | CCLK,<br>CCLK#                        | SLIO<br>Input              | Command Clock (differential): CCLK is driven by the memory controller (or a separate clock chip) coincident with the leading edges of the command bits. SLDRAM command input signals are effectively sampled at each crossing of internally delayed versions of CCLK/CCLK#. Read clocks, write clocks, and other internal clocks are derived from CCLK.                                                                                                                                               |

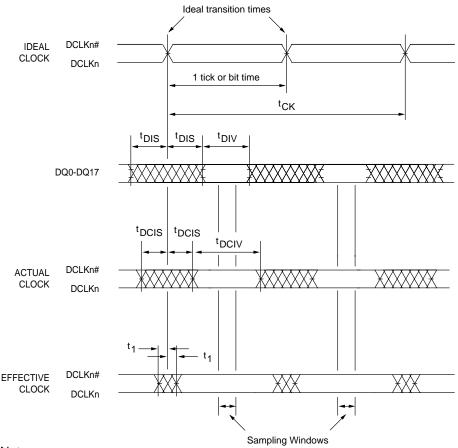

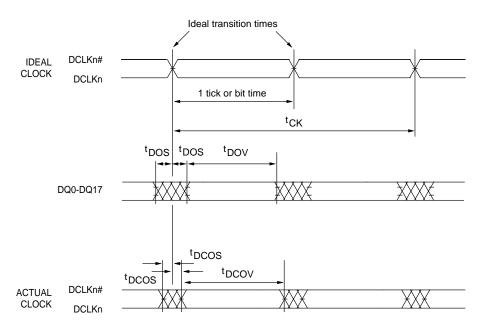

| 25, 24, 27, 26                       | DCLK0,<br>DCLK0#,<br>DCLK1,<br>DCLK1# | SLIO<br>Input/<br>Output   | Data Clocks (differential): For a read access, the specified pair of DCLK0/DCLK0# or DCLK1/DCLK1# is driven by the SLDRAM, and for write accesses, the specified pair is driven by the memory controller. During read accesses, the SLDRAM provides 2 crossings on the selected DCLK pair prior to, and then 1 crossing coincident with, the beginning of each valid data word. During write accesses, the SLDRAM uses a delayed version of the DCLK pair received with the data to capture the data. |

| 59, 60                               | SI, SO                                | LVCMOS<br>Input,<br>Output | Select In, Select Out: The controller and all SLDRAMs on a channel are connected in series using these pins. This connection is used to initialize the SLDRAMs.                                                                                                                                                                                                                                                                                                                                       |

| 6                                    | LINKON                                | LVCMOS<br>Input            | Link On: Used to enter and exit Shutdown mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7                                    | RESET#                                | LVCMOS<br>Input            | Reset#: Provides a hardware reset; resets all logic, including the ID register. Memory contents are not affected. An SLDRAM must be initialized following a hardware reset.                                                                                                                                                                                                                                                                                                                           |

| 8                                    | LISTEN                                | LVCMOS<br>Input            | Listen: Used to enter and exit Standby mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 42                                   | FLAG                                  | SLIO<br>Input              | Flag: FLAG HIGH indicates the start of a valid request packet; FLAG then goes LOW for the remainder of the packet. FLAG LOW at any other time is interpreted as a NOP.                                                                                                                                                                                                                                                                                                                                |

| 30-32, 35-41                         | CA0-CA9                               | SLIO<br>Input              | Command, Address: Commands, Addresses and/or Register Write Data are transferred on these signals, in packets of four words.                                                                                                                                                                                                                                                                                                                                                                          |

| 14-18, 21-23,<br>43-45, 48-53,<br>13 | DQ0-<br>DQ17                          | SLIO<br>Input/<br>Output   | Data I/O: Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5                                    | TEST                                  | _                          | Test Pin: Should be tied to Vss during normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 58                                   | Vref                                  |                            | Reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11, 19, 47, 55                       | VddQ                                  | Supply                     | DQ Power: Provide isolated power to DQs for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 12, 20, 46, 54                       | VssQ                                  | Supply                     | DQ Ground: Provide isolated ground to DQs for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1, 3, 9, 33,<br>57, 62, 64           | VDD                                   | Supply                     | Power Supply: +2.5V ± 5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2, 4, 10, 34,<br>56, 61, 63          | Vss                                   | Supply                     | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

### **FUNCTIONAL DESCRIPTION**

The specific SLDRAM described in this data sheet is an octal 128K x 72 DRAM which operates at 2.5V and includes a high speed, packet-oriented, synchronous 18-bit interface, and a pipelined architecture. Each of the 128K x 72 bit banks is organized as 1024 rows by 128 columns by 72 bits.

Read and write accesses begin with the application of a request packet which includes all necessary address bits. The request packet is followed, after a specific programmed delay, by a data packet, to complete the transaction.

Prior to normal operation, the SLDRAM must be initialized. The following sections provide detailed information covering device initialization, packet definition, command descriptions, register definition, and device operation.

### **Initialization**

#### POWER-UP/HARDWARE RESET

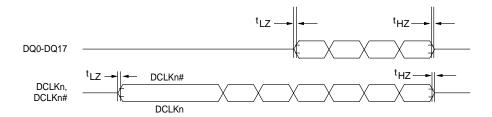

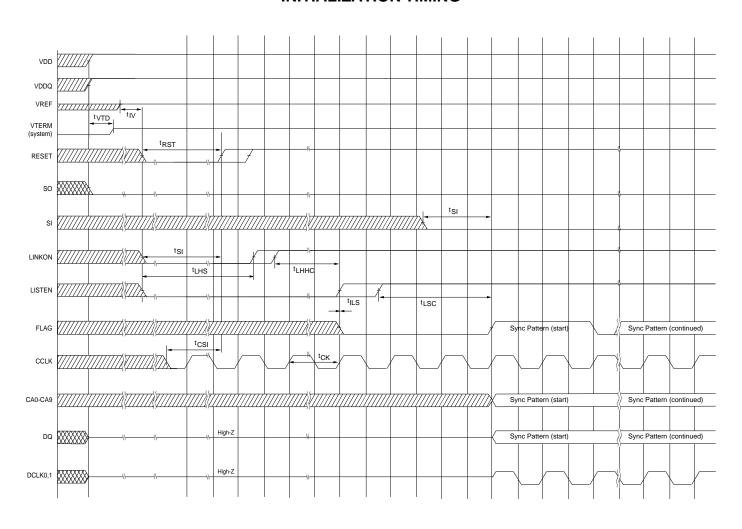

SLDRAMs must be powered-up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operation. Power must first be applied to VDD and VDDQ, then after a delay of tVTD, power must be applied to system VTERM. VTERM must be applied after VDDQ to avoid device latch-up, which may cause permanent damage to the device. VREF can be applied any time after VDDQ, but is expected to be nominally coincident with VTERM. Inputs are not recognized as valid until after VREF is applied. Upon power-up, the SLDRAM DQ and DCLK outputs will be High-Z and SO output will be driven LOW. The RESET# input should be held active for at least tRST. This hardware reset sets the internal ID Register to a value of 255, the SUB-ID Register to a value of 15, and sets programmable read and write delays to the minimum values.

#### EXIT SHUTDOWN/CONTROLLER DRIVER ADJUST

A LOW level on LINKON, and a stable CCLK, must be applied prior to deasserting RESET#; then after deasserting RESET#, continue the initialization sequence as if exiting the Shutdown mode (LISTEN LOW before LINKON HIGH, bring LINKON HIGH, wait tLHHC for DLLs to lock, then bring LISTEN HIGH). [Note: external buffer devices may require that LISTEN be LOW prior to deasserting RESET#, and that an additional lock delay must occur between LINKON going HIGH and LISTEN going HIGH]. After the exit Shutdown sequence, the device is active, and the command and write timing synchronization should be performed.

At some point prior to the start of command and write timing synchronization, the controller must perform a self-calibration of Voh and Vol on it's SLIO outputs and I/O pins.

### COMMAND AND WRITE TIMING SYNCHRONIZATION

For command and write timing synchronization, the controller transmits the specified pattern on the FLAG, CA, DQ and DCLK signals, repetitively, until a LOW-to-HIGH transition is eventually detected on it's SI input (which occurs only after all devices on the channel are successfully synchronized). The controller brings it's SO output HIGH after transmitting the first cycle of the specified pattern. The packets are broadcast to all devices connected directly to the controller and are identified by a two-tick HIGH level on the FLAG input. During this operation, the SLDRAM devices use the SI/SO daisy-chain link to communicate to the controller that command and write timing synchronization has been completed. This is achieved by passing a LOW-to-HIGH transition from the controller SO output to the first SLDRAM SI input, and then from the first SLDRAM SO output to the second SLDRAM SI input, etc. through the last SLDRAM SO output driving SI input of the controller. Each SLDRAM device begins command and write timing synchronization upon detecting the specified pattern but does not drive it's SO output until both the transition at it's SI input, and the completion of command and write timing synchronization have occurred.

The receipt of the special pattern on FLAG prior to the LOW-to-HIGH transition on SI differentiates this activity on the SI/SO link from the similar procedure used during ID assignment. The controller stops sending the specified patterns after detecting SI HIGH, and then waits 16 ticks before sending a valid command or resetting the SI/SO link (the FLAG signal should be LOW for 16 ticks). This delay allows the SLDRAM devices to detect the absence of the special pattern on the FLAG input and to recognize the next HIGH level on the FLAG input as being the start of a valid command packet. The controller resets the SI/SO link by bringing it's SO LOW and waiting for it's SI to go LOW; HIGH-to-LOW transitions propagate through the link independent of device status or operation.

Although this data sheet describes a 400 Mb/s/p device, it is noted for future designs that faster devices up through 800 Mb/s/p will include the capability to synchronize at the 400 Mb/s/p rate.

### **ID ASSIGNMENT**

Next, each SLDRAM on the channel(s) is sequentially assigned a unique ID and SUB-ID combination. Each SLDRAM is individually selected in turn by using the SI/SO link. This mode of operation is identified by a LOW-to-HIGH transition on SI followed by an ID Register Write Request Packet. Each ID Register Write Request will be followed by a corresponding SUB-ID Register Write Re-

quest Packet, and n of these request pairs will be issued, (where n equals the number of SLDRAM devices in the system). Only the SLDRAM which has SI HIGH, ID = 255 and SUB-ID = 15 will react to any given request pair. The selected SLDRAM reacts by writing the ID contained in the first packet to it's internal ID Register, writing the SUB-ID contained in the second packet to it's internal SUB-ID Register, and then driving it's SO HIGH. The controller provides enough delay (tID plus related maximum routing delays) between the assertion of it's SO output HIGH and the first issued request pair (and between subsequent issued request pairs) to allow for SO to propagate to the SI of the next device. ID assignment is complete when SI of the controller goes HIGH. Then the controller again resets the SI/SO link, as before.

### PRE-CONFIGURATION/SLDRAM DRIVER ADJUST

At this point the SLDRAMs can receive commands, and each SLDRAM is uniquely addressable. Next, the SLDRAM operating frequency should be programmed, and then Voh and Vol calibration should be performed. The information indicating the appropriate operating frequency will either be contained in the controller itself, or can be obtained by the controller by polling some other component (jumpers, Serial Presence Detect device, etc.). The appropriate values are then written to the respective registers of each SLDRAM. For programmed operating frequencies other than 200 MHz (400 Mb/s/p) the command and write synchronization would be repeated at this point for the new frequency.

Voh calibration is performed for each SLDRAM by sending a Drive DCLKs HIGH command and iteratively sending Increment/Decrement Voh commands and observing the output level until the desired level is achieved. Vol calibration is performed similarly using the Drive DCLKs LOW and Increment/Decrement Vol commands. The controller should then issue a Disable DCLKs command packet.

#### READ TIMING SYNCHRONIZATION

At this point the controller can send commands to individual SLDRAMs, and the operating frequency is selected, so read timing synchronization can be performed.

For each SLDRAM, the controller should send a Read Sync Request packet. The specified data pattern is returned by the SLDRAM, with a delay equal to the Actual Page Read Delay (which, after reset, equals the Minimum Page Read Delay, measured in integer clock ticks at the maximum rated frequency of the device). The actual delay from each SLDRAM module will be different, and the specific delays are unknown to the controller at this point. The controller should enable the data synchronization circuitry immediately after sending a Read Sync Request command.

The controller should then adjust internal timing to capture data. This is accomplished by adjusting the Fine Read and Data Offset Verniers until the known data pattern is captured and the capture timing is optimized. At this point, the controller should issue a Stop Read Sync Packet, which instructs the SLDRAM to discontinue sending the sync pattern. After this is done for each SLDRAM, the controller can read data from each SLDRAM at the minimum latency for that particular device.

Command and Write Timing Synchronization, Write Timing Synchronization, Read Timing Synchronization or output level calibration may be repeated periodically if necessary for a given system design and environment. Such re-synchronizations or re-calibrations should be performed when no accesses are in progress.

### DETECTING AND REPROGRAMMING READ AND WRITE LATENCIES

The controller may now detect the actual read latency in the system for each SLDRAM by sending a DRIVE DCLKs LOW command followed (after tDD) by a Read Status Register Request. The controller should enable data capture immediately after issuing the Read Status Register Request and should count clocks between sending the command and receiving the data. With the latency (including system delays) now known, the remaining status registers can be read as in normal operation (i.e. without first issuing the DRIVE DCLKs LOW command). Data from status registers is provided in a burst of 4 by the SLDRAM, at the Actual Read Latency of the device (which appears as the observed system latency at the controller).

After reading the status registers of all SLDRAMs, the controller uses the data provided, as well as the observed latencies, to determine the appropriate read latency to be programmed into the SLDRAMs.

In one suggested system design approach, the devices with shorter observed read latencies would be programmed with additional latency so as to match that of the SLDRAM(s) with the longest observed latency (for both bank and page accesses). This way, all read data arrives at the controller with the same latency from command to data, regardless of which SLDRAM device provides the data.

At this point the controller determines the optimum write latency corresponding to the above read latency at the controller I/O pins (optimizing the tradeoff of internal bus turnaround time and external bus turnaround time) and then must determine the corresponding write latency value for each SLDRAM (the write latency at a given SLDRAM may be different than that at the controller I/O pins, and may be different from that of other SLDRAMs). The controller must observe the system write latency for each SLDRAM compared to the corresponding programmed write latency for that device. This is accomplished by driving the DCLKs continually (toggling), issuing a Page Write to a specific address and sending a counting pattern on the DQs (start-

ing at the end of the write packet and continuing beyond the latency period, e.g. a count of 0-31 for  $400 \, \text{Mb/s/p}$ ). Reading back the value from the addressed location and comparing it with the value associated with the desired latency

provides the delta to be used to reprogram the write latencies (for bank and page accesses) for a given SLDRAM.

Once the IDs have been assigned and the timing adjusted for each SLDRAM, the channel is ready for normal operation

Figure 1

Command and Data Sync Patterns

| SIGNAL | REPEATING PATTERN |

|--------|-------------------|

| Flag   | 111101011001000   |

| CA9    | 000010100110111   |

| CA8    | 111101011001000   |

| CA7    | 000010100110111   |

| CA6    | 111101011001000   |

| CA5    | 000010100110111   |

| CA4    | 111101011001000   |

| CA3    | 000010100110111   |

| CA2    | 111101011001000   |

| CA1    | 000010100110111   |

| CA0    | 111101011001000   |

| DQ17   | 000010100110111   |

| DQ16   | 111101011001000   |

| DQ15   | 000010100110111   |

| DQ14   | 111101011001000   |

| DQ13   | 000010100110111   |

| DQ12   | 111101011001000   |

| DQ11   | 000010100110111   |

| DQ10   | 111101011001000   |

| DQ9    | 000010100110111   |

| DQ8    | 111101011001000   |

| DQ7    | 000010100110111   |

| DQ6    | 111101011001000   |

| DQ5    | 000010100110111   |

| DQ4    | 111101011001000   |

| DQ3    | 000010100110111   |

| DQ2    | 111101011001000   |

| DQ1    | 000010100110111   |

| DQ0    | 111101011001000   |

| DCLK1  | 1 0               |

| DCLK0  | 1 0               |

### **Packet Definition**

General definitions for the various packets included in the protocol are shown in the following figures. More specific definitions are included, when necessary, in the Regsister Definition, Command Description and Device Operation sections of this data sheet.

### READ, WRITE, OR ROW OP REQUEST PACKET

The Read, Write, or Row Op Request Packet is used to initiate any Read or Write Access, or to open or close a specific row in a specific bank.

A Read or Write request will result in the transfer of a Data Packet on the data bus at a specific time later. The Data Packet is driven by the SLDRAM for a READ, or by the memory controller for a Write. An Open Row or Close Row request generates no response.

Although unused address bits are not recognized by the SLDRAM device, zeroes should be applied for those bits, as shown.

### REGISTER READ REQUEST PACKET

The Register Read Request Packet is used to initiate a Read access to a register address. In response to a Register Read Request Packet, the SLDRAM will provide a Data Packet on the data bus at a specific time later.

Although bits REG6-REG4, and the last 18 bits of the packet are not needed or recognized by the SLDRAM, zeroes should be applied for those bits, as shown.

Figure 2

READ, WRITE, OR ROW OP REQUEST PACKET DEFINITION

| Flag | CA9  | CA8  | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |

|------|------|------|------|------|------|------|------|------|------|------|

| 0    | х    | Х    | х    | х    | х    | х    | х    | х    | х    | Х    |

| 1    | ID8  | ID7  | ID6  | ID5  | ID4  | ID3  | ID2  | ID1  | ID0  | CMD5 |

| 0    | CMD4 | CMD3 | CMD2 | CMD1 | CMD0 | BNK2 | BNK1 | BNK0 | ROW9 | ROW8 |

| 0    | ROW7 | ROW6 | ROW5 | ROW4 | ROW3 | ROW2 | ROW1 | ROW0 | 0    | 0    |

| 0    | 0    | 0    | 0    | COL6 | COL5 | COL4 | COL3 | COL2 | COL1 | COL0 |

ID8-ID0 = Device ID Value CMD5-CMD0 = Command Code BNK2-BNK0 = Bank Address

ROW9-ROW0 = Row Address COL6-COL0 = Column Address 0 = Unused, apply 0 for this bit

Figure 3

REGISTER READ PACKET DEFINITION

| Flag | CA9  | CA8  | CA7  | CA6  | CA5  | CA4    | CA3    | CA2    | CA1  | CA0  |

|------|------|------|------|------|------|--------|--------|--------|------|------|

| 0    | х    | х    | х    | х    | х    | х      | х      | х      | Х    | х    |

| 1    | ID8  | ID7  | ID6  | ID5  | ID4  | ID3    | ID2    | ID1    | ID0  | CMD5 |

| 0    | CMD4 | CMD3 | CMD2 | CMD1 | CMD0 | REG6=0 | REG5=0 | REG4=0 | REG3 | REG2 |

| 0    | REG1 | REG0 | 0    | 0    | 0    | 0      | 0      | 0      | 0    | 0    |

| 0    | 0    | 0    | 0    | 0    | 0    | 0      | 0      | 0      | 0    | 0    |

ID8-ID0 = Device ID Value CMD5-CMD0 = Command Code

REG6-REG0 = Register Address 0 = Unused, apply 0 for this bit

### REGISTER WRITE REQUEST PACKET

The Register Write Request Packet is used to initiate a Write access to a register address. This packet consists of four words, with the latter two being the data to be written to the selected register.

Although bits REG6-REG4 are not needed or recognized by the SLDRAM, zeroes should be applied for those bits, as shown.

#### **EVENT REQUEST PACKET**

The Event Request Packet is used to initiate a hard or soft reset, an Autorefresh, or a Close All Rows command, or to enter or exit Self Refresh, adjust output voltage levels, adjust the Fine Read Vernier or adjust the Data Offset Vernier.

The output voltage levels, or the fine read or data offset verniers can be adjusted using a dedicated Adjust Settings Event Request Packet or as part of an Autorefresh Event. In either case, the bits ADJ0-ADJ4 and DO0-DO4 determine the specific adjustment to be made, according to Truth Table 3. An autorefresh without adjustment is performed when ADJ0-ADJ4 are all 0.

The default values shown should be applied to the unused bits. For events other than Autorefresh or Adjust Settings, the ADJ0-ADJ4 bits are unused and zeroes should be applied to these bits. Note: bits DO0-DO4 are defined for future use, the default value for these bits is, and will be, all ones.

Figure 4

REGISTER WRITE PACKET DEFINITION

| Flag | CA9    | CA8    | CA7    | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |

|------|--------|--------|--------|------|------|------|------|------|------|------|

| 0    | х      | х      | х      | Х    | х    | х    | х    | х    | х    | х    |

| 1    | ID8    | ID7    | ID6    | ID5  | ID4  | ID3  | ID2  | ID1  | ID0  | CMD5 |

| 0    | CMD4   | CMD3   | CMD2   | CMD1 | CMD0 | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0    | REG6=0 | REG5=0 | REG4=0 | REG3 | REG2 | REG1 | REG0 | 0    | 0    | 0    |

| 0    | RD9    | RD8    | RD7    | RD6  | RD5  | RD4  | RD3  | RD2  | RD1  | RD0  |

ID8-ID0 = Device ID Value SID4-0 = Device Sub-ID Value RD9-RD0 = Register Data CMD5-CMD0 = Command Code REG6-REG0 = Register Address

### Figure 5 EVENT PACKET DEFINITION

| Flag | CA9   | CA8   | CA7   | CA6   | CA5   | CA4  | CA3  | CA2  | CA1  | CA0  |

|------|-------|-------|-------|-------|-------|------|------|------|------|------|

| 0    | х     | х     | х     | х     | х     | х    | х    | х    | х    | х    |

| 1    | ID8   | ID7   | ID6   | ID5   | ID4   | ID3  | ID2  | ID1  | ID0  | CMD5 |

| 0    | CMD4  | CMD3  | CMD2  | CMD1  | CMD0  | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0    | E6    | E5    | E4    | E3    | E2    | E1   | E0   | 0    | 0    | 0    |

| 0    | ADJ4* | ADJ3* | ADJ2* | ADJ1* | ADJ0* | DO4* | DO3* | DO2* | DO1* | DO0* |

<sup>\* =</sup> For Autorefresh and Adjust Settings events only, otherwise unused (ADJx = 0, DOx=1)

ID8-ID0 = Device ID Value SID4-0 = Device Sub-ID Value ADJ4-0 = Adjust Setting Code CMD5-CMD0 = Command Code E6-E0 = Event Index Code DO4-0 = Data Offset DQ Select (future use)

#### **DATA PACKET**

A Data Packet is provided by the controller for each Write Request, and by the SLDRAM for each Read Request. Each Data Packet contains either 8 bytes or 16 bytes, depending on whether the burst length was set to 4 or 8, respectively, in the corresponding request packet. There are no output

disable or write masking capabilities within the data packet.

When the burst length of 8 is selected, the first 8 bytes in the packet correspond to the column address contained in the request packet, and the second 8 bytes correspond to the same column address except with an inverted LSB (i.e. the burst 'wraps').

Figure 6

DATA PACKET DEFINITION (FOR BURST LENGTH = 4)

| DQ17 DQ16 DQ15 DQ14 DQ13 DQ12 DQ11 DQ10 DQ9 | DQ8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ6 |  |  |  |  |  |  |

|---------------------------------------------|-------------------------------------|--|--|--|--|--|--|

| Byte 0                                      | Byte 1                              |  |  |  |  |  |  |

| Byte 2                                      | Byte 3                              |  |  |  |  |  |  |

| Byte 4                                      | Byte 5                              |  |  |  |  |  |  |

| Byte 6                                      | Byte 7                              |  |  |  |  |  |  |

Figure 7

DATA PACKET DEFINITION (FOR BURST LENGTH = 8)

| DQ17 DQ16 DQ15 DQ14 DQ13 DQ12 DQ11 DQ10 DQ9 | DQ8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0 |

|---------------------------------------------|-------------------------------------|

| Byte 0                                      | Byte 1                              |

| Byte 2                                      | Byte 3                              |

| Byte 4                                      | Byte 5                              |

| Byte 6                                      | Byte 7                              |

| Byte 8                                      | Byte 9                              |

| Byte 10                                     | Byte 11                             |

| Byte 12                                     | Byte 13                             |

| Byte 14                                     | Byte 15                             |

### **Truth Table 1 - Commands**

| CMD5 | CMD4 | CMD3 | Command      | CMD2 | CMD1 | CMD0 | Subcommand                                                                         |

|------|------|------|--------------|------|------|------|------------------------------------------------------------------------------------|

| 0    | 0    | 0    |              | 0    | 0    | 0    | Read Access, Leave Row Open, Drive DCLK0                                           |

| 0    | 0    | 0    |              | 0    | 0    | 1 1  | Read Access, Leave Row Open, Drive DCLK1                                           |

| 0    | 0    | 0    |              | 0    | 1    | 0    | Read Access, Close Row, Drive DCLK0                                                |

| 0    | 0    | 0    | Page Access, | 0    | 1    | 1 1  | Read Access, Close Row, Drive DCLK1                                                |

| 0    | 0    | 0    | Burst of 4   | 1    | 0    | 0    | Write Access, Leave Row Open, Use DCLK0                                            |

| 0    | 0    | 0    | Barocori     | 1    | 0    | 1    | Write Access, Leave Row Open, Use DCLK1                                            |

| 0    | 0    | 0    |              | 1    | 1    | Ö    | Write Access, Close Row, Use DCLK0                                                 |

| 0    | 0    | 0    |              | 1    | 1    | 1 1  | Write Access, Close Row, Use DCLK1                                                 |

| 0    | 0    | 1    |              | 0    | 0    | Ö    | Read Access, Leave Row Open, Drive DCLK0                                           |

| 0    | 0    | 1    |              | 0    | 0    | 1    | Read Access, Leave Row Open, Drive DCLK1                                           |

| 0    | 0    | 1    |              | 0    | 1    | 0    | Read Access, Close Row, Drive DCLK0                                                |

| 0    | 0    | 1    | Page Access, | 0    | 1    | 1    | Read Access, Close Row, Drive DCLK1                                                |

| 0    | 0    | 1    | Burst of 8   | 1    | 0    | 0    | Write Access, Leave Row Open, Use DCLK0                                            |

| 0    | 0    | 1    | Daistoro     | 1    | 0    | 1    | Write Access, Leave Row Open, Use DCLK1                                            |

| 0    | 0    | 1    |              | 1    | 1    | 0    | Write Access, Close Row, Use DCLK1                                                 |

| 0    | 0    | 1    |              | 1    | 1 1  | 1    | Write Access, Close Row, Use DCLK0  Write Access, Close Row, Use DCLK1             |

| 0    | 1    | 0    |              | 0    | 0    | 0    | Read Access, Leave Row Open, Drive DCLK0                                           |

| 0    | 1    | 0    |              | 0    | 0    | 1    | Read Access, Leave Row Open, Drive DCLK0  Read Access, Leave Row Open, Drive DCLK1 |

| 0    | 1    | 0    |              | 0    | 1    | 0    | Read Access, Close Row, Drive DCLK0                                                |

| 0    | 1    | 0    | Bank Access, | 0    | 1 1  | 1    | Read Access, Close Row, Drive DCLR0                                                |

| 0    | 1    | 0    | Burst of 4   | 1    | 0    | 0    | Write Access, Leave Row Open, Use DCLK1                                            |

| 0    | 1    | 0    | Dui 5t 01 4  | 1    | 0    | 1    | Write Access, Leave Row Open, Use DCLK0                                            |

| 0    | 1    | 0    |              |      | 1    | 0    | Write Access, Close Row, Use DCLK1                                                 |

| 0    |      | 0    |              | 1    | 1 1  | -    |                                                                                    |

|      | 1    |      |              | 1    |      | 1    | Write Access, Close Row, Use DCLK1                                                 |

| 0    | 1    | 1    |              | 0    | 0    | 0    | Read Access, Leave Row Open, Drive DCLK0                                           |

| 0    | 1    | 1    |              | 0    | 0    | 1    | Read Access, Leave Row Open, Drive DCLK1 Read Access, Close Row, Drive DCLK0       |

| -    | 1    | 1    | DI- A        | 0    | 1    | 0    |                                                                                    |

| 0    | 1    | 1    | Bank Access, | 0    | 1    | 1    | Read Access, Close Row, Drive DCLK1                                                |

| 0    | 1    | 1    | Burst of 8   | 1    | 0    | 0    | Write Access, Leave Row Open, Use DCLK0                                            |

| 0    | 1    | 1    |              | 1    | 0    | 1    | Write Access, Leave Row Open, Use DCLK1                                            |

| 0    | 1    | 1    |              | 1    | 1    | 0    | Write Access, Close Row, Use DCLK0                                                 |

| 0    | 1    | 1    |              | 1    | 1    | 1    | Write Access, Close Row, Use DCLK1                                                 |

| 1    | 0    | 0    |              | 0    | 0    | 0    | Reserved                                                                           |

| 1    | 0    | 0    | <u> </u>     | 0    | 0    | 1    | Open Row                                                                           |

| 1    | 0    | 0    | Register     | 0    | 1    | 0    | Close Row                                                                          |

| 1    | 0    | 0    | Access,      | 0    | 1    | 1    | Register Write                                                                     |

| 1    | 0    | 0    | Row Op,      | 1    | 0    | 0    | Register Read, Use DCLK0                                                           |

| 1    | 0    | 0    | or Event     | 1    | 0    | 1    | Register Read, Use DCLK1                                                           |

| 1    | 0    | 0    |              | 1    | 1    | 0    | Reserved                                                                           |

| 1    | 0    | 0    |              | 1    | 1    | 1    | Event                                                                              |

| 1    | 0    | 1    |              | 0    | 0    | 0    | Read Sync (Drive both DCLKs)                                                       |

| 1    | 0    | 1    |              | 0    | 0    | 1    | Stop Read Sync                                                                     |

| 1    | 0    | 1    | _            | 0    | 1    | 0    | Drive DCLKs LOW                                                                    |

| 1    | 0    | 1    | Data         | 0    | 1    | 1    | Drive DCLKs HIGH                                                                   |

| 1    | 0    | 1    | Sync         | 1    | 0    | 0    | Write Sync (Both DCLKs toggling)                                                   |

| 1    | 0    | 1    |              | 1    | 0    | 1    | Reserved                                                                           |

| 1    | 0    | 1    |              | 1    | 1    | 0    | Disable DCLKs                                                                      |

| 1    | 0    | 1    |              | 1    | 1    | 1    | Drive DCLKs Toggling                                                               |

| 1    | 1    | 0    | Reserved     | Х    | Х    | Х    | Reserved                                                                           |

| 1    | 1    | 1    | Reserved     | Х    | Х    | Х    | Reserved                                                                           |

| *Index Range | Description                            |

|--------------|----------------------------------------|

| 0 - 15       | Defined Events - See Event Truth Table |

| 16 - 63      | Reserved                               |

| 64 - 127     | Vendor Dependent                       |

<sup>\*</sup> Index = value of E6-E0 in Event Request Packet

### Figure 8 Event Index Codes

### **Truth Table 2 - Events**

| E6-E3 | E2 | E1 | E0 | Event                                              |

|-------|----|----|----|----------------------------------------------------|

| 0     | 0  | 0  | 0  | Set ID Register to 255, SUB-ID to 15, reset device |

| 0     | 0  | 0  | 1  | Reset device, except ID and SUB-ID Registers       |

| 0     | 0  | 1  | 0  | Autorefresh                                        |

| 0     | 0  | 1  | 1  | Close all rows                                     |

| 0     | 1  | 0  | 0  | Enter Self Refresh                                 |

| 0     | 1  | 0  | 1  | Exit Self Refresh                                  |

| 0     | 1  | 1  | 0  | Adjust Settings                                    |

| 0     | 1  | 1  | 1  | Reserved                                           |

### **Truth Table 3 - Adjust Settings**

| ADJ4 | ADJ3 | ADJ2 | ADJ1 | ADJ0 | ADJUSTMENT                                                    |

|------|------|------|------|------|---------------------------------------------------------------|

| 0    | 0    | 0    | 0    | 0    | No Adjustment                                                 |

| 0    | 0    | 0    | 0    | 1    | Decrement Data Offset Vernier (delay DQs relative to DCLK0)   |

| 0    | 0    | 0    | 1    | 0    | Increment Data Offset Vernier (advance DQs relative to DCLK0) |

| 0    | 0    | 0    | 1    | 1    | Reset Data Offset Vernier to Zero                             |

| 0    | 0    | 1    | 0    | 0    | Reserved                                                      |

| 0    | 0    | 1    | 0    | 1    | Decrement Fine Read Vernier for DQs and DCLK0                 |

| 0    | 0    | 1    | 1    | 0    | Increment Fine Read Vernier for DQs and DCLK0                 |

| 0    | 0    | 1    | 1    | 1    | Reset Fine Read Vernier for DQs and DCLK0 to Zero             |

| 0    | 1    | 0    | 0    | 0    | Reserved                                                      |

| 0    | 1    | 0    | 0    | 1    | Decrement Fine Read Vernier for DCLK1                         |

| 0    | 1    | 0    | 1    | 0    | Increment Fine Read Vernier for DCLK1                         |

| 0    | 1    | 0    | 1    | 1    | Reset Fine Read Vernier for DCLK1 to Zero                     |

| 0    | 1    | 1    | 0    | 0    | Reserved                                                      |

| 0    | 1    | 1    | 0    | 1    | Decrement VOH Level                                           |

| 0    | 1    | 1    | 1    | 0    | Increment VOH Level                                           |

| 0    | 1    | 1    | 1    | 1    | Reset VOH to center of range                                  |

| 1    | 0    | 0    | 0    | 0    | Reserved                                                      |

| 1    | 0    | 0    | 0    | 1    | Decrement VOL Level                                           |

| 1    | 0    | 0    | 1    | 0    | Increment VOL Level                                           |

| 1    | 0    | 0    | 1    | 1    | Reset VOL to center of range                                  |

| 1    | 0    | 1    | 0    | 0    | Reserved                                                      |

| 1    | 0    | 1    | 0    | 1    | Reserved                                                      |

| 1    | 0    | 1    | 1    | 0    | Reserved                                                      |

| 1    | 0    | 1    | 1    | 1    | Reserved                                                      |

| 1    | 1    | 0    | 0    | 0    | Reserved                                                      |

| 1    | 1    | 0    | 0    | 1    | Reserved                                                      |

| 1    | 1    | 0    | 1    | 0    | Reserved                                                      |

| 1    | 1    | 0    | 1    | 1    | Reserved                                                      |

| 1    | 1    | 1    | 0    | 0    | Reserved                                                      |

| 1    | 1    | 1    | 0    | 1    | Reserved                                                      |

| 1    | 1    | 1    | 1    | 0    | Reserved                                                      |

| 1    | 1    | 1    | 1    | 1    | Reserved                                                      |

### **Command Descriptions**

Truth Table 1 provides a quick reference of available commands. Detailed descriptions are provided in the following sections. All command packets must start on a positive edge of CCLK (with CCLK in this context being specific, not generic).

#### **NO OPERATION (NOP)**

FLAG HIGH indicates the start of a valid request packet; FLAG then goes LOW for the remainder of the packet. FLAG LOW at any other time results in a NO OPERATION (NOP). A NOP prevents unwanted commands from being registered during idle states. NOPs do not affect operations already in progress.

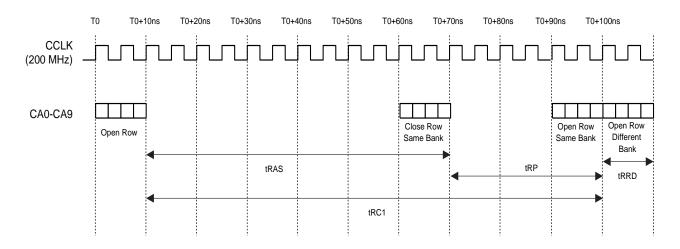

#### **OPEN ROW**

The OPEN ROW command is used to open (or activate) a row in a particular bank in preparation for a subsequent, but separate, column access command. The row remains open (or active) for accesses until a CLOSE ROW command or an access-and-close-row type command is issued to that bank. After an OPEN ROW command is issued to a given bank, a CLOSE ROW command or an access-and-close-row type command must be issued to that bank before a different row in that same bank can be opened.

The OPEN ROW command may be useful when a page access is anticipated, but the column address is not yet known, or when splitting a bank access into two components will facilitate scheduling.

#### **CLOSE ROW**

The CLOSE ROW command is used to close a row in a specific bank.

The CLOSE ROW command is used when it is desired to close a row that was previously left open in anticipation of subsequent page accesses.

#### **READ**

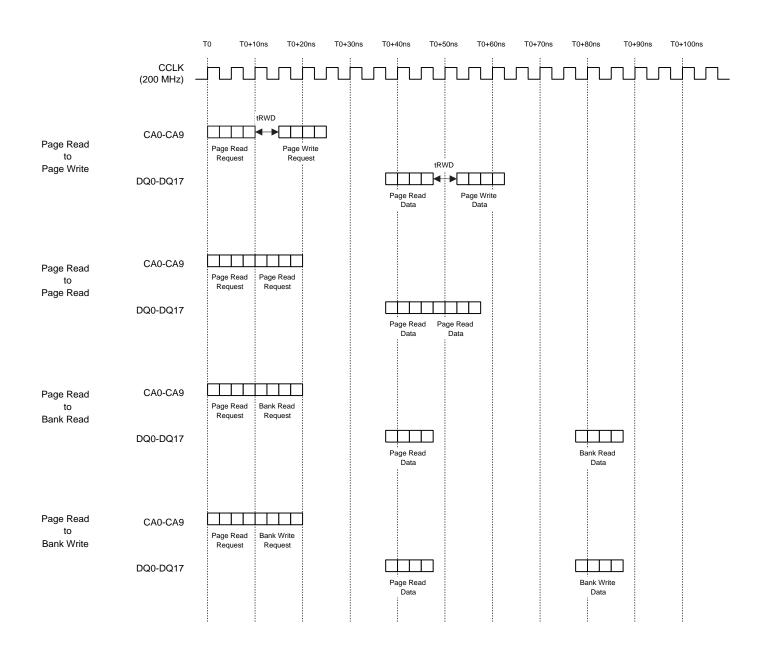

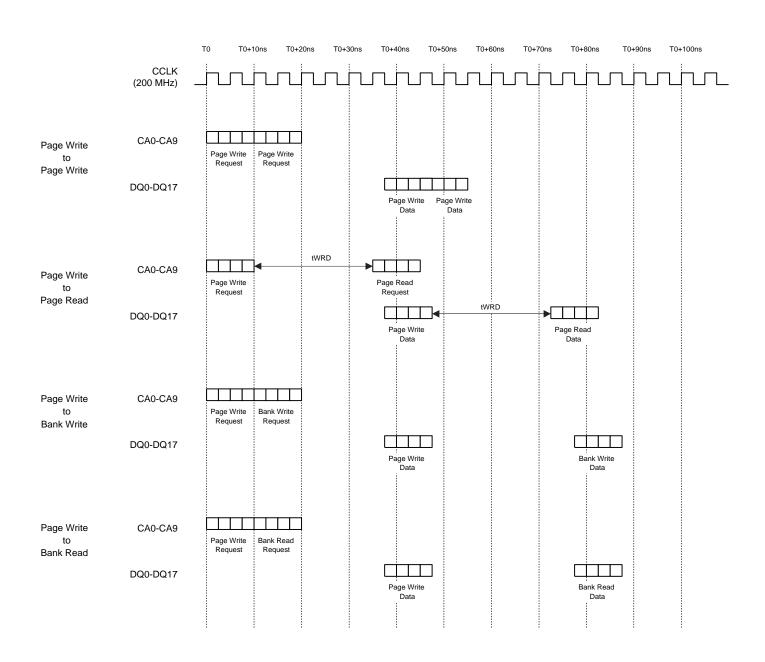

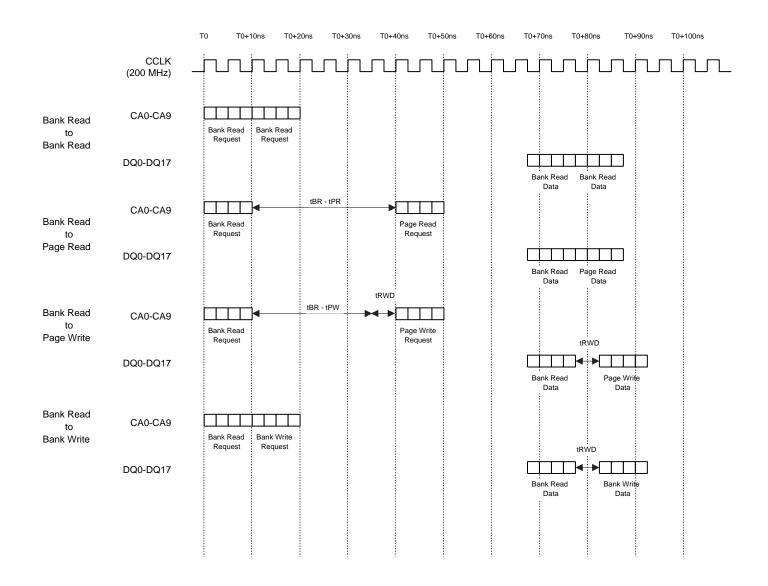

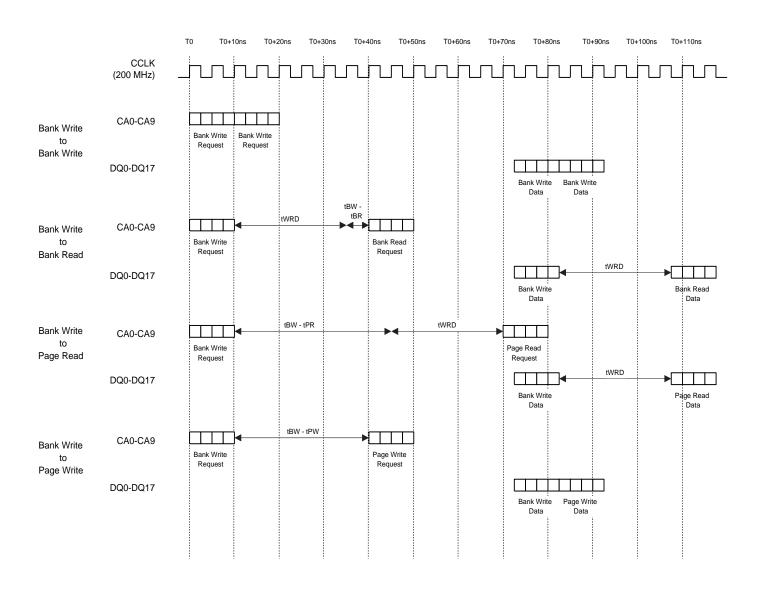

Page Read commands and Bank Read commands are used to initiate a read access to an open row, or to a closed row, respectively. The commands indicate the burst length, the selected DCLK, and whether to leave the row open after the access. Read data appears on the DQs subject to the corresponding Read Delay Register value and Read Data Vernier and Data Offset Vernier settings previously programmed into the device.

#### WRITE

Page Write commands and Bank Write commands are used to initiate a write access to an open row, or to a closed row, respectively. The commands indicate the burst length, the selected DCLK, and whether to leave the row open after

the access. Write data is expected on the DQs at a time determined by the corresponding Write Delay Register value previously programmed into the device.

#### **REGISTER READ**

Used to read the contents of the device status registers. The register data is available on the DQs after the delay determined by the Page Read Delay Register value and the Read Data Vernier and Data Offset Vernier settings previously programmed into the device.

#### REGISTER WRITE

Used to write to the control registers of the device. The register data is included within the request packet containing the command.

#### **EVENT**

Used to issue commands not requiring a specific address within a device or devices.

**Hard Reset** - Sets ID register to 255, SUB-ID register to 15, and resets device

Soft Reset - Resets device, except ID and SUB-ID registers

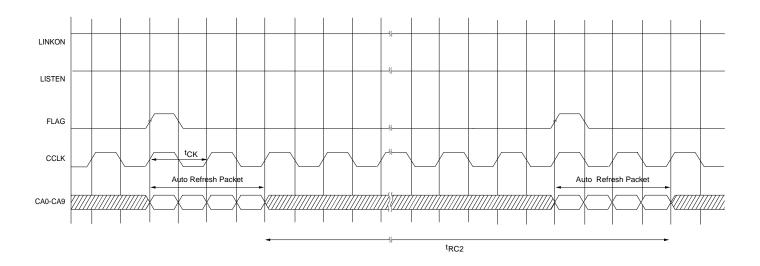

**Autorefresh** - Performs a refresh operation to the row or group of rows addressed by the internal refresh counter. All banks must be idle prior to performing an autorefresh event. The same adjustments that are possible with an Adjust Settings event may also be performed during an Autorefresh event

Close All Rows - Closes any open rows in any banks.

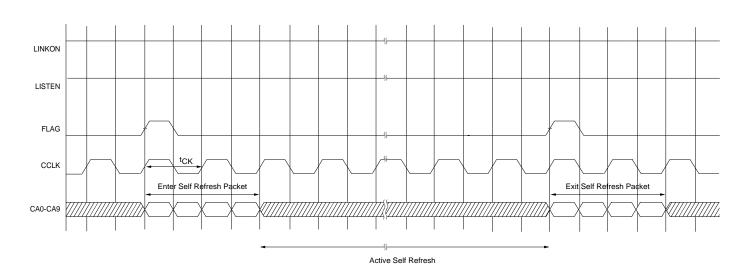

**Enter Self Refresh** - Causes the device to enter the Self Refresh mode of operation.

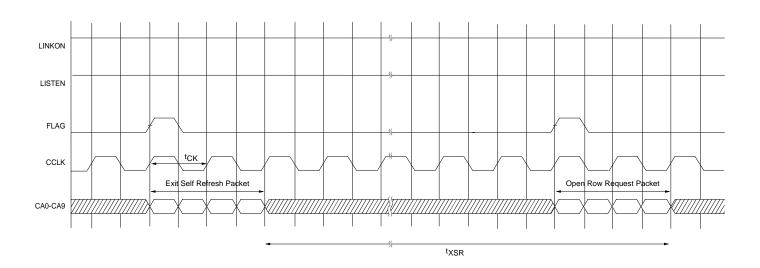

**Exit Self Refresh** - Causes the device to exit the Self Refresh mode of operation.

**Adjust Settings** - Used to adjust the Data Offset Vernier, Fine Read Verniers, VOH levels, and VOL levels.

#### READ SYNC (STOP READ SYNC)

Instructs the SLDRAM to start (stop) transmitting the specified synchronization pattern to be used by the controller to adjust input capture timing.

### **WRITE SYNC**

Instructs the SLDRAM to use the incoming data pattern to adjust input capture timing.

#### **DRIVE DCLKs LOW (HIGH)**

Instructs the SLDRAM to drive the DCLK outputs LOW (HIGH) until overridden by another DRIVE DCLK or READ command. DCLK is specific in this context; the DCLK# outputs will be in the opposite state.

#### **DRIVE DCLKs TOGGLING**

Instructs the SLDRAM to drive the DCLK outputs toggling at the operating frequency of the device (i.e. DCLKn and DCLKn#will cross every tCK/2 ns) until overridden by another DRIVE DCLK or READ command.

#### DISABLE DCLKs TOGGLING

Instructs the SLDRAM to disable (High-Z) the DCLK/DCLK# outputs until overridden by another DRIVE DCLK or READ command.

### **Register Definition**

The SLDRAM includes two sets of registers, the control registers and the status registers. The control registers are write-only registers which are logically 20-bits wide. Physically, all control registers are currently 8-bits or less, so the remaining bits are 'don't care' to the SLDRAM. However, to allow for future revision, the controller should write a 0 to each 'don't care' bit. Data to be written to a control register is provided via the Command/Address bus as part of the Register Write Packet.

The status registers are read-only registers which are logically 72-bits wide. Physically, all status registers are currently 32-bits, so the remaining bits are driven LOW during status register reads. Data being read from a status register is provided in a burst of 4, after a delay equal to the Actual Page Read Delay previously programmed into the device.

| REG3 | REG2 | REG1 | REG0 | CONTROL REGISTER    | STATUS REGISTER |

|------|------|------|------|---------------------|-----------------|

| 0    | 0    | 0    | 0    | ID                  | Configuration   |

| 0    | 0    | 0    | 1    | SUB-ID              | Actual Delays   |

| 0    | 0    | 1    | 0    | Operating Frequency | Minimum Delays  |

| 0    | 0    | 1    | 1    | Test                | Maximum Delays  |

| 0    | 1    | 0    | 0    | Page Read Delay     | Test            |

| 0    | 1    | 0    | 1    | Page Write Delay    | tRAS/tRP        |

| 0    | 1    | 1    | 0    | Bank Read Delay     | tRC1/tRC2       |

| 0    | 1    | 1    | 1    | Bank Write Delay    | tRCD/tXSR       |

| 1    | 0    | 0    | 0    | Reserved            | tWR/tWRD        |

| 1    | 0    | 0    | 1    | Reserved            | tPR/tBR         |

| 1    | 0    | 1    | 0    | Reserved            | tPW/tBW         |

| 1    | 0    | 1    | 1    | Reserved            | Reserved        |

| 1    | 1    | 0    | 0    | Reserved            | Reserved        |

| 1    | 1    | 0    | 1    | Reserved            | Reserved        |

| 1    | 1    | 1    | 0    | Reserved Reserved   |                 |

| 1    | 1    | 1    | 1    | Reserved            | Reserved        |

### Figure 9 REGISTER NAMES AND ADDRESSES

#### **CONTROL REGISTERS**

#### **ID Register**

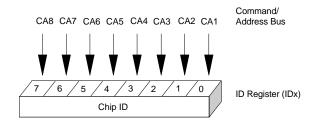

The ID Register consists of eight bits which are all set to 1 (= ID value 255) upon hardware reset, and are subsequently programmed to a unique value during initialization. Each SLDRAM monitors the Command/Address Bus for the start of a request packet, and then performs a comparison between the ID contained in the request packet and the one contained in it's internal ID Register. If there is a match within a given SLDRAM, this device will process the request packet. The 9th ID bit in the request packet allows for an SLDRAM to be accessed either individually or as part of a group (multicast). Broadcast Request Packets are recognized by all SLDRAMs, regardless of ID Register value. For Register Write and Event Request Packets, the SUB-ID value must also be a match, a multicast, or a broadcast to select a given SLDRAM.

The ID Register is programmed using the Write ID Register Request packet shown below.

### CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| 0 | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|---|

| 0 | 0   | 0   | 1   | 1   | 1   | 1   | 1   | 1   | 1 |

| 0 | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0 |

| 0 | ID7 | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | 0 |

## Figure 10 REGISTER WRITE REQUEST PACKET ID REGISTER

Note: ID8 is not stored in the SLDRAM

### Figure 11 ID REGISTER DEFINITION

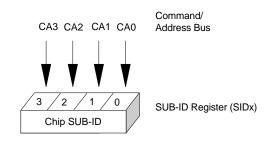

### **SUB-ID Register**

The SUB-ID Register consists of four bits which are all set to 1 (= ID value 15) upon hardware reset, and are subsequently programmed to a unique value (for a given ID value) during initialization. For Register Write and Event Requests, SLDRAMs with an ID that matches that in the request packet will perform a comparison between the SUB-ID also contained in the request packet and the one contained in it's internal SUB-ID Register. If there is a match within a given SLDRAM, this device will process the request packet. The 5th SUB-ID bit in the request packet allows for an SLDRAM to be accessed either individually or as part of a group (multicast). Such request packets will be recognized by all SLDRAMs with a matching ID if the 5th SUB-ID bit is 1 (regardless of SUB-ID register value), and by all SLDRAMs (regardless of ID and SUB-ID) if both the 9th ID bit and the 5th SUB-ID bit are 1.

The SUB-ID Register is programmed using the Write SUB-ID Register Request packet shown below.

### CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

|   | 0 | 1 | 1 | 1 | 1 | 1 | 1    | 1    | 1    | 1    |

|---|---|---|---|---|---|---|------|------|------|------|

|   | 0 | 0 | 0 | 1 | 1 | 1 | 1    | 1    | 1    | 1    |

|   | 0 | 0 | 0 | 0 | 0 | 0 | 1    | 0    | 0    | 0    |

| Ī | 0 | 0 | 0 | 0 | 0 | 0 | SID3 | SID2 | SID1 | SID0 |

## Figure 12 REGISTER WRITE REQUEST PACKET SUB-ID REGISTER

Note: SID4 is not stored in the SLDRAM

### Figure 13 SUB-ID REGISTER DEFINITION

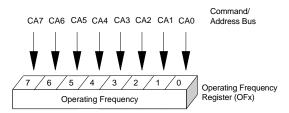

### **Operating Frequency Register**

Future SLDRAM devices will be capable of operating at more than one distinct clock frequency (e.g. 200, 300 or 400 MHz clock frequencies, resulting in 400, 600 or 800 Mb/s per pin data rate, respectively). The desired frequency, of those available, is selected via the Operating Frequency Register, as shown below. This is shown for future planning; for the devices covered by this data sheet, the value written to this register must be 0000000010 (bits 9-0, respectively).

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| ID8 | ID7 | ID6 | ID5 | ID4 | ID3  | ID2  | ID1  | ID0  | 1    |

|-----|-----|-----|-----|-----|------|------|------|------|------|

| 0   | 0   | 0   | 1   | 1   | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0   | 0   | 0   | 0   | 0   | 1    | 0    | 0    | 0    | 0    |

| 0   | 0   | OF7 | OF6 | OF5 | OF4  | OF3  | OF2  | OF1  | OF0  |

## Figure 14 REGISTER WRITE REQUEST PACKET OPERATING FREQUENCY REGISTER

Note: One, and only one, bit must be set to 1, and the corresponding operating frequency must be valid for a given device.

| OFx:            | Clock Frequency/     |

|-----------------|----------------------|

| 7 6 5 4 3 2 1 0 | (data rate per pin)  |

| 0 0 0 0 0 0 0 1 | 100 MHz/(200 Mb/s/p) |

| 0 0 0 0 0 0 1 0 | 200 MHz/(400 Mb/s/p) |

| 0 0 0 0 0 1 0 0 | 300 MHz/(600 Mb/s/p) |

| 0 0 0 0 1 0 0 0 | 400 MHz/(800 Mb/s/p) |

| 0 0 0 1 0 0 0 0 | 500 MHz/(1 Gb/s/p)   |

| 0 0 1 0 0 0 0 0 | 600 MHz/(1.2 Gb/s/p) |

| All others      | Reserved or Illegal  |

## Figure 15 OPERATING FREQUENCY REGISTER/ BIT DEFINITION

### **Test Register**

This register is for vendor specific device testing and should not be written to during normal device operation.

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

|   | ID8 | ID7 | ID6 | ID5 | ID4 | ID3  | ID2  | ID1  | ID0  | 1    |

|---|-----|-----|-----|-----|-----|------|------|------|------|------|

| Ī | 0   | 0   | 0   | 1   | 1   | SID4 | SID3 | SID2 | SID1 | SID0 |

|   | 0   | 0   | 0   | 0   | 0   | 1    | 1    | 0    | 0    | 0    |

| Ī | Т9  | T8  | T7  | T6  | T5  | T4   | Т3   | T2   | T1   | T0   |

### Figure 16 REGISTER WRITE REQUEST PACKET TEST REGISTER

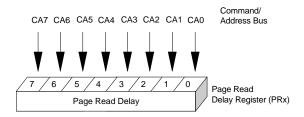

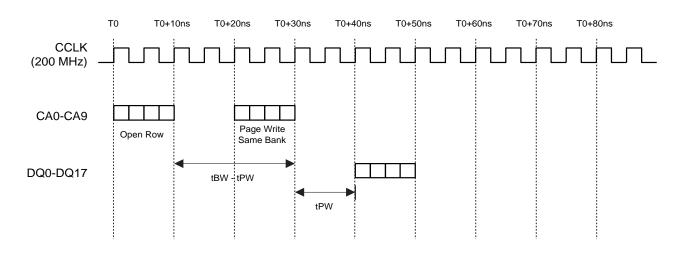

### Page Read Delay Register

The Page Read Delay Register is used to program the number of integer clock ticks (a.k.a. half cycles, or bit times) between receiving a Page Read Request Packet and providing the corresponding Read Data output. Although the 8-bit register can support a range of 0 to 255 clock ticks, the value programmed must be between the minimum and maximum values as provided in the respective status registers. Different values may be programmed in different SLDRAMs on the same channel in order to compensate for differences in internal SLDRAM and external routing delays.

The value written to this register may subsequently be modified by Increment/Decrement Fine Read Vernier events. Such modifications are reflected in the Actual Delays Status Register.

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| ID8 | ID7 | ID6 | ID5 | ID4 | ID3  | ID2  | ID1  | ID0  | 1    |

|-----|-----|-----|-----|-----|------|------|------|------|------|

| 0   | 0   | 0   | 1   | 1   | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0   | 0   | 0   | 0   | 1   | 0    | 0    | 0    | 0    | 0    |

| 0   | 0   | PR7 | PR6 | PR5 | PR4  | PR3  | PR2  | PR1  | PR0  |

## Figure 17 REGISTER WRITE REQUEST PACKET PAGE READ DELAY REGISTER

| PF | Rx: |   |   |   |   |   |   |                               |

|----|-----|---|---|---|---|---|---|-------------------------------|

| 7  | 6   | 5 | 4 | 3 | 2 | 1 | 0 | Integer Number of Clock Ticks |

| 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0                             |

|    |     |   |   |   |   |   |   | :                             |

| 1  | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 255                           |

## Figure 18 PAGE READ DELAY REGISTER/BIT DEFINITION

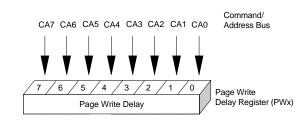

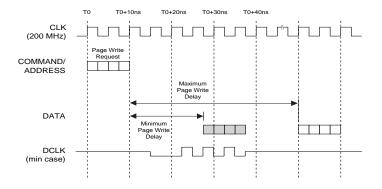

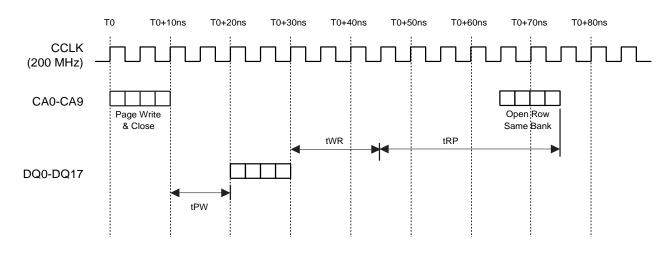

### **Page Write Delay Register**

The Page Write Delay Register is used to program the number of integer clock ticks (a.k.a. half cycles, or bit times) between receiving a Page Write Request Packet and receiving the corresponding Write Data input. Although the 8-bit register can support a range of 0 to 255 clock ticks, the value programmed must be between the minimum and maximum values as provided in the respective status registers. It is expected, though not required, that the same value would be programmed in all SLDRAMs on a channel. The specific value, from the range of allowable values, can be chosen to achieve the optimum relationship between read latency and write latency.

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| ID8 | ID7 | ID6 | ID5 | ID4 | ID3  | ID2  | ID1  | ID0  | 1    |

|-----|-----|-----|-----|-----|------|------|------|------|------|

| 0   | 0   | 0   | 1   | 1   | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0   | 0   | 0   | 0   | 1   | 0    | 1    | 0    | 0    | 0    |

| 0   | 0   | PW7 | PW6 | PW5 | PW4  | PW3  | PW2  | PW1  | PW0  |

### Figure 19 REGISTER WRITE REQUEST PACKET PAGE WRITE DELAY REGISTER

| PWx:            |                               |

|-----------------|-------------------------------|

| 7 6 5 4 3 2 1 0 | Integer Number of Clock Ticks |

| 0 0 0 0 0 0 0 0 | 0                             |

| :               | :                             |

| 1 1 1 1 1 1 1 1 | 255                           |

## Figure 20 PAGE WRITE DELAY REGISTER/BIT DEFINITION

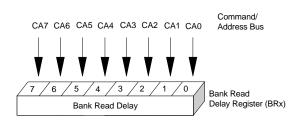

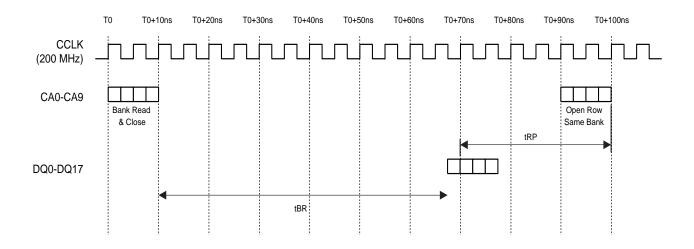

### **Bank Read Delay Register**

The Bank Read Delay Register is used to program the number of integer clock ticks (a.k.a. half cycles, or bit times) between receiving a Bank Read Request Packet and providing the corresponding Read Data output. Although the 8-bit register can support a range of 0 to 255 clock ticks, the value programmed must be between the minimum and maximum values as provided in the respective status registers. Different values may be programmed in different SLDRAMs on the same channel in order to compensate for differences in internal SLDRAM and external routing delays.

The value written to this register may subsequently be modified by Increment/Decrement Fine Read Vernier events. Such modifications are reflected in the Actual Delays Status Register.

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| ID8 | ID7 | ID6 | ID5 | ID4 | ID3  | ID2  | ID1  | ID0  | 1    |

|-----|-----|-----|-----|-----|------|------|------|------|------|

| 0   | 0   | 0   | 1   | 1   | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0   | 0   | 0   | 0   | 1   | 1    | 0    | 0    | 0    | 0    |

| 0   | 0   | BR7 | BR6 | BR5 | BR4  | BR3  | BR2  | BR1  | BR0  |

Figure 21

REGISTER WRITE REQUEST PACKET BANK READ DELAY REGISTER

| BF | ₹x: |   |   |   |   |   |   |                               |

|----|-----|---|---|---|---|---|---|-------------------------------|

| 7  | 6   | 5 | 4 | 3 | 2 | 1 | 0 | Integer Number of Clock Ticks |

| 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0                             |

|    |     |   | : |   |   |   |   | :                             |

| 1  | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 255                           |

### Figure 22 BANK READ DELAY REGISTER/BIT DEFINITION

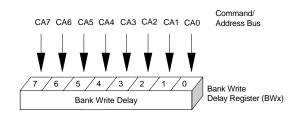

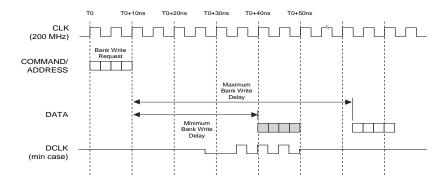

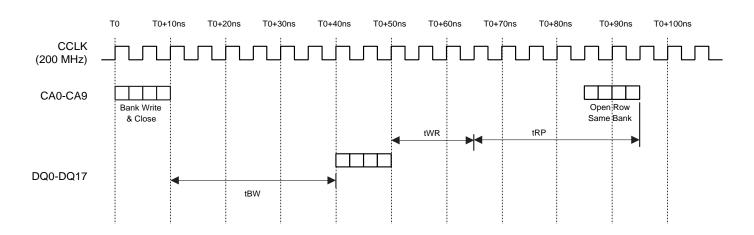

### **Bank Write Delay Register**

The Bank Write Delay Register is used to program the number of integer clock ticks (a.k.a. half cycles, or bit times) between receiving a Bank Write Request Packet and receiving the corresponding Write Data input. Although the 8-bit register can support a range of 0 to 255 clock ticks, the value programmed must be between the minimum and maximum values as provided in the respective status registers. It is expected, though not required, that the same value would be programmed in all SLDRAMs on a channel. The specific value, from the range of allowable values, can be chosen to achieve the optimum relationship between read latency and write latency.

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| ID8 | ID7 | ID6 | ID5 | ID4 | ID3  | ID2  | ID1  | ID0  | 1    |

|-----|-----|-----|-----|-----|------|------|------|------|------|

| 0   | 0   | 0   | 1   | 1   | SID4 | SID3 | SID2 | SID1 | SID0 |

| 0   | 0   | 0   | 0   | 1   | 1    | 1    | 0    | 0    | 0    |

| 0   | 0   | BW7 | BW6 | BW5 | BW4  | BW3  | BW2  | BW1  | BW0  |

### Figure 23 REGISTER WRITE REQUEST PACKET BANK WRITE DELAY REGISTER

| BWx:        |       |                               |

|-------------|-------|-------------------------------|

| 7 6 5 4 3 2 | 2 1 0 | Integer Number of Clock Ticks |

| 0 0 0 0 0   | 0 0 0 | 0                             |

| :           |       | :                             |

| 1 1 1 1 1 1 | 1 1 1 | 255                           |

## Figure 24 BANK WRITE DELAY REGISTER/BIT DEFINITION

|     | No. of 0 | Column | ıs per F | Row    | N    | lo. of D | Qs   |    | No.  | of Bar | nks  | N    | o. of R | ows pe | er Bar | nk Re | es. R |      |      |     |     |     |    | 100 D<br>ИНz О |    |            | Ма  | nufact | urer C | ode |      |

|-----|----------|--------|----------|--------|------|----------|------|----|------|--------|------|------|---------|--------|--------|-------|-------|------|------|-----|-----|-----|----|----------------|----|------------|-----|--------|--------|-----|------|

| / 3 | 1 / 30   | / 29   | / 28     | 3 / 27 | / 26 | 25       | / 24 | 23 | / 22 | / 21   | / 20 | / 19 | / 18    | / 17   | / 16   | /15   | /14   | / 13 | / 12 | /11 | /10 | / 9 | 8  | 7              | 6  | <b>/</b> 5 | / 4 | / 3    | / 2    | / 1 | / 0/ |

| СЗ  | C2       | C1     | C0       | D3     | D2   | D1       | D0   | ВЗ | B2   | B1     | ВО   | R3   | R2      | R1     | R0     | 0     | 0     | F5   | F4   | F3  | F2  | F1  | F0 | DO0            | М6 | M5         | M4  | МЗ     | M2     | M1  | мо   |

### Figure 25 CONFIGURATION REGISTER

#### STATUS REGISTERS

### **Configuration Register**

The Configuration Register contains a code which uniquely identifies the memory device vendor, the valid operating frequencies for the device, the number of banks in the device, the number of rows per bank, the number of columns per page and the number of DQs on the device.

| CA9 | CA8 | CA7 | CA6 | CA5  | CA4 | CA3 | CA2 | CA1 | CA0 |

|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|

| ID8 | ID7 | ID6 | ID5 | ID4  | ID3 | ID2 | ID1 | ID0 | 1   |

| 0   | 0   | 1   | 0   | CMD0 | 0   | 0   | 0   | 0   | 0   |

| 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 0   | 0   |

| 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 0   | 0   |

Note: CMD0 is either 0 or 1, to select the appropriate DCLK

## Figure 26 REGISTER READ REQUEST PACKET CONFIGURATION REGISTER

DQ17-8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0

| 0 | DO0 | M6 | M5 | M4 | МЗ | M2 | M1 | M0 |

|---|-----|----|----|----|----|----|----|----|

| 0 | 0   | 0  | F5 | F4 | F3 | F2 | F1 | F0 |

| 0 | В3  | B2 | B1 | В0 | R3 | R2 | R1 | R0 |

| 0 | C3  | C2 | C1 | C0 | D3 | D2 | D1 | D0 |

## Figure 27 REGISTER READ DATA PACKET CONFIGURATION REGISTER

### **Configuration Register - Data Offset Bit**

The DO0 bit indicates whether the SLDRAM supports bit level data offset. If DO0 = 0, the device supports word-wide offset only. If DO0 = 1, the device supports both word-wide and bit level offset.

### **Configuration Register - Manufacturer Field**

This field contains a code which uniquely identifies the memory device vendor.

| M | x: |   |   |   |   |   |                    |

|---|----|---|---|---|---|---|--------------------|

| 6 | 5  | 4 | 3 | 2 | 1 | 0 | Manufacturer       |

| 0 | 0  | 0 | 0 | 0 | 0 | 0 | Fujitsu            |

| 0 | 0  | 0 | 0 | 0 | 0 | 1 | Hitachi            |

| 0 | 0  | 0 | 0 | 0 | 1 | 0 | Hyundai            |

| 0 | 0  | 0 | 0 | 0 | 1 | 1 | IBM                |

| 0 | 0  | 0 | 0 | 1 | 0 | 0 | LG Semicon         |

| 0 | 0  | 0 | 0 | 1 | 0 | 1 | Micron             |

| 0 | 0  | 0 | 0 | 1 | 1 | 0 | Mitsubishi         |

| 0 | 0  | 0 | 0 | 1 | 1 | 1 | Mosel Vitelic      |

| 0 | 0  | 0 | 1 | 0 | 0 | 0 | Motorola           |

| 0 | 0  | 0 | 1 | 0 | 0 | 1 | National/Panasonic |

| 0 | 0  | 0 | 1 | 0 | 1 | 0 | NEC                |

| 0 | 0  | 0 | 1 | 0 | 1 | 1 | Nippon Steel       |

| 0 | 0  | 0 | 1 | 1 | 0 | 0 | OKI                |

| 0 | 0  | 0 | 1 | 1 | 0 | 1 | Samsung            |

| 0 | 0  | 0 | 1 | 1 | 1 | 0 | Siemens            |

| 0 | 0  | 0 | 1 | 1 | 1 | 1 | Texas Instruments  |

| 0 | 0  | 1 | 0 | 0 | 0 | 0 | Toshiba            |

| 0 | 0  | 1 | 0 | 0 | 0 | 1 | Vanguard           |

| 0 | 0  | 1 | 0 | 0 | 1 | 0 | Reserved           |

|   |    |   | : |   |   |   | :                  |

| 1 | 1  | 1 | 1 | 1 | 1 | 1 | Reserved           |

## Figure 28 CONFIGURATION REGISTER -MANUFACTURER FIELD DEFINITION

### **Configuration Register - Frequency Field**

This field indicates the valid operating frequencies for the device. Each defined bit corresponds to a specific operating frequency. At least one bit, and possibly more than one bit will be 1, indicating that the device supports that operating frequency. A 0 is provided on each reserved bit location as well as the bit locations for each operating frequency not supported. This is shown for future planning; for the devices covered by this data sheet, the value read from this field will be 000010 (bits F5-F0, respectively), indicating 200 MHz (or 400 Mb/s/p) operation.

| F5  | F4  | F3  | F2  | F1  | F0  |

|-----|-----|-----|-----|-----|-----|

| 600 | 500 | 400 | 300 | 200 | 100 |

| MHz | MHz | MHz | MHz | MHz | MHz |

## Figure 29 CONFIGURATION REGISTER FREQUENCY FIELD DEFINITION

### **Configuration Register - Bank Field**

This field indicates the number of banks in the device.

| В3 | B2 | B1 | В0 | No. of Banks  |

|----|----|----|----|---------------|

| 0  | 0  | 0  | 0  | Reserved (1)  |

| 0  | 0  | 0  | 1  | Reserved (2)  |

| 0  | 0  | 1  | 0  | Reserved (4)  |

| 0  | 0  | 1  | 1  | 8             |

| 0  | 1  | 0  | 0  | 16            |

| 0  | 1  | 0  | 1  | Reserved (32) |

| 0  | 1  | 1  | 0  | Reserved (64) |

| 0  | 1  | 1  | 1  | Reserved      |

| 1  | 0  | 0  | 0  | Reserved      |

| 1  | 0  | 0  | 1  | Reserved      |

| 1  | 0  | 1  | 0  | Reserved      |

| 1  | 0  | 1  | 1  | Reserved      |

| 1  | 1  | 0  | 0  | Reserved      |

| 1  | 1  | 0  | 1  | Reserved      |

| 1  | 1  | 1  | 0  | Reserved      |

| 1  | 1  | 1  | 1  | Reserved      |

## Figure 30 CONFIGURATION REGISTER BANK FIELD DEFINITION

#### **Configuration Register - Row Field**

This field indicates the number of rows per bank.

| R3 | R2 | R1 | R0 | No. of Rows per Bank |

|----|----|----|----|----------------------|

| 0  | 0  | 0  | 0  | Reserved             |

| 0  | 0  | 0  | 1  | Reserved (512)       |

| 0  | 0  | 1  | 0  | 1K                   |

| 0  | 0  | 1  | 1  | 2K                   |

| 0  | 1  | 0  | 0  | 4K                   |

| 0  | 1  | 0  | 1  | Reserved (8K)        |

| 0  | 1  | 1  | 0  | Reserved             |

| 0  | 1  | 1  | 1  | Reserved             |

| 1  | 0  | 0  | 0  | Reserved             |

| 1  | 0  | 0  | 1  | Reserved             |

| 1  | 0  | 1  | 0  | Reserved             |

| 1  | 0  | 1  | 1  | Reserved             |

| 1  | 1  | 0  | 0  | Reserved             |

| 1  | 1  | 0  | 1  | Reserved             |

| 1  | 1  | 1  | 0  | Reserved             |

| 1  | 1  | 1  | 1  | Reserved             |

## Figure 31 CONFIGURATION REGISTER ROW FIELD DEFINITION

### **Configuration Register - Column Field**

This field indicates the number of columns per row.

| C3 | C2 | C1 | C0 | No. of Columns per Row |

|----|----|----|----|------------------------|

| 0  | 0  | 0  | 0  | Reserved               |

| 0  | 0  | 0  | 1  | 16                     |

| 0  | 0  | 1  | 0  | 32                     |

| 0  | 0  | 1  | 1  | 64                     |

| 0  | 1  | 0  | 0  | 128                    |

| 0  | 1  | 0  | 1  | Reserved               |

| 0  | 1  | 1  | 0  | Reserved               |

| 0  | 1  | 1  | 1  | Reserved               |

| 1  | 0  | 0  | 0  | Reserved               |

| 1  | 0  | 0  | 1  | Reserved               |

| 1  | 0  | 1  | 0  | Reserved               |

| 1  | 0  | 1  | 1  | Reserved               |

| 1  | 1  | 0  | 0  | Reserved               |

| 1  | 1  | 0  | 1  | Reserved               |

| 1  | 1  | 1  | 0  | Reserved               |

| 1  | 1  | 1  | 1  | Reserved               |

Figure 32

CONFIGURATION REGISTER COLUMN FIELD DEFINITION

### **Configuration Register - DQ Field**

This field indicates the number of DQs per device.

| D3 | D2 | D1 | D0 | No. of DQs    |

|----|----|----|----|---------------|

| 0  | 0  | 0  | 0  | Reserved (4)  |

| 0  | 0  | 0  | 1  | 8             |

| 0  | 0  | 1  | 0  | Reserved (9)  |

| 0  | 0  | 1  | 1  | 16            |

| 0  | 1  | 0  | 0  | 18            |

| 0  | 1  | 0  | 1  | 32            |

| 0  | 1  | 1  | 0  | Reserved (36) |

| 0  | 1  | 1  | 1  | 64            |

| 1  | 0  | 0  | 0  | Reserved (72) |

| 1  | 0  | 0  | 1  | Reserved      |

| 1  | 0  | 1  | 0  | Reserved      |

| 1  | 0  | 1  | 1  | Reserved      |

| 1  | 1  | 0  | 0  | Reserved      |

| 1  | 1  | 0  | 1  | Reserved      |

| 1  | 1  | 1  | 0  | Reserved      |

| 1  | 1  | 1  | 1  | Reserved      |

Figure 33

CONFIGURATION REGISTER DQ FIELD DEFINITION

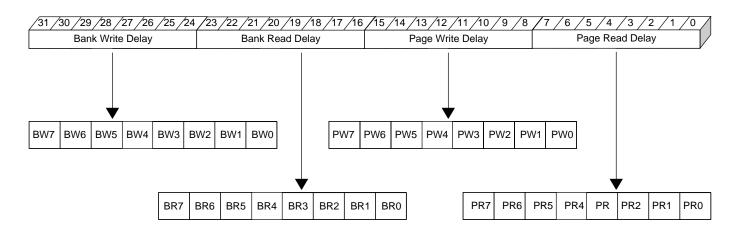

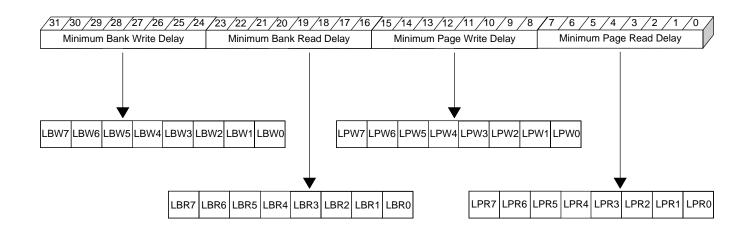

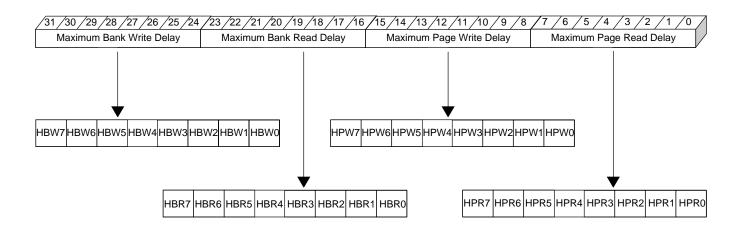

Figure 34

ACTUAL DELAY REGISTER FIELDS

### **Actual Delay Register**

This register contains the actual Page Read Delay, Page Write Delay, Bank Read Delay, and Bank Write Delay settings for the device. These values will reflect any subsequent modifications to the initial values; such modifications may result from controller programming of the corresponding Control Registers or from Fine Read Vernier adjustments.

CA9 CA8 CA7 CA6 CA5 CA4 CA3 CA2 CA1 CA0

| ID8 | ID7 | ID6 | ID5 | ID4  | ID3 | ID2 | ID1 | ID0 | 1 |

|-----|-----|-----|-----|------|-----|-----|-----|-----|---|

| 0   | 0   | 1   | 0   | CMD0 | 0   | 0   | 0   | 0   | 0 |

| 0   | 1   | 0   | 0   | 0    | 0   | 0   | 0   | 0   | 0 |

| 0   | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 0   | 0 |

## Figure 35 REGISTER READ REQUEST PACKET ACTUAL DELAY REGISTER

DQ17-8 DQ7 DQ6 DQ5 DQ4 DQ3 DQ2 DQ1 DQ0

| 0 | PR7 | PR6 | PR5 | PR4 | PR3 | PR2 | PR1 | PR0 |

|---|-----|-----|-----|-----|-----|-----|-----|-----|

| 0 | PW7 | PW6 | PW5 | PW4 | PW3 | PW2 | PW1 | PW0 |

| 0 | BR7 | BR6 | BR5 | BR4 | BR3 | BR2 | BR1 | BR0 |

| 0 | BW7 | BW6 | BW5 | BW4 | BW3 | BW2 | BW1 | BW0 |

## Figure 36 REGISTER READ DATA PACKET ACTUAL DELAY REGISTER

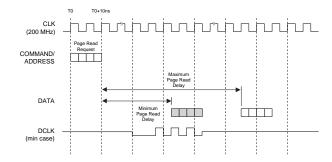

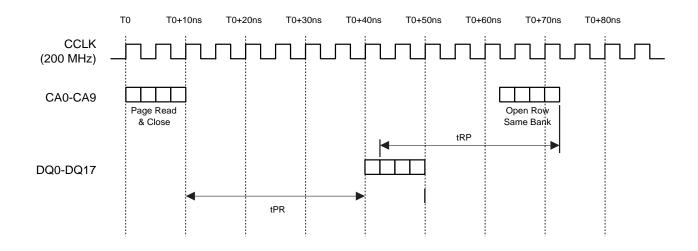

### Actual Delay Register - Actual Page Read Delay Field

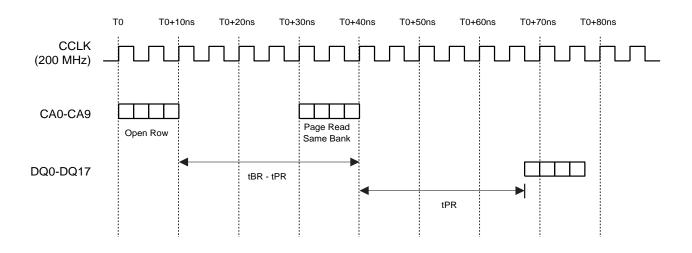

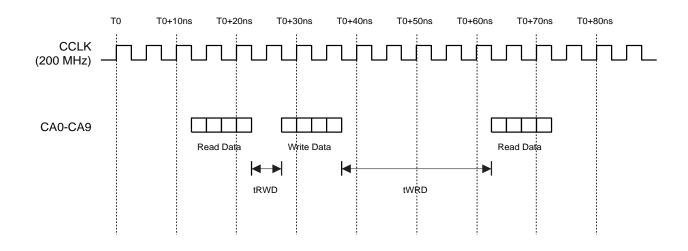

This register contains the Actual Page Read Delay supported by the device (measured in integer clock ticks between receiving a Page Read Request Packet and providing the corresponding Read Data output, as shown later in this data sheet).

| PF | ₹x: |   |   |   |   |   |   |                               |

|----|-----|---|---|---|---|---|---|-------------------------------|

| 7  | 6   | 5 | 4 | 3 | 2 | 1 | 0 | Integer Number of Clock Ticks |

| 0  | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0                             |

|    |     |   |   | : |   |   |   | :                             |

| 1  | 1   | 1 | 1 | 1 | 1 | 1 | 1 | 255                           |

# Figure 37 ACTUAL DELAY REGISTER ACTUAL PAGE READ DELAY FIELD DEFINITION

### **Actual Delay Register - Actual Page Write Delay Field**

This field contains the Actual Page Write Delay supported by the device (measured in integer clock ticks between receiving a Page Write Request Packet and receiving the corresponding Write Data input, as shown later in this data sheet).