# **Intel740 Graphics Accelerator**

**Datasheet**

February 1998

Order Number: 290618-001

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

The Intel740 may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Such errata are not covered by Intel's warranty. Current characterized errata are available on request.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol or the SMBus bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by:

calling 1-800-548-4725 or

by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

# Intel740 Features

#### • Hyper Pipelined Architecture

- 2X AGP Support

- Parallel Data Processing (PDP)

- Precise Pixel Interpolation (PPI)

Direct Memory Execution (DME)

- Direct Memory Execution (DME

- Sustained 3D Performance

- -1.1 Meg-Triangles/Second Peak

- 425-500K Triangles/Second Full

- Featured (66 Mega-Pixel Peak) - 45-55 Meg-Pixels/Second Full

- Featured

- Full Sideband Accelerated Graphics

- Port (AGP) Initiator Support

- Optimized For 440LX Intel AGPsets

#### • 3D Graphics Visual Enhancements

- Flat & Gouraud Shading

- Mip-Mapping With Bilinear Filtering (11 LODs)

- Color Alpha Blending For Transparency

- Real Time Texture Paging and Video Texturing

- Fogging & Atmospheric Effects

- Specular Lighting

- Edge Antialiasing

- Stippling Or "Screen Door" Transparency

- Backface Culling

- Z Buffering

#### • 3D Graphics Texturing Enhancements

- Per Pixel Perspective Correct Texture Mapping

- Texture Sizes From 1x1 To 1024x1024 pixels (Rect/Sq)

- Texture Formats

- Palletized 1,2,4, or 8-bit

- RGBA 1555,565,4444

- Compressed 4:2:2, 555, 1544

- Texture Color Keying

- Texture Chroma Keying

- Integrated Hardware Palette

- Local Memory Controller

- 2 to 8 MB SGRAM/SDRAM

High-Speed 64-Bit 100 MHz

- High-Speed 64-Bit 100 Interface

#### • Display/BIOS/I<sup>2</sup>C

- Integrated 24-bit 220 MHz RAMDAC

- Pixel Palette Pipeline Frequency: 203 MHz

- Display Resolution: 320x200 Up To 1600x1200 Pixels

- Gamma Corrected Video

- Multi-Monitor Capability

- Read/Write Access To 256KB Flash

- ACPI Compliant

- Display Data Channel: DDC 2B Compliant

- 2D Graphics

- Up To 1600x1200 In 8 Bit Color Format at 75 MHz

- Up to 1024x768 in 8/16/24 Bit Color Format @ 85 MHz Refresh Rate

- Hardware Accelerated Functions

- Programmable 64x64 3 Color Transparent Cursor

- 3 Operand Raster BitBLTs

- StretchBLT

- Color Expansion

- Hardware Overlay Engine

- Hardware Double Buffering

- Video

- Software DVD MPEGII Ready

- Hardware DVD MPEGII Capable

- Video Capture Support (16 Bit Or 8 Bit)

- Full Bi-directional VMI CCIR601 Video Port

- Programmable Video Output Characteristics For VGA and SVGA

- Full Motion Video

- Video Conferencing Support

- Intercast & VBI Support

- NTSC And PAL TV Out Support

- OS & Driver Support

- DirectX\* 5.0

- OpenGL\*

- Full 2X AGP Support

- Windows\* 95

- Windows\* 95 AGP VxD

- Windows NT\* 4.0

- Windows\* 98

- Windows NT\* 5.0

- 468 Pin STBGA (Super Thermal Ball Grid Array) Package

The Intel740 may contain design defects or errors known as errata which may cause the products to deviate from published specifications. Current characterized errata are available on request.

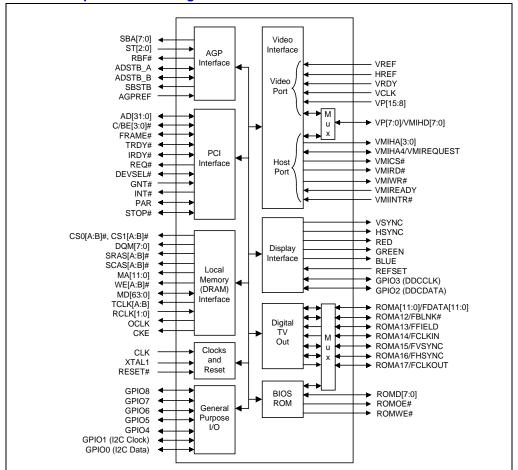

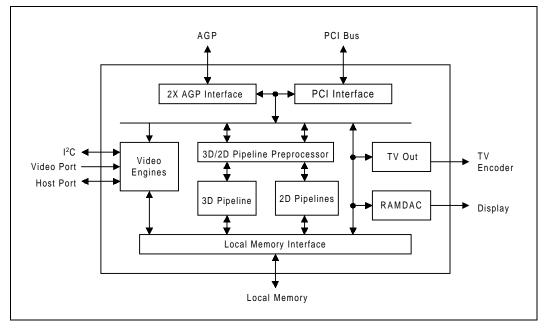

The Intel740 is a highly integrated graphics accelerator designed for the Accelerated Graphics Port (AGP). Its architecture consists of dedicated multi-media engines executing in parallel to deliver high performance 3D, 2D and video capabilities. The 3D and 2D engines are managed by a 3D/2D pipeline preprocessor allowing them a sustained flow of graphics data. The 3D engine has been architected as a deep pipeline, where performance is maximized by parallel data paths and allowing each pipeline stage to simultaneously operate on different primitives or portions of the same primitive. The Intel740 supports perspective-correct texture mapping, bilinear MIP-Mapping, Gouraud shading, alpha-blending, stippling, antialiasing, fogging and Z Buffering. A rich set of 3D instructions permit these features to be independently enabled or disabled. Textures can be located in AGP memory to free up local memory for other uses (e.g., back and Z Buffers, bitmaps, etc.).

The Intel740 2D capabilities includes BLT and STRBLT engines, a hardware cursor, and an extensive set of 2D registers and instructions. The high performance 64-bit BitBLT engine provides hardware acceleration for many common Windows\* operations.

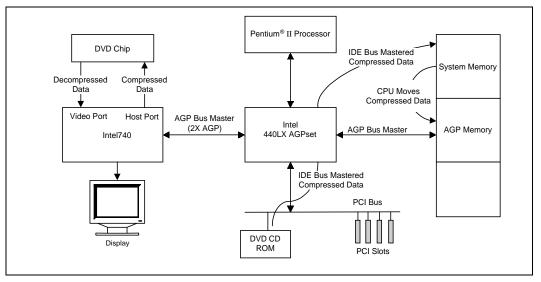

The Intel740 also includes dedicated video engines for support of video conferencing and other video applications. The Intel740's Video Module Interface (VMI) has both a Host Port and Video Port that provide the interface to the DVD chip. A full bi-directional VMI Host Port is supported for low-cost hardware MPEGII DVD decode. The Video Port interface also provides video capture for video input devices. The Video interface includes support for full motion video, MPEGII/DVD, Intercast and VBI and NTSC and PAL TV out.

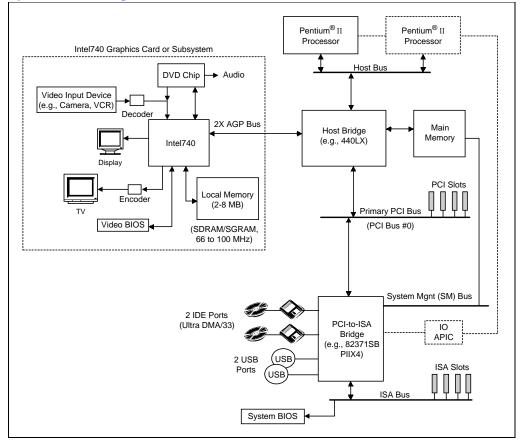

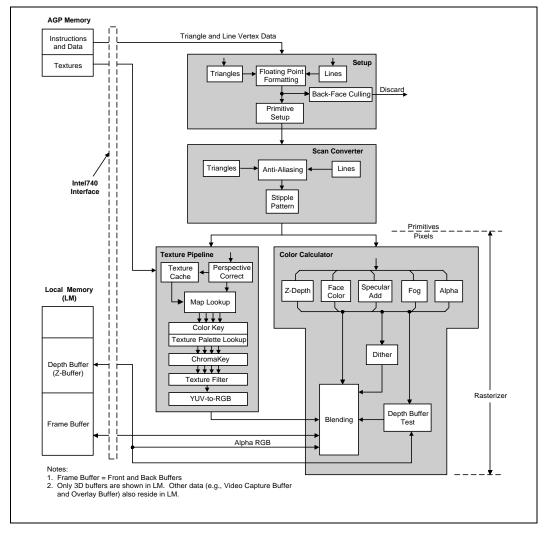

#### Intel740 Simplified Block Diagram

#### System Block Diagram with Intel740

# int<sub>e</sub>ا *Contents*

| 1 | Archit | ectural Ov  | /erview                                            | 1-1  |

|---|--------|-------------|----------------------------------------------------|------|

|   | 1.1    | 3D Ena      | ine                                                | 1-1  |

|   | 1.2    |             | ine                                                |      |

|   | 1.3    |             | Iodule Interface (VMI)                             |      |

|   | 1.4    |             | ۲۷ Out                                             |      |

|   | 1.5    | Display     |                                                    | 1-5  |

| 2 | Signa  | l Descripti | on                                                 | 2-1  |

|   | 2.1    | Strappi     | ng Options                                         | 2-8  |

| 3 | Regis  | ter Descri  | ption                                              | 3-1  |

|   | 3.1    | PCI Co      | nfiguration Registers                              | 3-2  |

|   |        | 3.1.1       | VID—Vendor Identification Register                 |      |

|   |        | 3.1.2       | DID—Device Identification Register                 |      |

|   |        | 3.1.3       | PCICMD—PCI Command Register                        |      |

|   |        | 3.1.4       | PCISTS—PCI Status Register                         |      |

|   |        | 3.1.5       | RID—Revision Identification Register               |      |

|   |        | 3.1.6       | CC—Class Code Register                             |      |

|   |        | 3.1.7       | CLS—Cache Line Size Register                       |      |

|   |        | 3.1.8       | MLT—Master Latency Timer Register                  |      |

|   |        | 3.1.9       | HDR—Header Type Register                           |      |

|   |        | 3.1.10      | BIST—BIST Register                                 |      |

|   |        | 3.1.11      | LMADR—Local Memory Range Address Register          |      |

|   |        | 3.1.12      | MMADR—Memory Mapped Range Address Register         |      |

|   |        | -           | SVID—Subsystem Vendor Identification Register      |      |

|   |        | 3.1.14      | SID—Subsystem Identification Register              |      |

|   |        | -           | ROMADR—Video BIOS ROM Base Address Register        |      |

|   |        |             | CAPPOINT—Capabilities Pointer Register             |      |

|   |        |             | INTRLINE—Interrupt Line Register                   |      |

|   |        |             | INTRPIN—Interrupt Pin Register                     |      |

|   |        | 3.1.19      | MINGNT—Minimum Grant Register                      |      |

|   |        | 3.1.20      | MAXLAT—Maximum Latency Register                    |      |

|   |        |             | AGPCAP—AGP Capabilities Register                   |      |

|   |        |             | AGPST—AGP Status Register                          |      |

|   |        |             | AGPCMC—AGP Master Command Register                 |      |

|   |        |             | PM_CAPID—Power Management Capabilities ID Register |      |

|   |        |             | PM_CAP D—Power Management Capabilities Register    |      |

|   |        |             | PM_CS—Power Management Control/Status Register     |      |

|   | 3.2    |             | Configuration Registers                            |      |

|   | 3.Z    |             |                                                    |      |

|   |        | 3.2.1       | XRX—Configurations Extension Index Register        |      |

|   |        | 3.2.2       | XR50—DRAM Row Type (DRT) Register                  |      |

|   |        | 3.2.3       | XR51—DRAM Control (DRAMC) Low Register             |      |

|   |        | 3.2.4       | XR52—DRAM Control (DRAMC) High Register            |      |

|   |        | 3.2.5       | XR53—DRAM Extended Control (DRAMEC) Register       |      |

|   |        | 3.2.6       | XR54—DRAM Timing (DRAMT) Register                  |      |

|   |        | 3.2.7       | XR55—DRAM Row Boundary 0 (DRB0) Register           |      |

|   |        | 3.2.8       | XR56—DRAM Row Boundary 1 (DRB1) Register           | 3-21 |

| 4.1        |           | struction Processing (Pipeline Preprocessor)    |      |

|------------|-----------|-------------------------------------------------|------|

| 4.2        |           | ne                                              |      |

|            |           | Buffers                                         |      |

|            |           | Setup                                           | 4-3  |

|            |           | Scan Conversion                                 | 4-4  |

|            | 4.2.4 I   | Rasterizing                                     | 4-4  |

|            | 4         | 4.2.4.1 Texturing                               | 4-4  |

|            | 4         | 4.2.4.2 Color Calculator                        | 4-6  |

| 4.3        |           | Operation                                       |      |

| 4.4        | Fixed Bli | tter (BLT) and Stretch Blitter (STRBLT) Engines | 4-8  |

|            | 4.4.1 I   | Fixed BLT Engine                                | 4-8  |

|            | 4.4.2     | Stretch BitBLT Engine                           | 4-9  |

|            | 4.4.3 I   | Hardware Cursor                                 | 4-9  |

| 4.5        |           | odule Interface (VMI)                           |      |

|            |           | /ideo Port                                      |      |

|            |           | 4.5.1.1 Capture Formats                         |      |

|            |           | 4.5.1.2 Video Port Capabilities                 |      |

|            |           | 4.5.1.3 Video Port Example Hook Up              |      |

|            | 4.5.2 I   | Host Port                                       | 4-12 |

|            | 4         | 4.5.2.1 Host Write Cycle                        | 4-12 |

|            |           | 4.5.2.2 Host Read Cycle                         |      |

|            |           | 4.5.2.3 Burst Write cycle                       |      |

|            |           | 4.5.2.4 Burst Write Cycle (Option 1)            |      |

|            | 2         | 4.5.2.5 Host Port Example Hook Up               | 4-17 |

|            | 4.5.3 (   | Overlay Engine                                  | 4-17 |

|            | 4         | 4.5.3.1 Field-Based Content                     | 4-18 |

|            | 4.5.4     | /BI and Intercast Data                          | 4-18 |

| 4.6        |           | nterface                                        |      |

|            | 4.6.1     | TV Out Connection Example                       |      |

| 4.7        | AGP/PC    | I Interface                                     | 4-21 |

| 4.8        | Local Me  | emory Interface                                 |      |

|            |           | DRAM Types                                      |      |

|            |           | Address Translation                             |      |

|            |           | SDRAM Sizing                                    |      |

|            |           | Refresh                                         |      |

| 4.9        |           |                                                 |      |

| 4.10       |           | splay Data Channel)                             |      |

| 4.11       |           |                                                 |      |

| 4.12       |           |                                                 |      |

| Electri    |           | , and Package Information                       |      |

| 5.1        |           | I Characteristics                               |      |

| J. I       |           | Absolute Maximum Ratings                        |      |

|            |           |                                                 |      |

|            |           | Thermal Characteristics                         |      |

|            |           | Power Characteristics                           |      |

| - 0        |           | D.C. Characteristics                            |      |

| 5.2<br>5.3 |           | formation                                       |      |

| L ')       | Packade   | Information                                     |      |

4

5

6

# **Figures**

| 1-1  | The Intel740 Architectural Interfaces                               | 1-1  |

|------|---------------------------------------------------------------------|------|

| 1-2  | The Intel740 Implementation of Sideband Addressing                  | 1-2  |

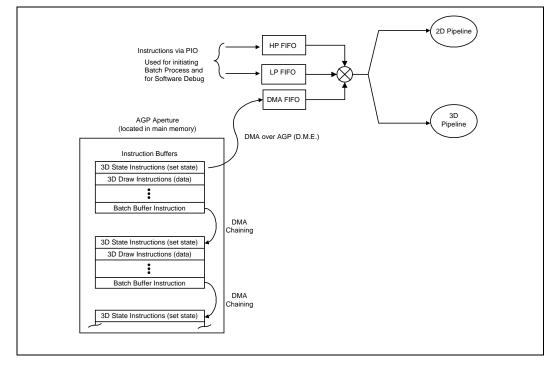

| 1-3  | Batch Processing on the Intel740—A Conceptual View                  | 1-2  |

| 1-4  | The Intel740's Ability to Execute Textures Directly From AGP Memory |      |

| 1-5  | The Intel740 Functioning as Two Memory Controllers                  |      |

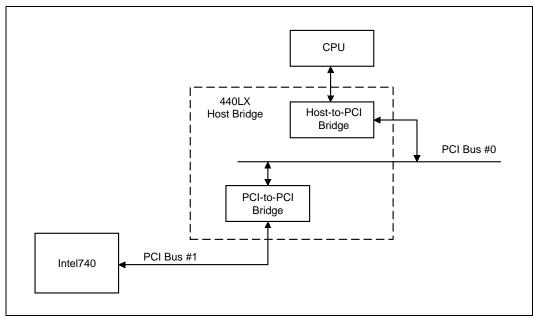

| 3-1  | PCI Bus Hierarchy (Using 82443LX as Host Bridge)                    | 3-2  |

| 4-1  | 3D/2D Pipeline Preprocessor                                         | 4-2  |

| 4-2  | The Intel740's 3D Pipeline (Parallel Data Paths)                    | 4-3  |

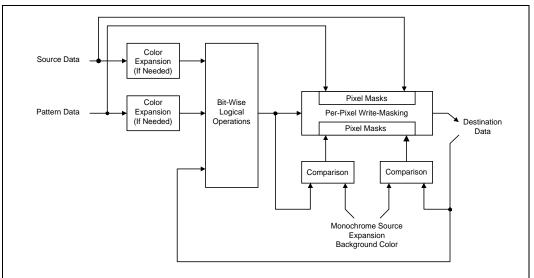

| 4-3  | BLT Engine Block Diagram and Data Paths                             | 4-9  |

| 4-4  | Data Flow For DVD Playback                                          | 4-10 |

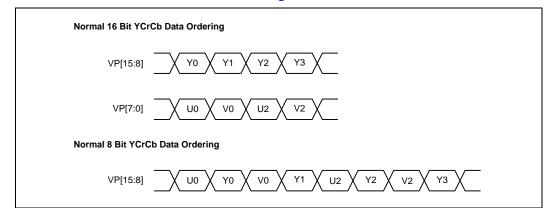

| 4-5  | Normal 8 and 16 Bit YCrCb Data Ordering                             | 4-11 |

| 4-6  | Capture Port Field Detection                                        |      |

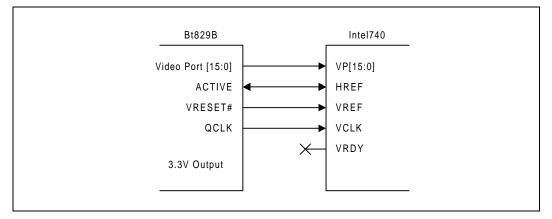

| 4-7  | Video Port Connection Example                                       | 4-12 |

| 4-8  | VMI Host Write Cycle                                                | 4-13 |

| 4-9  | VMI Host Read Cycle                                                 | 4-14 |

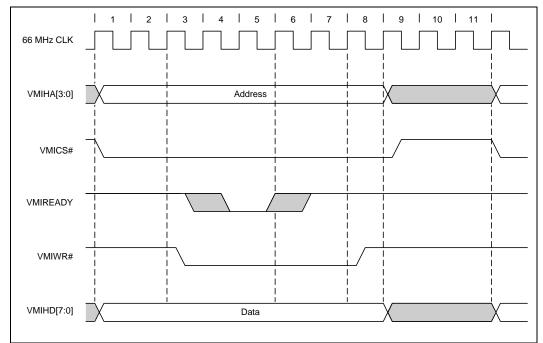

| 4-10 | VMI Burst Write Cycle                                               | 4-15 |

| 4-11 | VMI Burst Write Cycle (Option 1)                                    |      |

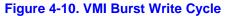

| 4-12 | VMI Connection Example For Bi-directional Mode                      | 4-17 |

| 4-13 | Capture Buffer Sharing VBI and Video Data                           | 4-18 |

| 4-14 | Intel740 Slave Mode                                                 | 4-20 |

| 4-15 | TVout Connection Example                                            |      |

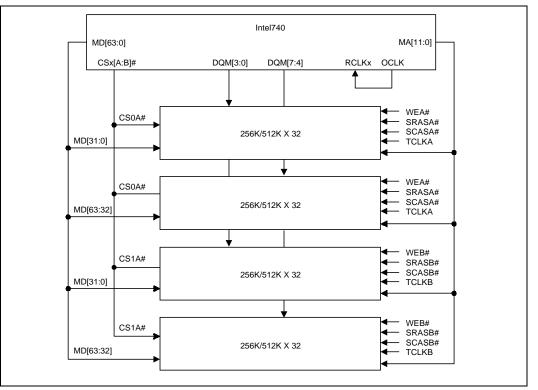

| 4-16 | 2/4 MB Local Memory Connection (64-bit Data Path)                   | 4-22 |

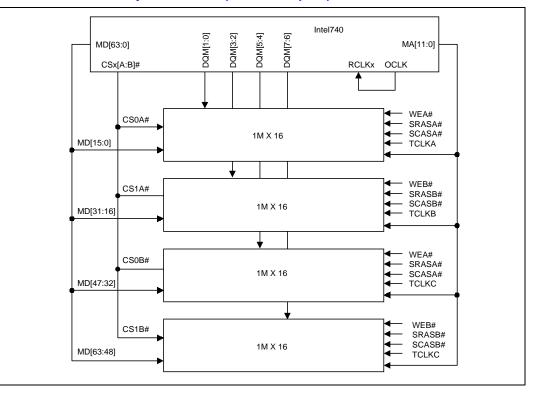

| 4-17 | 4/8 MB Local Memory Connection (64-bit data path)                   | 4-23 |

| 4-18 | 8 MB Local Memory Connection (64-bit data path)                     | 4-23 |

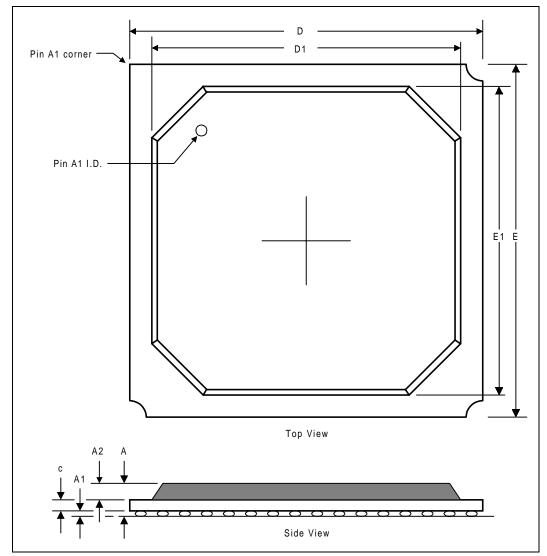

| 5-1  | The Intel740 Package Dimensions (468 STBGA) — Top and Side Views    | 5-9  |

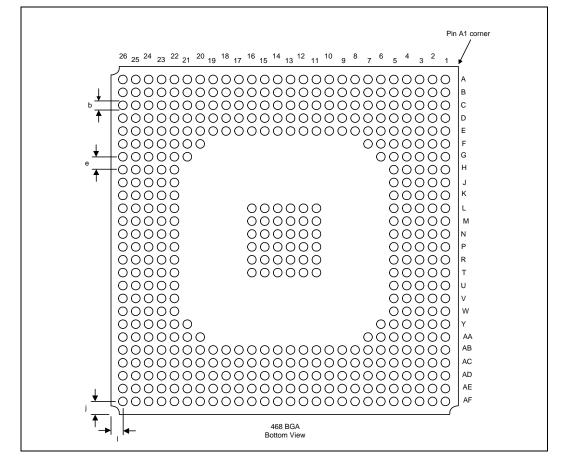

| 5-2  | The Intel740 Package Dimensions (468 STBGA)                         | 5-10 |

# **Tables**

| 1-1  | Display Modes Supported                   | 1-5  |

|------|-------------------------------------------|------|

| 2-1  | Basic PCI/AGP Signals                     | 2-1  |

| 2-2  | AGP Specific Signals                      | 2-3  |

| 2-3  | DRAM (Local Memory) Interface Signals     |      |

| 2-4  | BIOS ROM Signals                          |      |

| 2-5  | Video Interface Signals                   | 2-5  |

| 2-6  | Display Interface Signals                 | 2-6  |

| 2-7  | Digital TV Out Signals                    | 2-7  |

| 2-8  | General Purpose Input/Output Signals      | 2-7  |

| 2-9  | Clock and Reset Signals                   |      |

| 2-10 | Supply, Ground, and Test Signals          | 2-8  |

| 3-1  | PCI Configuration Space                   | 3-3  |

| 4-1  | Texture Mapping Modes                     | 4-5  |

| 4-2  | TV Out RGB Output Format                  | 4-19 |

| 4-3  | Supported Memory Types                    | 4-22 |

| 4-4  | DRB Bit Programming                       | 4-24 |

| 4-5  | The Intel740 Address Translation          | 4-24 |

| 4-6  | Dispaly Modes Supported                   | 4-25 |

| 5-1  | Intel740 Package Thermal Resistance       | 5-2  |

| 5-2  | Power Dissipation Characteristics         | 5-2  |

| 5-3  | D.C. Characteristics                      | 5-3  |

| 5-4  | Intel740 Pinout (Top View)                | 5-4  |

| 5-5  | Intel740 Pinout (Top View)                | 5-5  |

| 5-6  | Alphabetical Pin List                     | 5-6  |

| 5-7  | Pinout For Power, Ground, and No Connects | 5-8  |

| 5-8  | Intel740 Package Dimensions (468 STBGA)   |      |

| 6-1  | Intel740 Test Mode Select                 |      |

| 6-2  | NAND Chain Outputs                        | 6-1  |

| 6-3  | NAND Chain Ordering                       | 6-2  |

|      | -                                         |      |

# **Architectural Overview**

# 1

The Intel740 is a highly integrated graphics accelerator designed for the Accelerated Graphics Port (AGP). Its architecture consists of dedicated multi-media engines executing in parallel to deliver high performance 3D, 2D and video capabilities. The 3D and 2D engines are managed by the 3D/2D pipeline preprocessor allowing them a sustained flow of graphics data. The Intel740 also includes dedicated video engines for support of video conferencing and other video applications. Each of these functional units is described in detail in the *Functional Description* Chapter.

### 1.1 3D Engine

The Intel740 is capable of delivering a high rate of sustained 3D graphics performance with full 3D feature set functionality. This constant high level of performance is delivered through the Intel740's hyper-pipelined 3D architecture and the incorporation of specific graphics architectural enhancements. With the use of Direct Memory Execution (DME), the Intel740 fully utilizes the bandwidth of AGP and memory, benefiting the heavy data demands of 3D. DME is a technique that allows the Intel740 to store and execute textures in system memory instead of local graphics memory. This provides high levels of performance and unlimited texture sizes.

Architectural enhancements within the 3D pipeline ensure that the Intel740 uses this data in the most efficient way possible. Parallel Data Processing (PDP) allows several commands to be executed at the same time in the graphics pipeline. This translates into consistent high-performance regardless of the number of features enabled in a scene. Precise-Pixel Interpolation (PPI) contributes to the hyper-pipelined 3D quality with the Intel740's unique texture engine that delivers precise accuracy in interpolation operations of pixel values and color values. This detailed pixel processing maintains a high level of image quality in every scene.

The DME architecture means that full 2X AGP implementation is integrated into the Intel740 with sideband operations supporting Type 1, Type 2, and Type 3 sideband cycles. This allows 533 MB/s peak data transfers. Type 3 support permits textures to be located anywhere in the 32-bit system memory address space. Deep buffering allows the Intel740 to receive data at this high rate and handle any latencies associated with AGP transactions.

Sideband addressing gives the Intel740 the ability to issue multiple requests without having to wait for data to be returned. This allows the Intel740 to achieve the highest possible sustained data transfer rates across 2X AGP and makes DME possible.

#### Figure 1-2. The Intel740 Implementation of Sideband Addressing

|                                     |        | Tim   | e                  |           |      |       |     |         |

|-------------------------------------|--------|-------|--------------------|-----------|------|-------|-----|---------|

| Non Sideband Implementat            | tion   |       |                    |           |      |       |     |         |

|                                     | Reques | t Dat | a I                | Request   | t    | Data  | R   | lequest |

| Maximum Throughput With<br>Sideband |        |       | entation<br>equest | n<br>Requ | uest | Reque | est |         |

|                                     |        |       | 1                  |           |      |       |     | -       |

| Data Path                           |        | Data  | Da                 | ta        | Data | a     | Dat | a       |

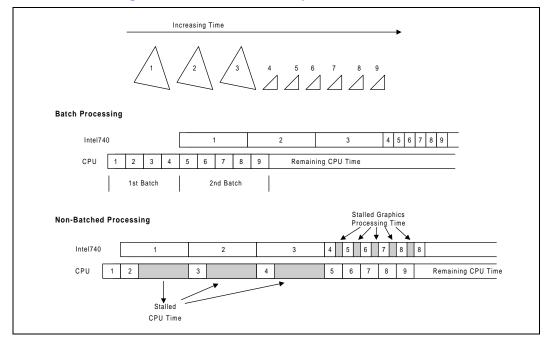

To provide the highest level of system concurrency and performance the Intel740 is optimized for a batch processing mode of triangle delivery. Batch processing frees up the CPU for intelligent 3D gaming and more complex geometry processing. This batch processing allows the CPU to place a "batch" of triangles in memory and begin on another batch of triangles without the need to perform handshaking with the Intel740.

#### Figure 1-3. Batch Processing on the Intel740—A Conceptual View

The DME capabilities of the Intel740 maximize the amount of memory available for rendering (Figure 1-4). The Intel740 is capable of executing directly from AGP memory. This "direct execution" avoids the "thrashing" of local memory associated with an architecture that must load local memory from AGP or system memory. As such, textures can be executed directly from AGP memory allowing performance to be sustained even when the texture footprint increases.

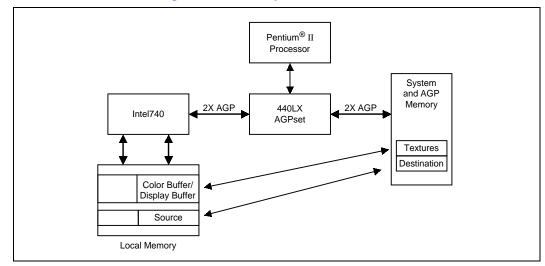

As Figure 1-5 indicates, the Intel740 is capable of rendering from local memory while textures are being executed from AGP memory through parallel arbitration. This arbitration allows a combined memory peak bandwidth of 1.3 GB/s. The capability to support two open pages in local memory coupled with an additional memory channel in AGP memory supports the 3D rendering model of color (front/back buffers), z, and textures. The Intel740 also supports 2D rendering through the use of three raster operands (pattern, source and destination).

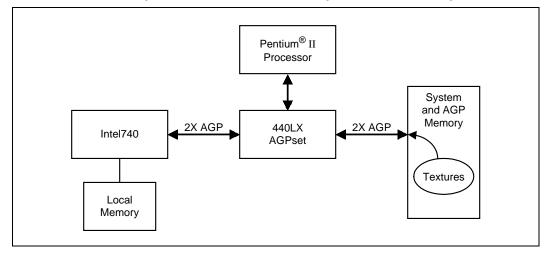

#### Figure 1-4. The Intel740's Ability to Execute Textures Directly From AGP Memory

Figure 1-5. The Intel740 Functioning as Two Memory Controllers

Included in the Intel740's architecture are dedicated 3D pipeline enhancements. These enhancements are designed to manage the way in which 3D data is requested from memory and then used within the compute engine. While parallelism is employed among each of the Intel740's engines, the 3D pipeline calculates 3D data in a highly parallel fashion. With this architecture, the 3D rasterizer is able to compute four fully textured, shaded, fogged and Z Buffered pixels per clock. The 3D pipeline requests data from memory so that memory locality is maximized, regardless of triangle size or orientation. This results in fewer page misses, higher cache efficiency, and a highly sustained 3D graphics output independent of the complexity of the 3D scene being rendered. By combining memory efficiencies and processing data efficiencies, the Intel740 is capable of a high rate of sustained 3D performance.

## 1.2 2D Engine

The Intel740's 64-bit BitBLT engine provides hardware acceleration for many common Windows operations. There are two primary BitBLT functions: Fixed BitBLT (BLT) and Stretch BitBLT (STRBLT). The term BitBLT refers to block transfers of pixel data between memory locations. Use of the BLT engine accelerates the Graphical User Interface (GUI) of Microsoft\* Windows. Hardware is included for all 256 Raster Operations (ROPs) defined by Microsoft\*, including transparent BitBLT. The BLT engines can be used for various functions including:

- · Moving rectangular blocks of data between memory locations

- Pixel format conversion

- Data Alignment

- Performing logical operations

The Intel740 uses instructions to invoke BLT and STRBLT operations, permitting software to set up instruction buffers and use batch processing as described in the *3D/2D Instruction Processing* (*Pipeline Preprocessor*) Section. Like the 3D engine described in the previous section, 2D batch processing takes full advantage of 2X AGP and frees up the CPU. Deep buffering allows the Intel740 to receive data at a high rate and handle any latencies associated with AGP transactions.

## 1.3 Video Module Interface (VMI)

The Intel740 VMI consists of a Video Port and a Host Port. The Host Port provides an enhanced VMI 1.4 Mode B Port. The enhancements allow burst modes of operation. The Intel740 Video Port is used to receive decompressed video data from a DVD chip or video data from a Video Decoder chip. A CCIR601 digital interface is supported as the primary capture standard. Using both the host and video ports, DVD, TV, Intercast, and video capture can be achieved. Use of the Intel740 overlay capability allows images from the capture engine to be displayed while being captured.

# 1.4 Digital TV Out

The Intel740 TVout port provides a digital output interface to either a television or monitor. The interface has a 12-bit data bus and connects to a television via a standard TV encoder chip (e.g., a Brooktree\* BT869). Output to the encoder is in digital 24-bit RGB format. The following resolutions are supported:

- 320x200

- 320x240

- 640x400

- 640x480

- 720x480

- 800x600

### 1.5 Display

The display function contains a RAM-based Digital-to-Analog Converter (RAMDAC) that transforms the digital data from the graphics and video subsystems to analog data for the monitor. The following display modes are supported.

#### Table 1-1. Display Modes Supported

|            | Bits Per Pixel<br>(frequency: Hz) |                |                |  |  |

|------------|-----------------------------------|----------------|----------------|--|--|

| Resolution | 8-bit Indexed                     | 16-bit         | 24-bit         |  |  |

| 320x200    | 60,72,75,85                       | 60,72,75,85    | 60,72,75,85    |  |  |

| 320x240    | 60,72,75,85                       | 60,72,75,85    | 60,72,75,85    |  |  |

| 512x384    | 60,72,75,85                       | 60,72,75,85    | 60,72,75,85    |  |  |

| 640x350    | 85                                | 85             | 85             |  |  |

| 640x480    | 60,72,75,85                       | 60,72,75,85    | 60,72,75,85    |  |  |

| 800x600    | 56,60,72,75,85                    | 56,60,72,75,85 | 56,60,72,75,85 |  |  |

| 1024x768   | 60,70,75,85                       | 60,70,75,85    | 60,70,75,85    |  |  |

| 1280x1024  | 60,72,75,85                       | 60,72,75       | —              |  |  |

| 1600x1200  | 60,75                             | —              | —              |  |  |

# Signal Description

This section provides a detailed description of each signal for the Intel740. The signals are arranged in functional groups according to their associated interface.

The "#" symbol at the end of a signal name indicates that the active, or asserted, state occurs when the signal is at a low voltage level. When "#" is not present after the signal name the signal is asserted when at the high voltage level.

The terms assertion and negation are used extensively. This is done to avoid confusion when working with a mixture of "active-low" and "active-high" signals. The term **assert**, or **assertion** indicates that a signal is active, independent of whether that level is represented by a high or low voltage. The term **negate**, or **negation** indicates that a signal is inactive.

The signal description also includes the type of buffer used for the particular signal:

- I Input pin

- O Output pin

- **OD** Open Drain Output pin. This pin requires a pull-up to the VCC of the processor core

- **I/O** Bi-directional input/output pin

The signal description also includes the type of buffer used for the particular signal:

AGP AGP/PCI-66/133MHz 3.3V Signaling Environment DC and AC Specifications.

LVTTL Low Voltage TTL compatible signals. These are also 3.3V inputs and outputs.

#### Table 2-1. Basic PCI/AGP Signals (Sheet 1 of 2)

| Name     | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD[31:0] | I/O,<br>AGP | <b>PCI Address/Data:</b> When the Intel740 acts as a target on the PCI Bus, the AD[31:0] signals are inputs for address reads/writes and write data, and outputs for read data. AD[31:0] contain the address during the first clock of FRAME# assertion and data on subsequent clocks. Note that AD16 is also used as the IDSEL function.                                                                                                 |

|          | AGP         | <b>AGP Address/Data:</b> The Intel740 acts as an AGP master. Data is driven or received by the Intel740 after appropriate commands are enqueued to the host-to-PCI bridge (via the side band address bus).                                                                                                                                                                                                                                |

| DEVSEL#  | I/O,<br>AGP | <b>PCI Device Select:</b> Remains as DEVSEL# when a PCI transaction is initiated (FRAME# is asserted). DEVSEL#, when asserted, indicates that the Intel740 as a PCI target device has decoded its address as the target of the current access. When the Intel740 is a PCI master, DEVSEL# is asserted by the system memory controller when it has decoded its address as the target of the current access.<br><b>AGP:</b> Not Used on AGP |

| FRAME#   | I/O,<br>AGP | <b>PCI Frame:</b> The Intel740 latches the C/BE[3:0]# and the AD[31:0] signals on the first clock edge on that it samples FRAME# asserted. FRAME# is negated by the initiator and remains negated by its own on-board pull up resistor.<br><b>AGP:</b> Not Used on AGP                                                                                                                                                                    |

#### Table 2-1. Basic PCI/AGP Signals (Sheet 2 of 2)

| Name       | Туре        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |             | <b>PCI Initiator Ready:</b> The assertion of IRDY# indicates the current PCI Bus initiator's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                                                                                                              |

| IRDY#      | I/O,<br>AGP | <b>AGP Initiator Ready:</b> IRDY# assertion for reads indicates the AGP master can accept the next 32 bytes of read data. The master is not allowed to insert wait states during the first 32 bytes of a read transaction. However, it can insert wait states after each 32 byte block is transferred. IRDY# assertion for writes indicates that the master is ready to transfer all write data for the current transaction. Once IRDY# is asserted for writes the master is not allowed to insert wait states, (There is no FRAME# IRDY# relationship.) |

| C/BE[3:0]# | I/O,<br>AGP | PCI Command/Byte Enable: PCI Bus Command and Byte Enable signals are multiplexed on the same pins. During the address phase of a transaction, C/BE[3:0]# define the bus command. During the data phase C/BE[3:0]# are used as byte enables. The byte enables determine which byte lanes carry meaningful data.<br>AGP Byte Enable: Provides valid byte information during AGP write transactions                                                                                                                                                         |

|            |             | and are not used during the return of AGP read data.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            |             | <b>PCI Target Ready:</b> The assertion of TRDY# indicates the target's ability to complete the current data phase of the transaction.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TRDY#      | I/O,<br>AGP | <b>AGP Target Ready:</b> TRDY# assertion indicates that the AGP target is ready to provide read data for the entire transaction (when the transfer size is less than or equal to 32 bytes) or is ready to transfer the initial or subsequent block (32 bytes) of data, when the transfer size is greater than 32 bytes. The target is allowed to insert wait states after each block is transferred on both read and write transactions.                                                                                                                 |

| PAR        | I/O,<br>AGP | <ul> <li>Parity: PAR is "even" and is calculated on 36 bits (AD[31:0] and C/BE[3:0]#). Even parity means a count of the number of "1s" within the 36 bits plus PAR should be even. PAR is always calculated on 36 bits regardless of the valid byte enables. PAR drives PAR for read data phase and is only guaranteed to be valid for 1 PCI clock after the data phase. PAR is driven and tri-stated identically to the AD[31:0] lines except for this extra 1 clock delay.</li> <li>AGP: This signal is not used for AGP cycles.</li> </ul>            |

|            |             | PCI Stop: This signal remains as STOP# when a PCI transaction is initiated                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| STOP#      | I/O,<br>AGP | (FRAME# is asserted).<br>AGP: This signal is not used for AGP cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| REQ#       | O,<br>AGP   | <b>PCI Request:</b> This signal Indicates to the arbiter that the Intel740 wants to use the PCI bus AGP Request.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | ,           | AGP Request: Sideband signals are used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| GNT#       | l,<br>AGP   | <b>PCI Grant:</b> Indicates to the Intel740 that it has been granted access to the bus.<br><b>AGP Grant:</b> ST[2:0] data is only valid when GNT# is asserted. When GNT# is negated, these signals have no meaning and must be ignored.                                                                                                                                                                                                                                                                                                                  |

| INT#       | O,<br>AGP   | PCI and AGP INT: INT# is used to request an interrupt.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

**NOTE:** All PCI signals behave according to the PCI 2.1 specification.

#### Table 2-2. AGP Specific Signals

| Name     | Туре        | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          |             | AGP Addressing (Sideband Signals)                                                                                                                                                                                                                                                                                                                    |  |  |  |

| SBA[7:0] | O,<br>AGP   | <b>Side Band Address:</b> The SBA[7:0] bus is used to pass address and command to the target from the master. The Intel740 does not use the PIPE# protocol; thus, this is the only way of enqueueing requests to the AGP target.                                                                                                                     |  |  |  |

|          |             | AGP Flow Control and Status Signals                                                                                                                                                                                                                                                                                                                  |  |  |  |

| RBF#     | O,<br>AGP   | <b>Read Buffer Full:</b> This signal indicates if the Intel740 is ready to accept previously requested low priority read data or not. When asserted, the arbiter is not allowed to return low priority read data to the Intel740.                                                                                                                    |  |  |  |

|          |             | Status Bus:       ST[2:0] provide information from the AGP arbiter to a master on what it may do.         ST[2:0] have meaning to the Intel740 when its GNT# is asserted. When GNT# is negated, these signals have no meaning and must be ignored.         000       Indicates that previously requested low priority read data is being returned to |  |  |  |

|          |             | <ul> <li>1000 Indicates that previously requested low phony read data is being returned to the master.</li> <li>1001 Indicates that previously requested high priority read data is being returned to the master.</li> </ul>                                                                                                                         |  |  |  |

| ST[2:0]  |             | 010 Indicates that the master is to provide low priority write data for a previous enqueued write command.                                                                                                                                                                                                                                           |  |  |  |

|          | I,<br>AGP   | 011 Indicates that the master is to provide high priority write data for a previous enqueued write command. This is not used by the Intel740 and will not be responded to.                                                                                                                                                                           |  |  |  |

|          |             | 100 Reserved                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |             | 101 Reserved                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |             | 110 Reserved                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|          |             | 111 Indicates that the master has been given permission to start a bus<br>transaction. In particular, this encoding is recognized by the Intel740 PCI as a<br>grant to be a PCI master. The Intel740 does not use this functionality to post<br>its status word to the host memory via PCI.                                                          |  |  |  |

|          |             | AGP Clocking Signals                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| ADSTB_A  | I/O,<br>AGP | AD Bus Strobe: This signal provides timing for double clocked data on the AD[15:0] bus.                                                                                                                                                                                                                                                              |  |  |  |

| ADSTB_B  | I/O,<br>AGP | <b>AD Bus Strobe:</b> This signal is a copy of ADSTB_A that provides timing for double clocked data on the AD[31:16] bus.                                                                                                                                                                                                                            |  |  |  |

| SBSTB    | O,<br>AGP   | Side Band Strobe. This signal provides timing for SBA[7:0].                                                                                                                                                                                                                                                                                          |  |  |  |

| AGPREF   | Ref         | Analog Reference: This is the analog reference voltage for the AGP port. This pin should be connected to a reference voltage source of 0.4 VDDQ which is used to determine the trip point of the AGP buffers.                                                                                                                                        |  |  |  |

#### Table 2-3. DRAM (Local Memory) Interface Signals

| Name                    | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CS0[A:B]#/<br>CS1[A:B]# | O,<br>LVTTL   | <b>Chip Select (SDRAM):</b> For the memory row configured with SDRAM, these signals select the particular SDRAM components during the active state. CSxA# and CSxB# are multiple copies of the same signal.                                                                                                                                                                                           |

| DQM[7:0]                | O,<br>LVTTL   | <b>Input/Output Data Mask (SDRAM):</b> These signals control the memory array and act as synchronized output enables during read cycles and as a byte enables during write cycles. For write cycles, byte masking functions are performed during the same clock when write data is driven (i.e., 0 clock latency).                                                                                    |

| SRASA#/<br>SRASB#       | O,<br>LVTTL   | <b>SDRAM Row Address Strobe (SDRAM):</b> SRASA# and SRASB# are multiple copies of the same logical signal (for loading purposes) used to generate SDRAM commands encoded on the SRASx/SCASx/WEx signals. When SRAS# is sampled active at the rising edge of the SDRAM clock, the row address is latched into the SDRAMs. These signals drive the SDRAM array directly without any external buffers.   |

| SCASA#/<br>SCASB#       | O,<br>LVTTL   | <b>SDRAM Column Address Strobe (SDRAM):</b> SCASA# and SCASB# are multiple copies of the same logical signal (for loading purposes) used to generate SDRAM commands encoded on SRAS#/SCAS#/WE# signals. When SCAS# is sampled active at the rising edge of the SDRAM clock, the column address is latched into the SDRAMs. These signals drive the SDRAM array directly without any external buffers. |

| MA[11:0]                | O,<br>LVTTL   | <b>Memory Address(SDRAM):</b> MA[11:0] are used to provide the multiplexed row and column addresses to DRAM.                                                                                                                                                                                                                                                                                          |

| WEA#/<br>WEB#           | O,<br>LVTTL   | Write Enable Signal (SDRAM): WEx# is asserted during writes to DRAM. WEA# and WEB# are multiple copies of the same signal.                                                                                                                                                                                                                                                                            |

| MD[63:0]                | I/O,<br>LVTTL | <b>Memory Data (SDRAM):</b> These signals provide a 64-bit data path to the DRAM array. Note that these signals are internally connected to 20 K $\Omega$ (nominal) pull-down resistors to prevent the memory data bus from floating when no DRAM is active.                                                                                                                                          |

| TCLK[A:B]               | O,<br>LVTTL   | Transmit Clock for SDRAM: There are 2 copies of TCLK.                                                                                                                                                                                                                                                                                                                                                 |

| RCLK0                   | I,<br>LVTTL   | <b>Receive Clock Low:</b> RCLK0 is a copy of OCLK appropriately phase adjusted to match the SDRAM/board timings. RCLK0 is used to latch the lower 32 bits of data from SDRAM.                                                                                                                                                                                                                         |

| RCLK1                   | I,<br>LVTTL   | <b>Receive Clock High:</b> RCLK1 is a copy of OCLK appropriately phase adjusted to match the SDRAM/board timings. RCLK1 is used to latch the upper 32 bits of data from SDRAM.                                                                                                                                                                                                                        |

| OCLK                    | O,<br>LVTTL   | Output Clock: OCLK is a copy of TCLK and is used to derive the RCLKxs.                                                                                                                                                                                                                                                                                                                                |

| CKE                     | O,<br>LVTTL   | <b>Clock Enable:</b> This signal is used for SDRAM powerdown control. All SDRAM banks must be precharged before CKE is negated.                                                                                                                                                                                                                                                                       |

#### Table 2-4. BIOS ROM Signals

| Pin Name                                                                                      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMA[17:0]/<br>FDATA[11:0},<br>FBLNK#<br>FFIELD<br>FCLKIN,<br>FVSYNC#,<br>FHSYNC#,<br>FCLKOUT | I/O  | <b>BIOS ROM Address (Outputs):</b> The Intel740 can access up to a 256 KB of dedicated BIOS ROM through ROMA[17:0].<br>ROMA[15:0] are externally strapped to encode the subsystem vendor ID (see <i>Strapping Option</i> section for details). Note that these signals are internally connected to pull-down resistors (20 K $\Omega$ nominal value).<br>The ROMA[17:0] pins are multiplexed with the Digital TV Out signals. |

| ROMD[7:0]                                                                                     | I/O  | <b>BIOS ROM Data:</b> The Intel740 is capable of reading or writing data to the BIOS with these pins.                                                                                                                                                                                                                                                                                                                         |

| ROMOE#                                                                                        | 0    | BIOS ROM Output Enable: This signal selects a read of BIOS ROM.                                                                                                                                                                                                                                                                                                                                                               |

| ROMWE#                                                                                        | 0    | BIOS ROM Write Enable: This signal selects a write of BIOS ROM.                                                                                                                                                                                                                                                                                                                                                               |

#### Table 2-5. Video Interface Signals (Sheet 1 of 2)

| Pin Name               | Туре                                                                              | Description                                                                                                                                                                                                                                                                                                             |  |  |  |

|------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                        | VMI Video Port                                                                    |                                                                                                                                                                                                                                                                                                                         |  |  |  |

| VREF                   | I,<br>LVTTL Vertical Reference Input: Vertical reference input for video capture. |                                                                                                                                                                                                                                                                                                                         |  |  |  |

| HREF                   | I,<br>LVTTL                                                                       | Horizontal Reference Input: Horizontal reference input for video capture.                                                                                                                                                                                                                                               |  |  |  |

| VRDY                   | I,<br>LVTTL                                                                       | Video System Ready: This input signal indicates that the video system has placed valid data on the VP[15:0] bus.                                                                                                                                                                                                        |  |  |  |

| VCLK                   | I,<br>LVTTL                                                                       | <b>VAFC Video Input Clock:</b> VCLK is the continuous master clock driven from the video system.                                                                                                                                                                                                                        |  |  |  |

|                        |                                                                                   | Video Capture Data Port (Upper Byte): VP[15:8] are the video data inputs to the Intel740. They are used when the video capture port is in 8-bit mode. For 16-bit mode, VP[15:0] are used.                                                                                                                               |  |  |  |

| VP[15:8]               | I,<br>LVTTL                                                                       | VP[15:0] also provide strapping options for the subsystem identification which the Intel740 recognizes during a hard reset (see Strapping Options section for details). Note that these signals are internally connected to 20 K $\Omega$ (nominal) pull-down resistors. This signal is tri-stated during a hard reset. |  |  |  |

| VP[7:0]/               | I/O,                                                                              | Video Capture Data Port (Lower Byte): VP[7:0] are the video data inputs to the Intel740. This pins are shared with the bi-directional VMI host port data signals (VMIHD[7:0]).<br>VP[15:0] also provide strapping options for the subsystem identification which                                                        |  |  |  |

| VMIHD[7:0]             | LVTTL                                                                             | the Intel740 recognizes during a hard reset (see Strapping Options section for details). Note that these signals are internally connected to 20 K $\Omega$ (nominal) pull-down resistors. This signal is tri-stated during a hard reset.                                                                                |  |  |  |

|                        |                                                                                   | VMI Host Port                                                                                                                                                                                                                                                                                                           |  |  |  |

| )/D[7:0]/              |                                                                                   | VMI Host Data: VP[15:8] are the video data input/output signals to the Intel740. These pins are shared with the VMI video capture port input signals (VP[7:0]).                                                                                                                                                         |  |  |  |

| VP[7:0]/<br>VMIHD[7:0] | I,<br>LVTTL                                                                       | VP[15:0] also provide strapping options for the subsystem identification which the Intel740 recognizes during a hard reset (see Strapping Options section for details). Note that these signals are internally connected to 20 K $_{\Omega}$ (nominal) pull-down resistors.                                             |  |  |  |

#### Table 2-5. Video Interface Signals (Sheet 2 of 2)

| Pin Name                            | Туре                         | Description                                                                                                                                              |  |

|-------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VMIHA[3:0]<br>VMIHA4/<br>VMIREQUEST | O,<br>LVTTL<br>I/O,<br>LVTTL | VMI Host Address: The VMIHA[4:0] output signals provide the host address.<br>VMI Request: VMIREQUEST is a data request to the Intel740 for DVD DMA data. |  |

| VMICS#                              | O,<br>LVTTL                  | <b>VMI Chip Select:</b> The Intel740 asserts this signal for read/write operations to the DVD chip.                                                      |  |

| VMIRD#                              | O,<br>LVTTL                  | VMI Read: This signal indicates a VMI read cycle.                                                                                                        |  |

| VMIWR#                              | O,<br>LVTTL                  | VMI Write: This signal indicates a VMI write cycle.                                                                                                      |  |

| VMIREADY                            | I,<br>LVTTL                  | VMI Ready: VMIREADY indicates to the Intel740 that the DVD device is ready for data. This signal is used to insert wait states.                          |  |

| VMIINTR#                            | I,<br>LVTTL                  | <b>VMI Interrupt Request:</b> This signal provides a VMI interrupt request from the DVD chip to the Intel740.                                            |  |

#### Table 2-6. Display Interface Signals

| Pin Name           | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSYNC              | 0            | <b>CRT Vertical Synchronization:</b> This signal is used as the vertical sync (polarity is programmable) or "Vsync Interval".                                                                                                                                                                                                                                                                                                                                                                                                                      |

| HSYNC              | 0            | <b>CRT Horizontal Synchronization:</b> This signal is used as the horizontal sync (polarity is programmable).                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| RED                | O,<br>Analog | <b>Red (Analog Video Output):</b> This signal is a CRT Analog video output from the internal color palette DAC. The DAC is designed for a $37.5\Omega$ equivalent load on each pin (e.g., $75\Omega$ resistor on the board, in parallel with the $75\Omega$ CRT load).                                                                                                                                                                                                                                                                             |

| GREEN              | O,<br>Analog | <b>Green (Analog Video Output):</b> This signal is a CRT analog video output from the internal color palette DAC. The DAC is designed for a $37.5\Omega$ equivalent load on each pin (e.g., $75\Omega$ resistor on the board, in parallel with the $75\Omega$ CRT load).                                                                                                                                                                                                                                                                           |

| BLUE               | O,<br>Analog | <b>Blue (Analog Video Output):</b> This signal is a CRT Analog video output from the internal color palette DAC. The DAC is designed for a $37.5\Omega$ equivalent load on each pin (e.g., $75\Omega$ resistor on the board, in parallel with the $75\Omega$ CRT load).                                                                                                                                                                                                                                                                            |

| REFSET             | I,<br>NA     | <b>Resistor Set:</b> Set point resistor for the internal color palette DAC. A 560 $\Omega$ 1% resistor is required between REFSET and VSSA.                                                                                                                                                                                                                                                                                                                                                                                                        |

| GPIO3<br>(DDCCLK)  | I/O          | <b>CRT Monitor DDC Interface clock.</b> This GPIO signal is configurable as a CRT Monitor DDC Interface clock. (Also referred to as VESA <sup>*</sup> "Display Data Channel"; also referred to as the "Monitor Plug-n-Play" interface.) For DDC1, DCLK and DDAT provide a unidirectional channel for Extended Display ID. For DDC2, DCLK and DDAT can be used to establish a bi-directional channel based on the I <sup>2</sup> C protocol. The host can request Extended Display ID or Video Display Interface information over the DDC2 channel. |

| GPIO2<br>(DDCDATA) | I/O          | <b>CRT Monitor DDC Interface data.</b> This GPIO signal is configurable as CRT Monitor DDC Interface Data.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### Table 2-7. Digital TV Out Signals

| Pin Name                   | Туре          | Description                                                                                                                   |

|----------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------|

| ROMA[11:0]/<br>FDATA[11:0] | I/O,<br>LVTTL | TV Data Out: Data to be output to the TV encoder.                                                                             |

| ROMA14/<br>FCLKIN          | I,<br>LVTTL   | TV Pixel Clock Input: Pixel Clock from TV encoder.                                                                            |

| ROMA16/<br>FHSYNC          | I/O,<br>LVTTL | <b>Horizontal Sync Input:</b> HSYNC signal for TV out interface. The high/low active state is programmable.                   |

| ROMA15/<br>FVSYNC          | I/O,<br>LVTTL | <b>Vertical Sync Input:</b> VSYNC signal for TV out interface. The high/low active state is programmable.                     |

| ROMA13/<br>FFIELD          | I,<br>LVTTL   | Field Control Input: This signal indicates the field polarity. The polarity is programmable.                                  |

| ROMA12/<br>FBLNK#          | I/O,<br>LVTTL | <b>Composite Blanking Control Output:</b> Indicates active pixels when FBLNK# is negated. FBLNK# is sampled on FCLKOUT edges. |

| ROMA17/<br>FCLKOUT         | O,<br>LVTTL   | TV Pixel Clock Output: Pixel clock sent with data to ensure proper latching of data.                                          |

**NOTE:** The Digital TV Out signals are multiplexed with the BIOS ROM signals.

#### Table 2-8. General Purpose Input/Output Signals

| Pin Name                          | Туре          | Description                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO0<br>(I <sup>2</sup> C Data)  | I/O,<br>LVTTL | <b>General Purpose Input/Output 0:</b> This signal is a standard GPIO signal.<br>However, for Intel board and software driver designs, GPIO0 is used for $I^2C$ data.<br>This signal is tri-stated during a hard reset.                                                                                                                                               |

| GPIO1<br>(I <sup>2</sup> C Clock) | I/O,<br>LVTTL | <b>General Purpose Input/Output 1:</b> This signal is a standard GPIO signal.<br>However, for Intel board and software driver designs, GPIO1 is used for the ${}^{P}C$ clock. This signal is tri-stated during a hard reset.                                                                                                                                          |

| GPIO[3:2]                         | I/O,<br>LVTTL | <b>General Purpose Input/Output [3:0]:</b> These are standard configurable GPIO signals. However, for Intel's board design and software driver design these signals have dedicated uses. See the Display Interface Signal description (Table 2-6) for the dedicated uses of GPIO[3:2].                                                                                |

| GPIO4                             | I/O,<br>LVTTL | <b>General Purpose Input/Output 4:</b> This configurable GPIO signal has added functionality. It has added interrupt functionality such that a high to low transition can trigger an interrupt event. For example, it can be used for thermal fault sensing, or other events that do not occur during powerdown modes. This signal is tri-stated during a hard reset. |

| GPIO5                             | I/0,<br>LVTTL | <b>General Purpose Input/Output 5:</b> GPIO6 is a standard configurable GPIO signal. A suggested use is for Fan Control. This signal is tri-stated during a hard reset.                                                                                                                                                                                               |

| GPIO6                             | I/O,<br>LVTTL | <b>General Purpose Input/Output 6:</b> GPIO6 is a standard configurable GPIO signal.<br>A suggested use is to control the video capture port mux from VMI devices. This signal is tri-stated during a hard reset.                                                                                                                                                     |

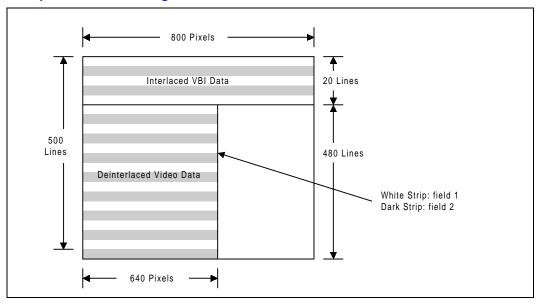

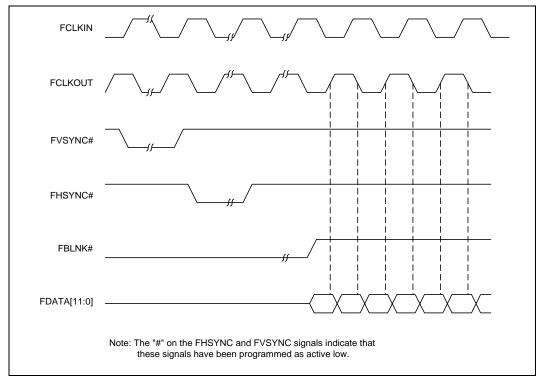

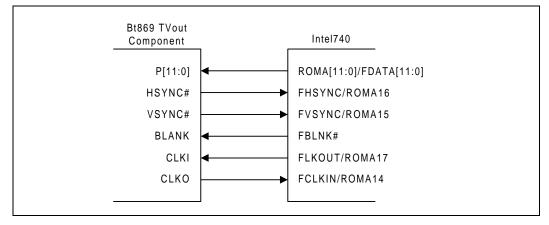

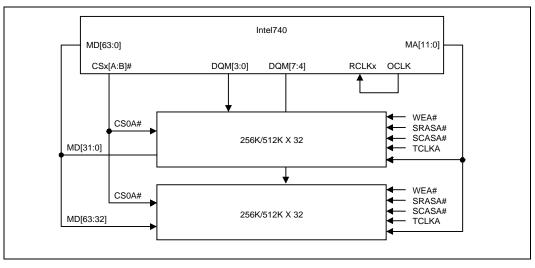

| GPIO7                             | I/0,<br>LVTTL | <b>General Purpose Input/Output 7:</b> GPIO7 is a standard configurable GPIO signal (no added functionality). This signal is tri-stated during a hard reset.                                                                                                                                                                                                          |