## **Modeling Delay**

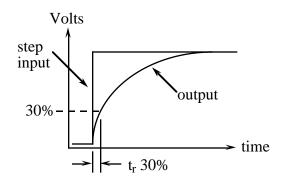

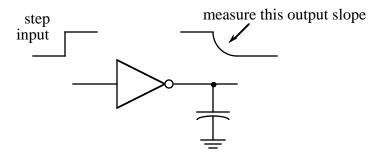

For a <u>step</u> input, then propagation delay simplifies to just rise/fall time of the output to a particular point (50%, 30%/70%, etc.).

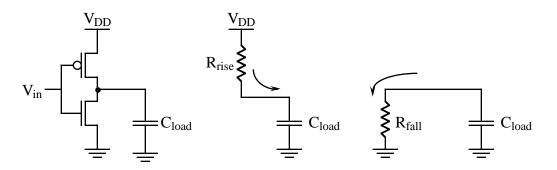

Delay can be modeled in terms of an <u>RC</u> delay:

$$\tau_{rise} = R_{rise} C_{load} \qquad \text{and} \qquad \tau_{fall} = R_{fall} C_{load} \,,$$

for a **particular**  $V_{DD}$ .

Effective Resistance is inversely proportional to ß of transistor.

$$R_{\text{rise}} = k_{\text{rise}} \times \frac{1}{\beta_p}$$

$$R_{\text{fall}} = k_{\text{fall}} \times \frac{1}{\beta_n}$$

How do I determine  $k_{rise}$ ,  $k_{fall}$ ? Do <u>SPICE simulation</u> for a particular C<sub>load</sub>, measure delay, solve for  $k_{rise}$ ,  $k_{fall}$ .

These values of  $k_{rise}$ ,  $k_{fall}$  would be valid for the **particular** V<sub>DD</sub> you used in the simulations.

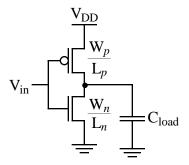

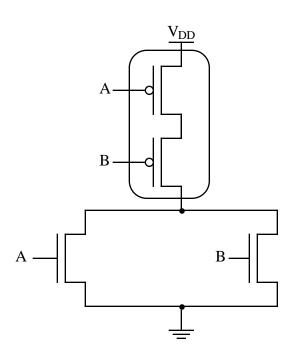

By characterizing an <u>inverter</u> this way, then one can predict delay for more complex gates after transforming the complex gates into an "equivalent" inverter. In this procedure, the original characterized inverter is sometimes called the "base" inverter.

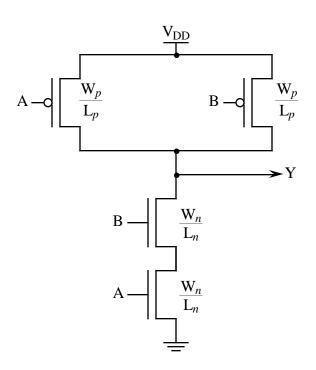

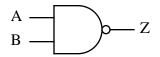

In delay terms (for this NAND), for  $t_{rise}$ , would expect to have the <u>same</u> worst <u>case</u>  $t_{rise}$  as the base inverter because either A or B *p*MOS will pulling.

For  $t_{fall}$ , would expect NAND gate to be twice as slow (as the base inverter) because channel lengths add.

## More accurate delay model breaks gate delay into two <u>parts</u>: $\tau_{internal}$ , $\tau_{output}$

- $\tau_{internal}$  = gate delay with zero load (only internal capacitance values affect delay)

- $\tau_{external}$  = portion of delay proportional to external load.

$$\tau_{\text{gate}} = \tau_{\text{internal}} + k \frac{C_{\text{load}}}{C_{\text{unit load}}};$$

$C_{\text{unit load}} = C_{1x \text{ load}}$

Make SPICE measurement at no load, get  $\tau_{internal}$ .

Make SPICE measurement at unit load (typical output load), determine <u>k</u> value.

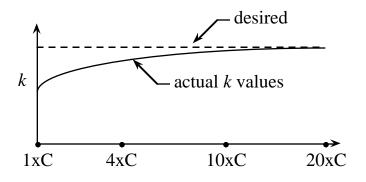

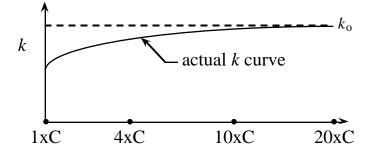

Hopefully, *k* is a constant for different output loads, but <u>may not be</u>.

In this case, take SPICE measurements at different output loads and perform a curve fit of  $\underline{k}$  against C values.

$k = k_0 - \rho[\exp(-C_{norm} \times \alpha)]$

$\Rightarrow$  curve fit and get values for  $k_0$ ,  $\alpha$ ,  $\rho$

$$C_{norm} = \frac{C_{load}}{C_{1x \ load}}$$

Delay calculation:

a) compute k value based on C<sub>load</sub>

b) compute delay value based on k

For a gate, need propagation delay factor for each input, both  $H \rightarrow L$  and  $L \rightarrow H$

T<sub>phl\_a\_to\_z</sub>, T<sub>phl\_b\_to\_z</sub>

T<sub>plh\_a\_to\_z</sub>, T<sub>plh\_b\_to\_z</sub>

Would need  $k_0$ ,  $\alpha$ ,  $\rho$ , and  $\tau_{internal}$  parameters for each one of these

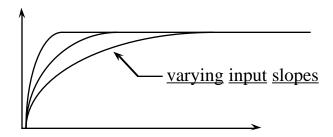

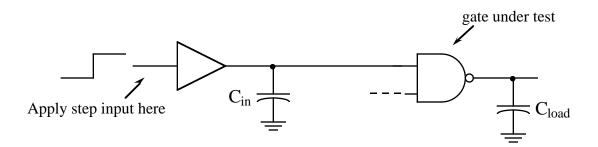

But wait a minute! . . . All of the previous discussion assumed a step input!

Is this realistic? No

Actual waveforms in circuit look something like this:

How do I determine the range of input slopes I might see in a circuit?  $\Rightarrow$  Need to know fastest slope, slowest slope

Fastest case would probably be for the inverter driving a 1x load, pulling down.

- $\Rightarrow$  Measure the output slope. Call it your <u>fastest</u> slope.

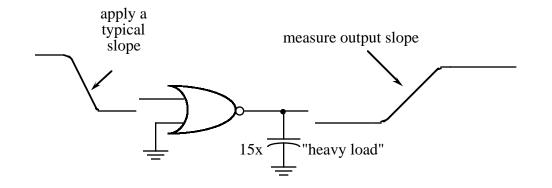

- $\Rightarrow$  Measure again for 4x load and call that your <u>typical</u> slope.

To get a representative "slow" slope, use a 2-input NOR gate pulling high

Why use a NOR gate?

Two *p*MOS's in series will <u>be slow</u>.

Now that you have a <u>fast</u> slope, and <u>slow</u> slope, pick values in between and generate tables of model parameters ( $k_0$ ,  $\alpha$ ,  $\rho$ ,  $\tau_{internal}$ )

For different slopes values — do table lookup based on input slope value.

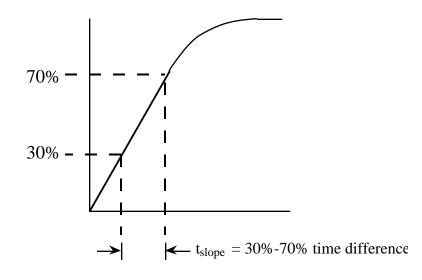

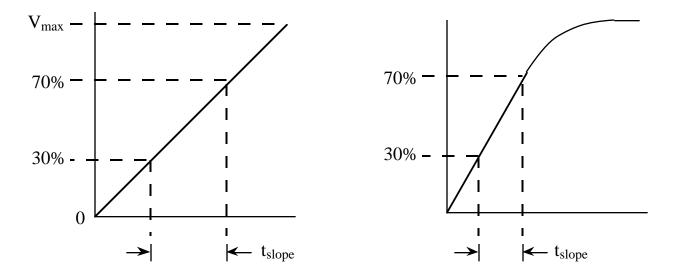

During characterization, I can apply a straight line input (as shown below left)

<u>Not very realistic</u>. Probably want to apply a more realistic waveform (above right).

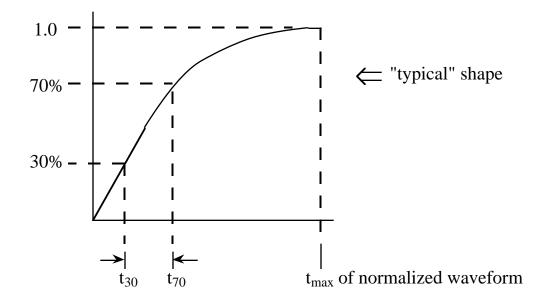

Can have a normalized waveform:

Want to scale this to new waveform based on <u>new</u>  $t_{slope}$

Y<sub>values</sub> scaled by V<sub>DD</sub>.

$\Rightarrow$  new Y<sub>value</sub> = old Y<sub>value</sub> × V<sub>DD</sub>

Xvalue (time) scaling???

$t_{max} = (t_{70} - t_{30}) \times 2.5$

$t_{max_new} = (t_{70_new} - t_{30_new}) \times 2.5$

This last equation (above) implies that given  $t_{70\_new}$  and  $t_{30\_new}$ , *then*  $t_{max\_new}$  can be computed.

Then

$$X_{new} = \frac{X_{old}}{t_{max\_old}} \times t_{max\_new}$$

Nice thing about previous method using a "scaled" waveform is that you can get a desired slope very easily.

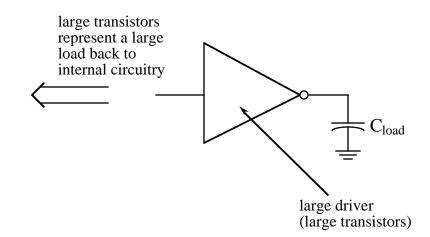

Most realistic waveform is achieved however by having another gate drive the input:

Vary  $C_{in}$  to control input slope. Only problem is that precise control of input slope is difficult, must be able to accurately predict slope of output gate based upon value of " $C_{in}$ ".

This will simulate realistic driving conditions.

## **Stage Ratio - Delay Optimization**

To drive a large load, do not just want to make one large driver

Want to drive the load with a series of progressively larger drivers

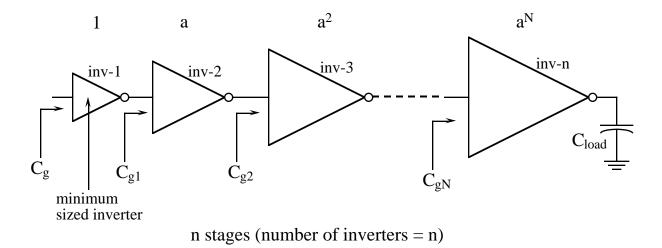

Each driver (inverter) larger than preceding driver by stage ratio "a".

Let  $C_g$  be gate load of first driver which is minimum size. Then,  $C_{gN}$  will be  $C_g \times a^N$  and want

$$C_g a^n \le C_L$$

, [Note:  $n = N + 1$ ]

to guarantee that none of capacitances internal to the chain of inverters exceed  $C_{load}$ . For example, if  $C_{gN} \ge C_{load}$ , why we would need the n-th inverter at all!

So when the condition  $C_g a^n \le C_L$  is set equal we have

$$a^n = \frac{C_L}{C_g} \ .$$

Question: What value of "a" will lead to minimum delay? What value of "n"? If we find one, we can compute the other.

Delay through each stage is approximately  $a \times t_d$  where  $t_d$  is the delay through a minimum-sized inverter driving another minimum-sized inverter.

Total Delay =

$$n \times a \times t_d$$

We know

$$a^n = \left(\frac{C_L}{C_g}\right),$$

SO

$$a = \left(\frac{C_L}{C_g}\right)^{1/n}$$

Substituting,

Total Delay =

$$n \left(\frac{C_L}{C_g}\right)^{1/n} t_d$$

To find optimum value for n, differentiate and set equal to zero.

If we do, then we find

$$n_{opt} = ln\left(\frac{C_L}{C_g}\right)$$

Once we know nopt, find aopt

$$a^{n} = \left(\frac{C_{L}}{C_{g}}\right)$$

$$a^{\ln(C_{L}/C_{g})} = \frac{C_{L}}{C_{g}}$$

Take the natural log (i.e., ln) of both sides:

$$\ln\left(\frac{C_L}{C_g}\right) \times \ln(a) = \ln\left(\frac{C_L}{C_g}\right)$$

$$\ln(a) = 1$$

$$\Rightarrow \quad a = e^1 \approx 2.7 \quad \Leftarrow$$

A more detailed analysis shows that the intrinsic output capacitance of the inverter will affect this ratio.

$$a_{opt} = exp\left(\frac{k + a_{opt}}{a_{opt}}\right)$$

where

$$k = \frac{\mathrm{C}_{\mathrm{drain}}}{\mathrm{C}_{\mathrm{gate}}} \; .$$

Page 190 of text computed

$$C_{drain} = 0.0043 pF$$

,  $C_{gate} = 0.02 pF$  for 1µm process

$$k = \frac{\mathrm{C}_{\mathrm{drain}}}{\mathrm{C}_{\mathrm{gate}}} = 0.215$$

a<sub>opt</sub> = 2.93