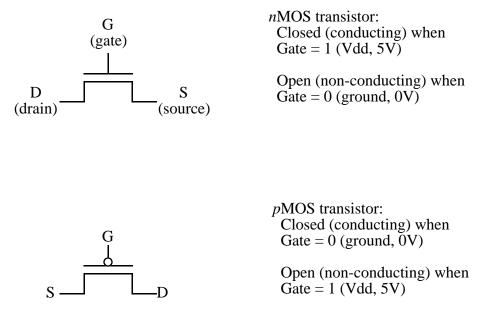

## **MOS Transistors as Switches**

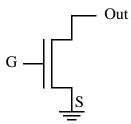

For *n*MOS switch, source is typically tied to ground and is used to *pull-down* signals:

when Gate = 1, Out = 0, (OV) when Gate = 0, Out = Z (high impedance)

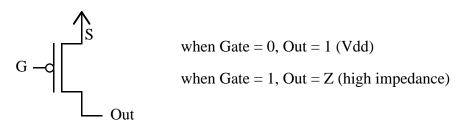

For *p*MOS switch, source is typically tied to Vdd, used to *pull* signals *up*:

Note: The MOS transistor is a symmetric device. This means that the drain and source terminals are interchangeable. For a conducting *n*MOS transistor,  $V_{DS} > 0V$ ; for the *p*MOS transistor,  $V_{DS} < 0V$  (or  $V_{SD} > 0V$ ).

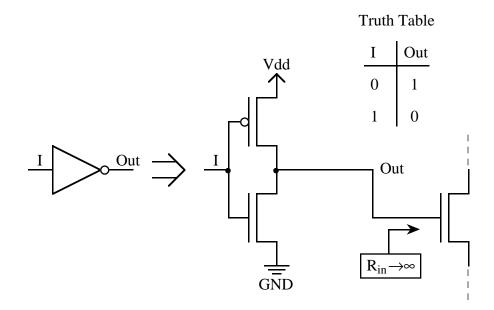

## The CMOS Inverter

Note: Ideally there is <u>no</u> static power dissipation. When "I" is fully is *high* or fully *low*, <u>no</u> current path between Vdd and GND exists (the output is usually tied to the gate of another MOS transistor which has a very high input impedance).

Power is dissipated as "I" transistions from  $0 \rightarrow 1$  and  $1 \rightarrow 0$  and a momentory current path exists between Vdd and GND. Power is also dissipated in the charging and discharging of gate capacitances.

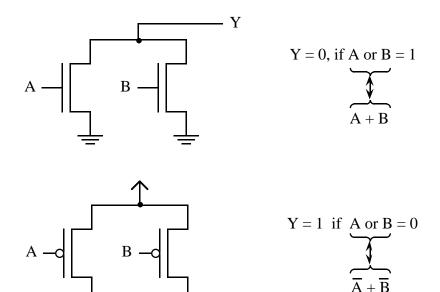

### **Parallel Connection of Switches**

- Y

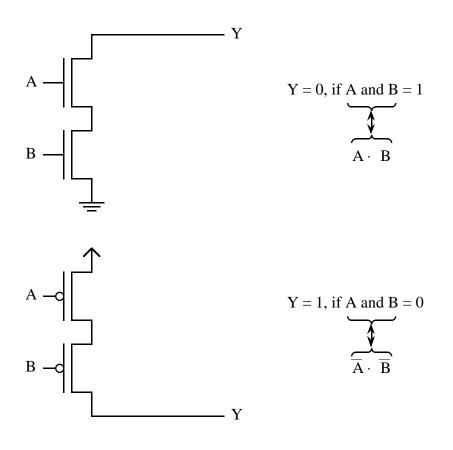

## Series Connection of Switches

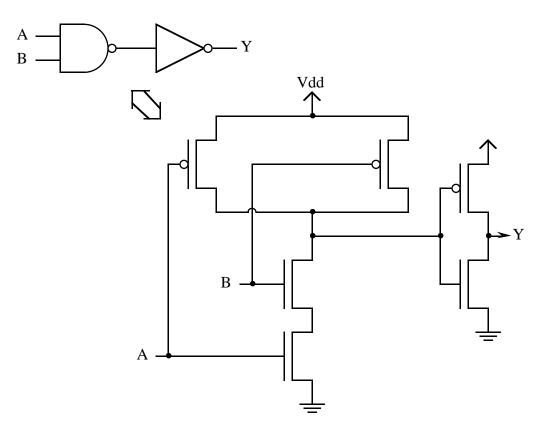

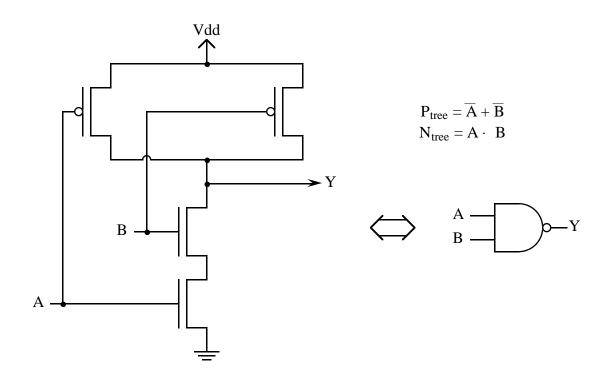

# NAND Gate Design

*p*-type transistor tree will provide "1" values of logic function *n*-type transistor tree will provide "0" values of logic function

Truth Table (NAND):

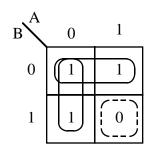

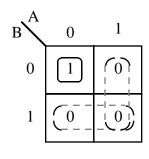

K-map (NAND):

| AB |   |

|----|---|

| 00 | 1 |

| 01 | 1 |

| 10 | 1 |

| 11 | 0 |

NAND circuit example:

#### August 25, 1998

#### page 5

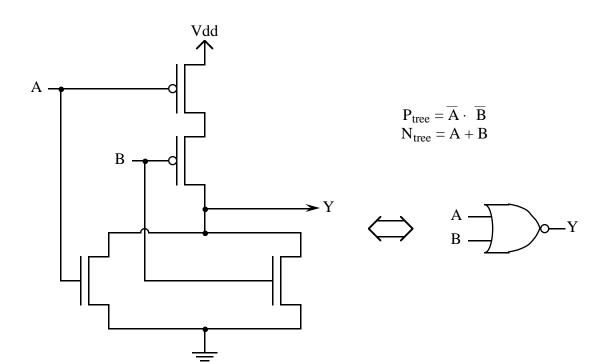

## NOR Gate Design

*p*-type transistor tree will provide "1" values of logic function *n*-type transistor tree will provide "0" values of logic function

Truth Table:

K-map:

| AB |   |

|----|---|

| 00 | 1 |

| 01 | 0 |

| 10 | 0 |

| 11 | 0 |

NOR circuit example:

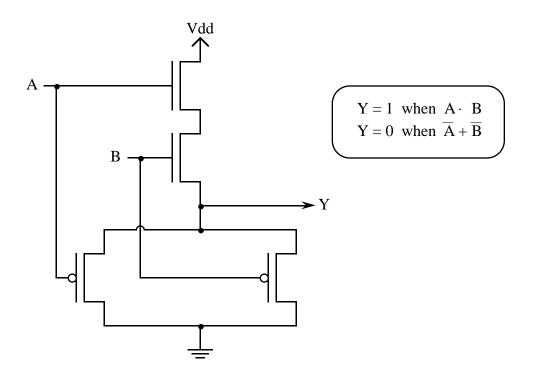

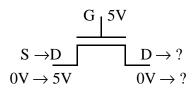

### What logic gate is this?

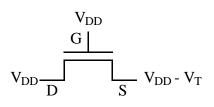

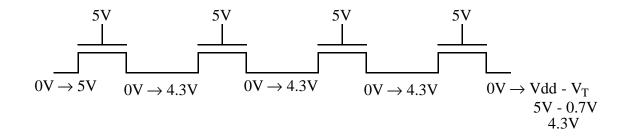

where  $V_T = 0.7V$  to 1.0V (i.e., threshold voltage will vary) output voltage = 4.3V to 4.0V, a *weak* "<u>1</u>" The *n*MOS transistor will stop conducting if  $V_{GS} < V_T$ . Let  $V_T = 0.7V$ ,

As source goes from  $0V \rightarrow 5V$ ,  $V_{GS}$  goes from  $5V \rightarrow 0V$ .

When  $V_S > 4.3V$ , then  $V_{GS} < V_T$ , so switch stops conducting.

$V_D$  left at 5V -  $V_T$  = 5V - 0.7V = 4.3V or Vdd -  $V_T$ .

What about *n*MOS in series?

Only one threshold voltage drop across series of nMOS transistors

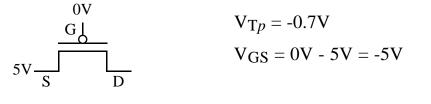

# For *p*MOS transistor, $V_T$ is <u>negative</u>. *p*MOS transistor will conduct if $|V_{GS}| > |V_{Tp}|$ ( $V_{SG} > |V_{Tp}|$ ), or $V_{GS} < V_{Tp}$

August 25, 1998

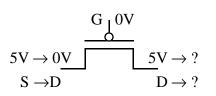

How will *p*MOS pass a "0"?

conducting

When  $|V_{GS}| < |V_{Tp}|$ , stop conducting

$V_{GS} < V_{Tp}$  or  $|V_{GS}| > |V_{Tp}|$

-5V < -0.7V 5V > 0.7V

So when  $|V_{GS}| < |-0.7V|$ ,  $V_D$  will go from  $5V \rightarrow 0.7V$ , a weak "<u>0</u>"

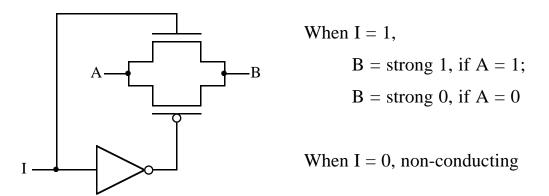

How are both a strong "1" and a strong "0" passed?

Transmission gate pass transistor configuration

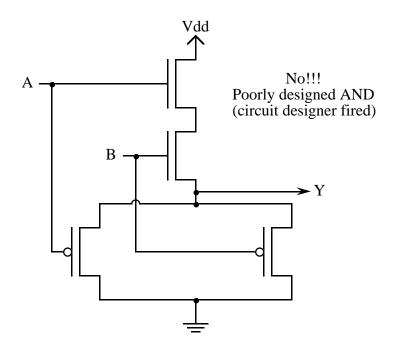

# About that AND Gate...

Instead use this,