## Agenda

- Trends in medical applications

- Role of PCI Express

- Altera® PCI Express solution

- PCI Express demo

CY2

### **Medical Sub-Segments**

- Diagnostic imaging

- Ultrasound (US)

- Computed tomography (CT)

- Magnetic resonance imaging (MRI)

- Positron emission tomography (PET)

- X-ray

- Electro-medical

- Patient monitoring

- Ventilation and life support

- Anesthesia

- Cardiac rhythm management (CRM)

- Automatic external defibrillators (AED)

- Pacing systems

- Implantable cardiac defibrillators (ICD)

- Other medical lab equipment

- Scientific and lab instrumentation

- Radiation

**AED**

Blood Analysis Centrifuge

# **Diagnostic Imaging Trends**

| Modality    | Trend                                                                                                       |  |

|-------------|-------------------------------------------------------------------------------------------------------------|--|

| All         | Trend towards digital imaging - higher resolution and 3-D imaging  Increased amount of high-speed filtering |  |

|             | Trend towards serial backplanes                                                                             |  |

|             | Portable imaging has potential to reach wider customer base                                                 |  |

| СТ          | Single slice to multi-slice                                                                                 |  |

| MRI         | Higher Tesla (T) based systems                                                                              |  |

| Ultrasound  | Higher growth rates in developing nations due to lower system costs                                         |  |

| X-ray       | Higher growth rates in developing nations due to lower system costs                                         |  |

| CT and PET  | Evolution of combined modalities                                                                            |  |

| Nuclear/PET | The fastest growing modality – '03-'08 compound annual growth rate (CAGR) of 12%                            |  |

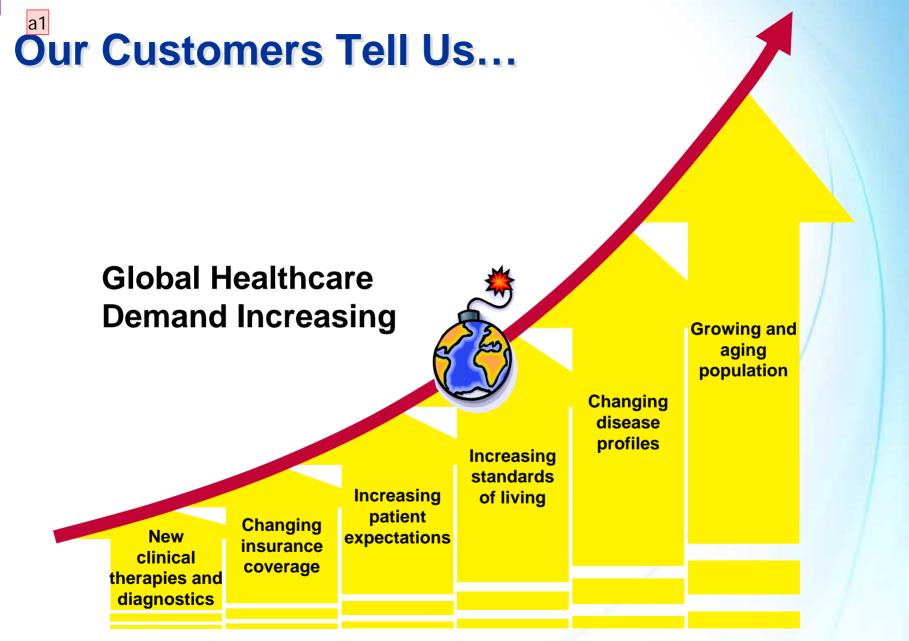

### **Our Customers Tell Us...**

**Healthcare Providers Driving Towards:**

### **Medical OEM** solutions

- Handheld and portable form factors

- **Flexible**

- Modular

- Cost-effective

solutions

Connectivity

# **Product Development Trends**

- Market dynamics drive focus on differentiating via software and firmware

- Common hardware architectures are emerging:

- a. Chassis-based, premium systems

- b. Modular-based, mid-range systems

- c. Handheld, value systems

- Architectural building blocks becoming standardized

Co-processing

Add-on features

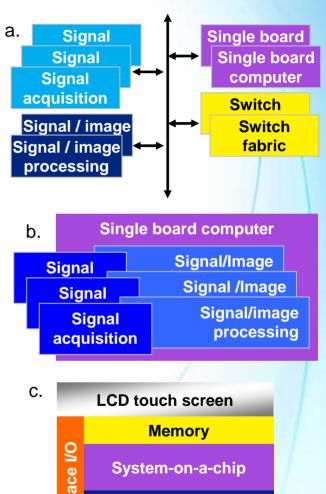

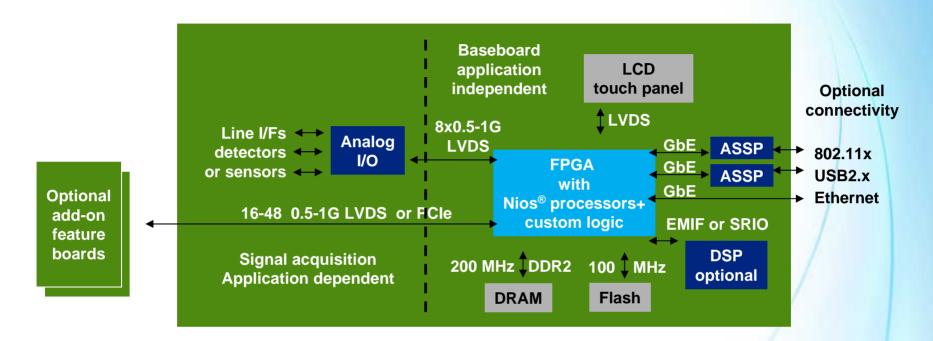

## **Three Emerging Platforms**

### Chassis

- Leveraging PCIe/GbE for backplane interconnect

- High-end medical imaging

### Modular

- Leveraging SBCs for software convenience and COTS hardware

- Patient monitoring, ultrasound, x-ray

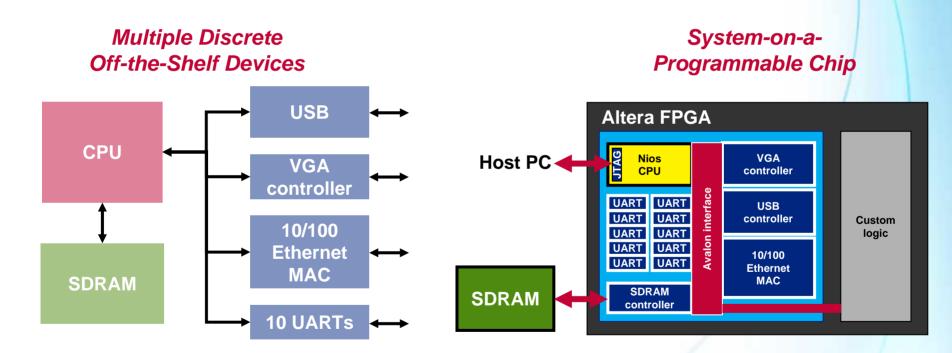

### Handheld

- Leveraging system-on-a-programmable-chip (SOPC)

FPGAs

- Low-end patient monitoring/ultrasound

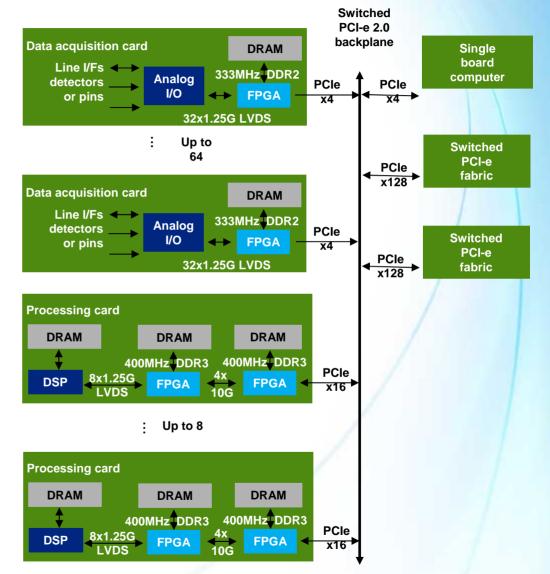

## T&M Chassis System in 2008

- Asymmetric data flow

- Scalable to smaller chassis

- Applications:

- High-end medical imaging

- CT, MR, PET

- Devices:

- Acquisition: Cyclone<sup>®</sup> III FPGAs

- Processing: Stratix<sup>®</sup> III FPGAs

- Configuration and BIST: MAX® III **CPLDs**

- Competition:

- FPGAs, ASICs, digital signal processing (DSP) devices

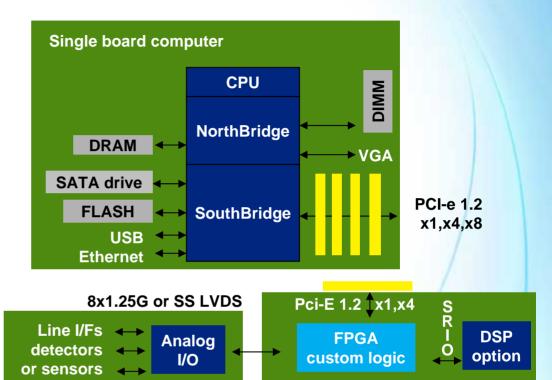

# T&M Modular System in 2008

- Stackable modules

- Applications:

- Mobile equipment

- Patient monitoring

- Endoscopes

- Ultrasound, x-ray

- Devices:

- Low end: Cyclone III FPGAs

- Stackable: Stratix III FPGAs

- Configuration and BIST:

MAX III CPLDs

- Competition:

- GPPs, DSP devices, FPGAs, ASICs

**Application dependent**

· Signal interface

IF daughterboards

**Application independent**

**PCIe FPGA board**

100 MHz 300 MHz DDR2

**DRAM**

Signal acquisition

Flash

Signal processing

### **T&M Handheld Devices in 2008**

### Applications:

Low-end patient monitoring, portable ultrasound, endoscopes

#### Device:

Mid-range: Cyclone III; High-end: HardCopy® III, MPU, configuration and BIST: MAX III

### Competition:

Low-end: MCUs, DSP devices, ASICs

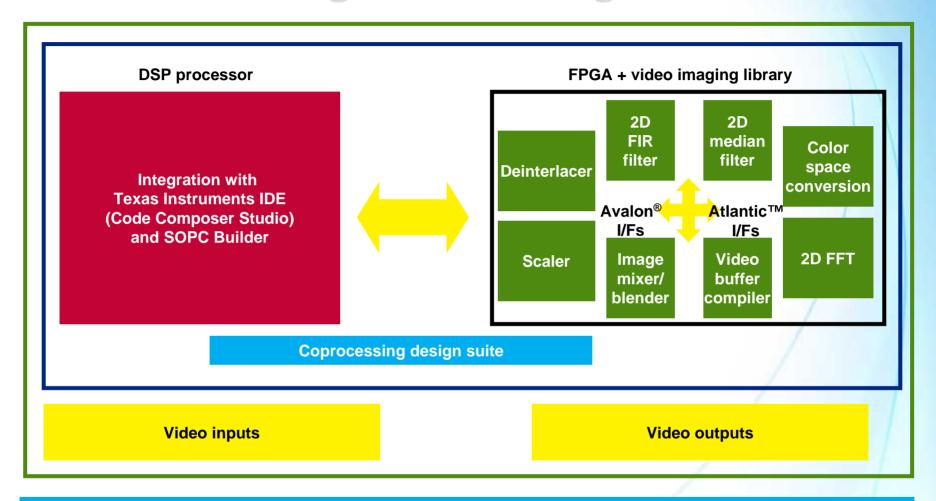

# Video and Image Processing Suite

Video hardware platforms – development kits and reference designs

### **Deliver Faster Results and Lower Cost**

Use Nios II embedded processor and SOPC Builder for system integration

1 Quarter Saved on Two-Year Project!

### **Complete Memory Solutions**

#### **Advanced FPGA Architecture**

- DQS phase shift circuitry

- Six registers in I/Os

- Feature-rich PLLs and clock management

# Development Kits and Hardware Reference Platforms

- Demo project

- Board design guidelines

- Schematic and Gerber files

# Memory Controller MegaCore® intellectual property (IP)

- Open source datapath

- Reference designs

- GUI

- Included in the free IP base suite

### **Software Support**

- Automatic generated constraints

- System-level timing analysis

- SPICE and IBIS simulation models

### Device Handbook, Application Note

- Interface description

- Timing analysis

- Electrical analysis

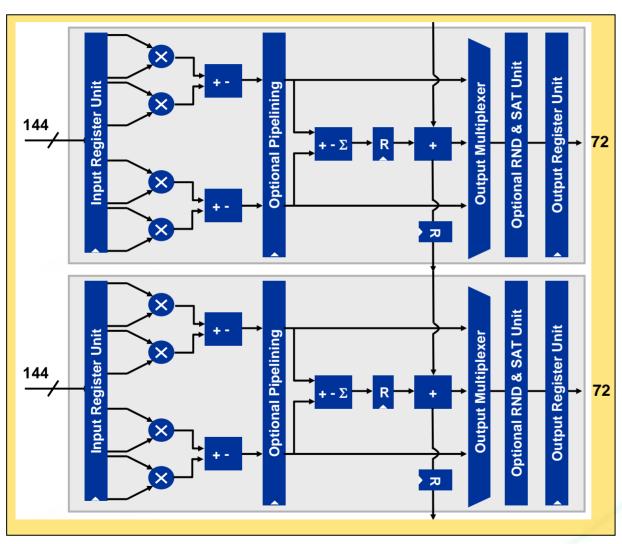

## **DSP Blocks for DSP Algorithms**

- Basic multiplier modes

- -8x(9x9)

- 6 x (12x12)

- 4 x (18x18)

- 2 x (36x36)

- 2 x complex (18x18)

- Sum modes

- 4 x sum of two (18x18)

- 2 x sum of four (18x18)

- Accumulation

- 2 x Acc

- Cascade modes

- Input cascade

- Output cascade

- Rounding

- Unbiased and biased

- Saturation

- Asymmetrical and symmetrical

- Barrel shifter

- Arithmetic, logical, and rotational

## **External Memory Interfaces**

Stratix III FPGAs are the only FPGAs in the industry to offer DDR3 interfaces

|              | Device family   |                                          |

|--------------|-----------------|------------------------------------------|

|              |                 | Stratix II FPGAs/<br>Stratix II GX FPGAs |

| Interconnect | Performance* ** | Performance                              |

| DDRIII       | 400 MHz         | N/A                                      |

| DDRII        | 400 MHz         | 333 MHz                                  |

| QDR II       | 350 MHz         | 300 MHz                                  |

| QDR II+      | 400 MHz         | N/A                                      |

| RLDRAM II    | 400 MHz         | 300 MHz                                  |

<sup>\*\*</sup> Pending Characterization

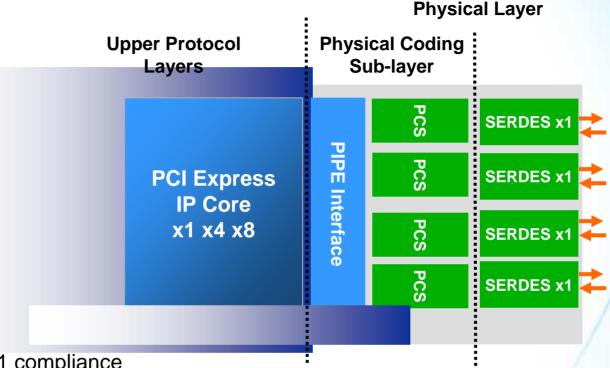

# PCI Express Configuration (x1, x4, x8)

© 2007 Altera Corporation—Public

# **Altera PCI Express Solutions**

- Complete, easy-to-use PCI Express solutions

- x1, x4 and x8 endpoints

- Industry-leading design flow with Altera IP MegaCore function

- Stratix II GX, Cyclone II, Stratix II, HardCopy II, and Stratix GX device family support

- Low-risk, hardware-verified solutions

- Device characterization and PCI-SIG compliance workshops

- 2 generations of FPGAs with embedded transceivers

- Stratix GX FPGAs passed PCI-SIG compliance

- Stratix II GX FPGAs passed PCI-SIG compliance

- Development/demo boards

### Fastest Time-To-Market with a Reliable PCI Express Endpoint Solution

## **PCI-SIG Compliance and Interoperability**

| Motherboard vendor | Result |

|--------------------|--------|

| Intel              | Passed |

| HP                 | Passed |

| IBM                | Passed |

| ATI                | Passed |

| nVidia             | Passed |

| VIA                | Passed |

| Bridge/switch tested | Result |

|----------------------|--------|

| PLX                  | Passed |

| IDT                  | Passed |

| Test equipment vendor    | Result |

|--------------------------|--------|

| Wavecrest                | Passed |

| Agilent                  | Passed |

| Catalyst                 | Passed |

| Tektronix                | Passed |

| VMETRO                   | Passed |

| Intel                    | Passed |

| LeCroy                   | Passed |

| Interoperability         | Result |

| Freescale PowerQUICC III | Passed |

| IDT Switches             | Passed |

### Passed all the PCI-SIG Gold-Suite Compliance Tests with 100% Pass Rate

### Reliability - Interoperability

- Partnered with Freescale to create and present joint working **PCI** Express solution

- Demonstrated Freescale PowerQUICC III-to-Altera Stratix II GX interoperation

- Verified working PCI Express interface for up to 8 lanes

| Freescale                   | Altera             |

|-----------------------------|--------------------|

| MPC8548E                    |                    |

| MPC8547E                    |                    |

| MPC8545E                    | Stratix II GX FPGA |

| MPC8543E                    |                    |

| MPC8641                     |                    |

| MPC8641D                    |                    |

| MPC8572E and future MPC85xx |                    |

| processors with PCI Express |                    |

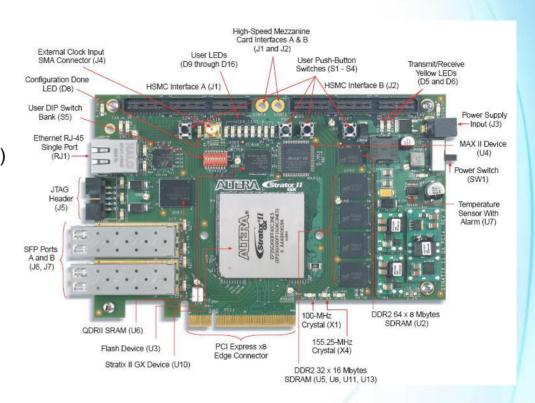

### **PCle Board**

- EP2SGX90FF1508

- x8 PCI Express

- DDRII

- 72 bit, 333 MHz

- **QDRII**

- 36 bit, 300 MHz (350-MHz QDRII+)

- 2x SFP ports

- JTAG header

- 10/100/1G Ethernet

- 2x mezzanine connector

- Up to 84 LVDS

- Up to 6 transceivers

- Up to 3 clocks

- SMA clock input

- PCI Express Development Kit Stratix II GX Edition DK-PCIE-2SGX90N (US \$2,995)

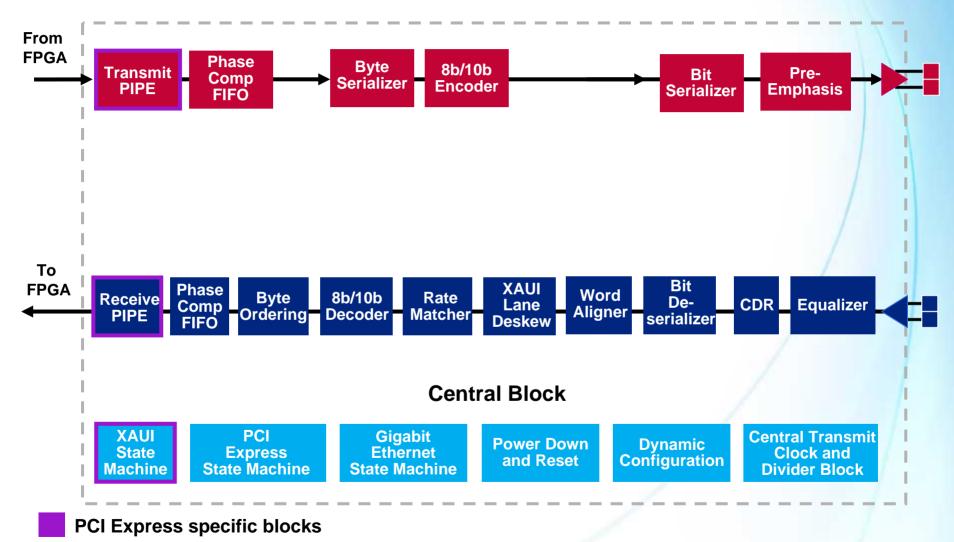

### **PCI Express IP Core**

- PCI Express 1.1 compliance

- Support for up to 4 virtual channels (VCs)

- Configurable maximum payload up to 2 Kbytes

- 128, 256, 512, 1024, or 2048 bytes

- Configurable retry buffer

- Optional end-to-end cyclic redundancy code (ECRC) generation/checking

- Optional advanced error reporting (AER)

- Flexible reference clock support (100, 125, or 156.25 MHz)

# **Summary**

- PCI Express adopted in current and next generation medical systems

- Altera FPGAs provide comprehensive support for PCI **Express**

- Arria<sup>™</sup> GX FPGAs for mainstream applications

- Stratix II GX FPGAs for emerging high-performance applications

- Altera PCI Express solution proven in real systems

- Complete PCI-SIG compliance

- Characterization reports, development kits