## **Agenda**

- Digital IF modem applications overview

- FPGA as a digital IF modem solution

- Live demo

- Conclusions

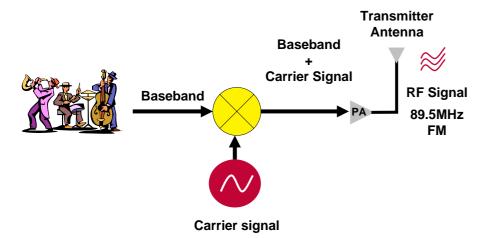

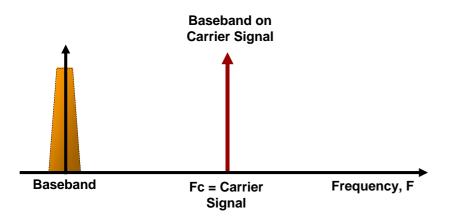

## **Digital IF Modem Defined**

- **IF**: [from Wikipedia] An intermediate frequency (IF) is a <u>frequency</u> to which a <u>carrier frequency</u> is shifted as an intermediate step in <u>transmission</u> or <u>reception</u>

- Digital IF modem: A <u>device</u> that processes IF signals in their <u>digital representations</u> with <u>digital methods</u>

## **Background**

## **Background**

## **Digital IF Market Applications**

## Cellular communication

- Global System for Mobile Communications (GSM)

- W-CDMA

- Code Division Multiple Access-2000 (CDMA-2000)

- EVD

- Long-term evolution (LTE)

#### Video broadcast

Digital video broadcast (DVB) – H/T/S modulators and demodulators

## Military secure communication

- Field sensors

- Hand-held/portable radios

- Military global positioning system (GPS)

- Military radios

- Satellite

- Radar/sonar

### Medical instrument

- Computed tomography (CT) scan

- Ultrasound

- Magnetic resonance imaging (MRI)

- Medical wireless instruments

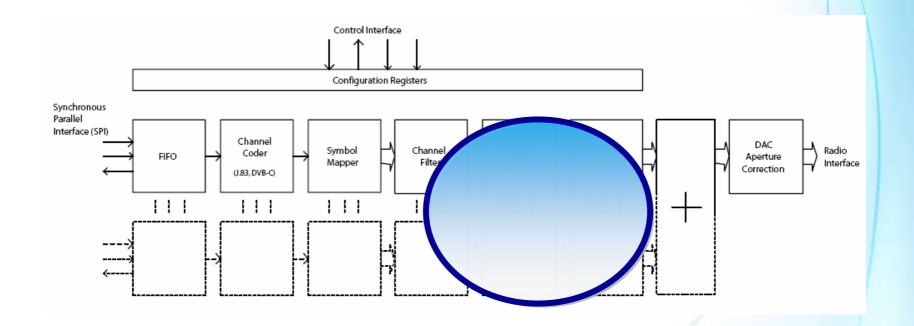

## **Application Example #1: Cable Modulator**

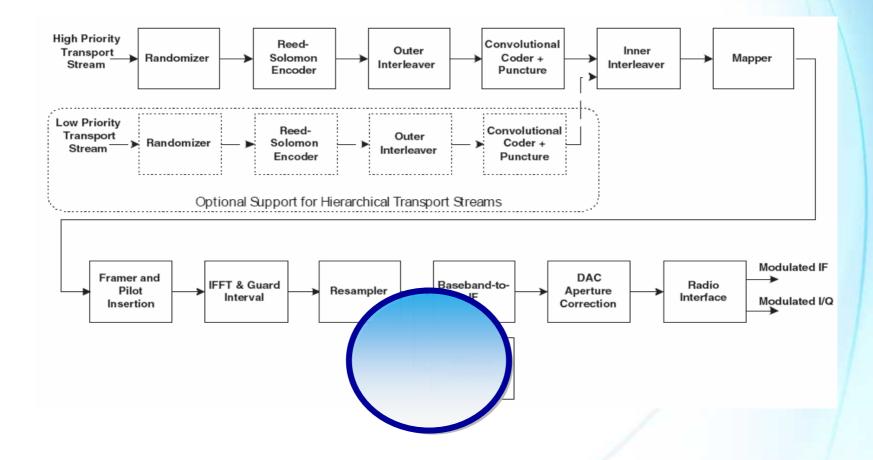

## **Application Example #2: DVB-T/H/S**

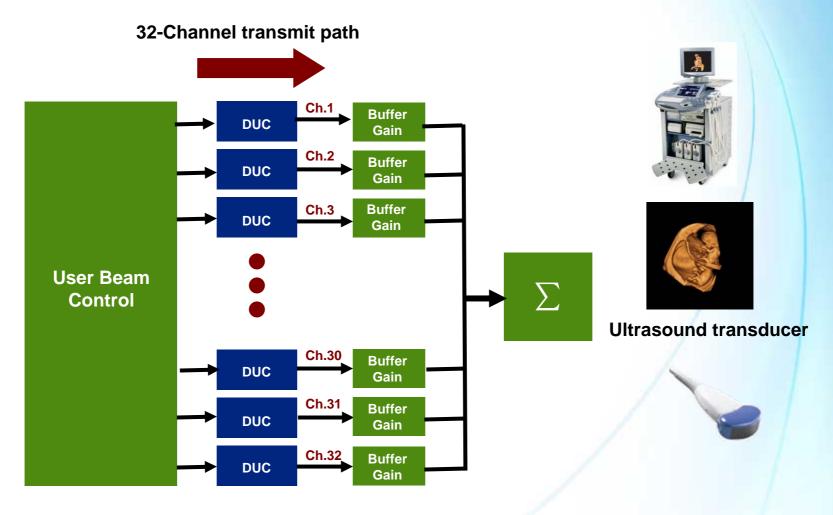

## **Application Example #3: Medical Ultrasound**

**Comprehensive Altera solution**

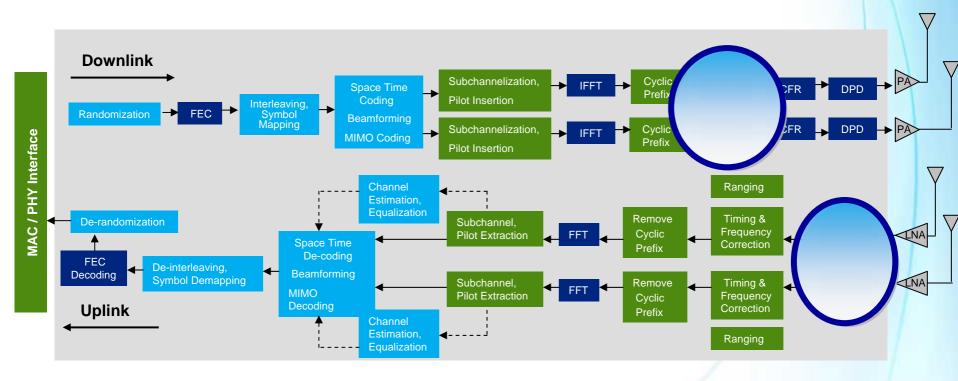

## Application Example #4: WiMAX Orthogonal Frequency Division Multiplexing (OFDM) Engine

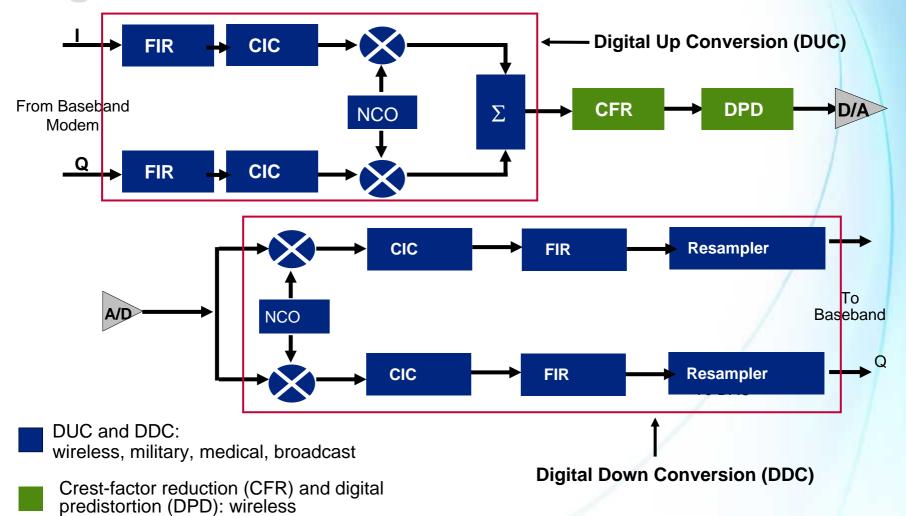

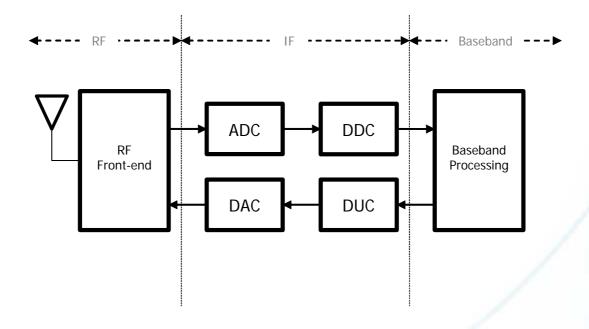

## High-Level Block Diagrams of a Typical Digital IF Modem

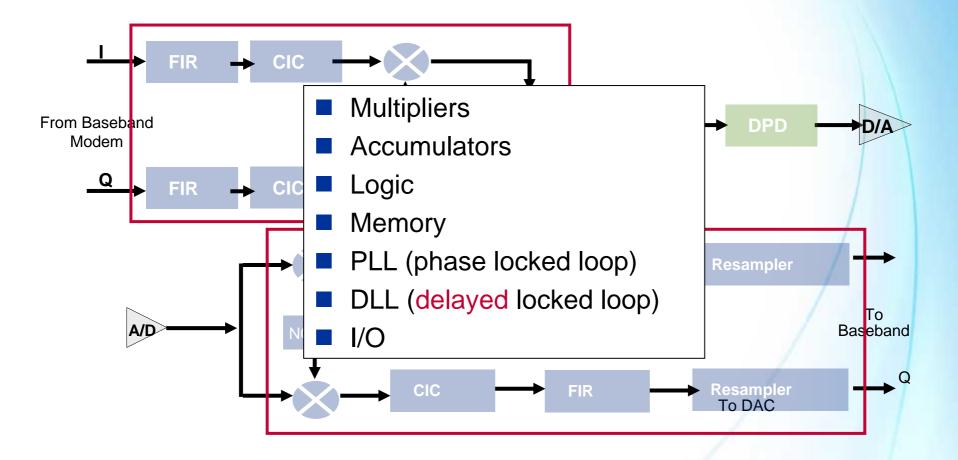

## To Build These With an FPGA, We Need...

#### Other Considerations...

### FPGA is Ideal for Digital IF Functions Because...

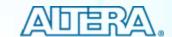

- Abundance of resources for building IF functions

- Logic: up to 338K logic elements (LEs) and 270K registers

- Digital signal processing (DSP): up to 896 18X18 multipliers

- Memory: up to 17.2 Mbits of 600-MHz memory

- PLLs, DLLs: numerous located across the device for ease of clock management

- I/O: support for wide varieties of singleended and differential I/O standards

- Latest manufacturing process (e.g. 65 nm) + state-of-the-art design software tools for

- Low power

- Low cost

- Ease of design

## **Example: WiMAX PHY Layer Implementation**

|                                    |                                                       | LEs    | Number of M9K<br>memory blocks | 18x18<br>multipliers | Power<br>(watts) |

|------------------------------------|-------------------------------------------------------|--------|--------------------------------|----------------------|------------------|

| IF processing                      | WiMAX DUC                                             | 2,704  | 50                             | 30                   | 0.40             |

|                                    | WiMAX DDC                                             | 2,623  | 46                             | 25                   | 0.40             |

| OFDMA<br>symbol-rate<br>processing | DL OFDMA engine                                       | 4,176  | 33                             | 4                    | 0.25             |

|                                    | UL OFDMA engine                                       | 3,834  | 57                             | 4                    | 0.25             |

|                                    | Channel estimation and equalization                   | 7,400  | 1                              | 4                    | 0.33             |

| Bit-rate<br>processing             | Symbol mapper and demapper                            | 1,404  | 3                              | 0                    | 0.10             |

|                                    | Forward error correction (FEC, encoding and decoding) | 18,511 | 26                             | 0                    | 0.60             |

|                                    | Total percentage of Cyclone® III EP3C55 resources     | 77%    | 83%                            | 43%                  | 2.33             |

## **Altera DSP Development Kits**

QUARTUS® II

Contains Everything You Need to Develop High-Performance DSP Designs on FPGAs

### 30-Day evaluation version

System reference designs

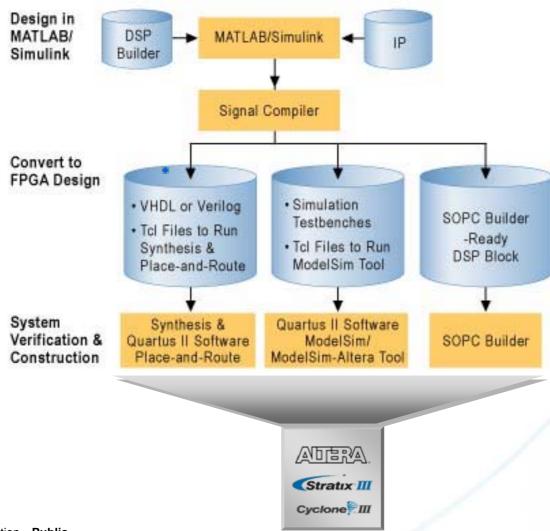

## **DSP Builder and Simulink Design Flow**

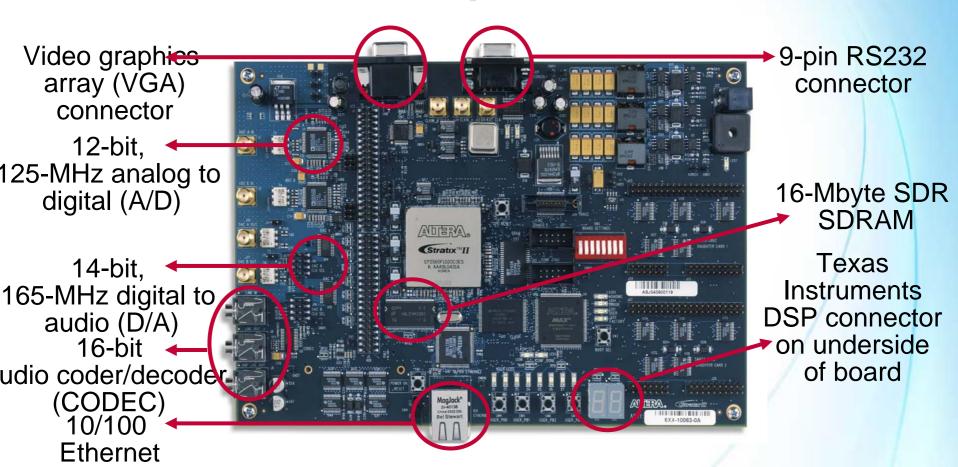

## **Stratix II DSP Development Board**

### Cyclone III Edition Available Soon

#### Conclusion

- FPGAs deliver low power, high performance, and costefficient digital IF functions to enable customers' innovation

- Innovative DSP design tool flow improves productivity

- DUC and DDC application demo example

- Design methodology significantly reduces the development time for different standards

- Highly optimized and cost-efficient designs

# Visit Altera's DSP Solution Center at <a href="http://www.altera.com/dsp">http://www.altera.com/dsp</a>

#### **Live Demo**

- DDC/DUC reference design

- DSP Builder

## Reference Design Overview

#### DUC/DDC

- Provides the link between digital baseband and analog RF front end of generic transceiver

- High-throughput signal processing required makes FPGA ideal platform

- Compliant to the draft WiMAX standard (IEEE 802.16)

- Multi-channel filter design for low cost

- Support for multiple transmit and receive antenna configurations

- Easily modifiable to support scalable channel bandwidths

- Uses DSP Builder methodology

- Backed up by DSP Builder-ready, highly parameterizable intellectual property (IP) MegaCore<sup>®</sup> functions

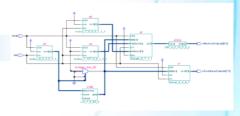

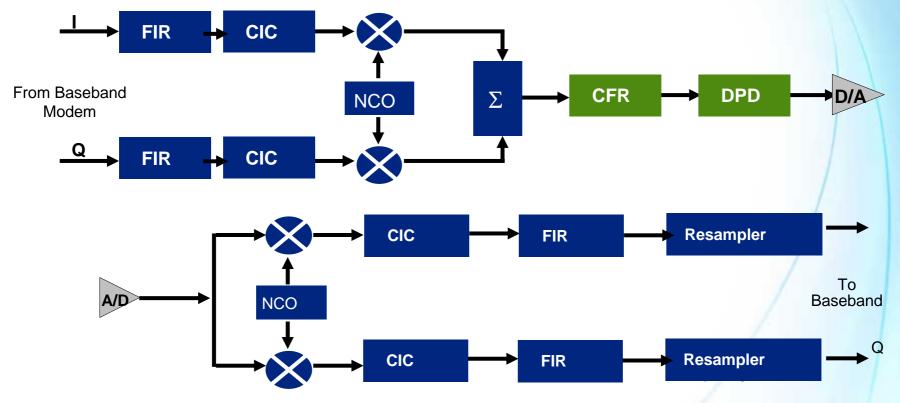

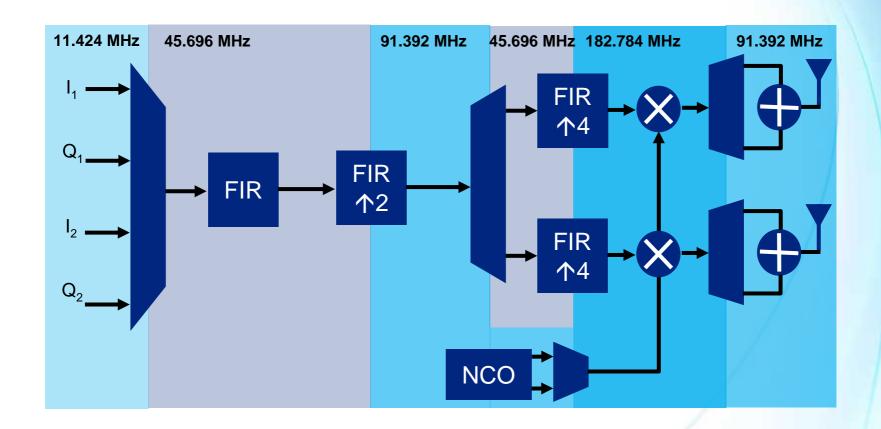

## **DUC and DDC High-Level Block Diagrams**

- DUC and DDC: wireless, military, medical, broadcast

- Crest-factor reduction (CFR) and digital predistortion (DPD): wireless

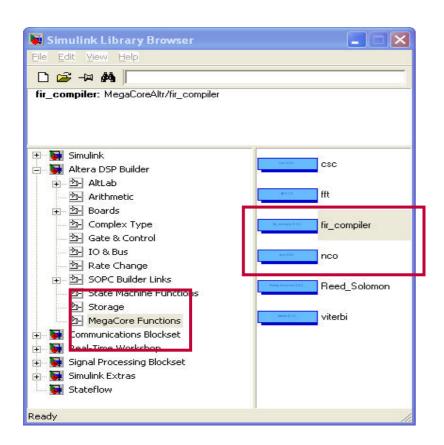

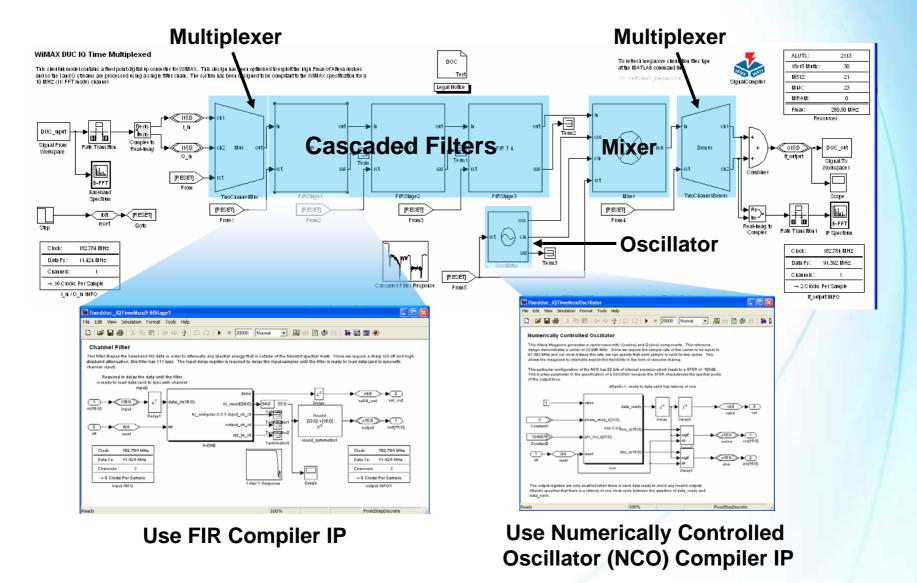

### DSP Builder Implementation: IP MegaCore Library

## IP Can Be Added to the Library Separately

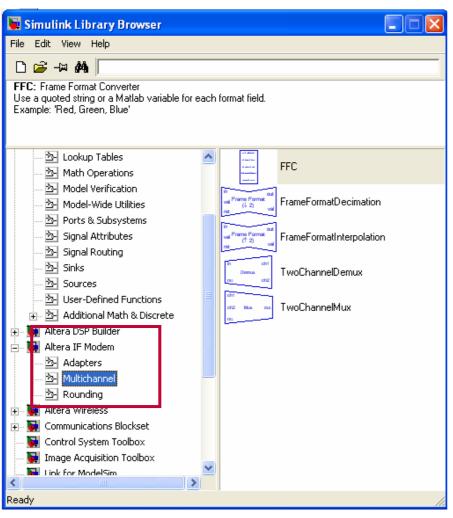

# DSP Builder Implementation: Digital Intermediate Frequency (IF) Library

- Adapters

- Provide input/output interface to finite impulse response (FIR) filter

- Multichannel

- Frame format converter

- Decimation

- Interpolation

- Multiplexer

- Demultiplexer

- Rounding

## **DUC With 2 Antennas – Design Architecture**

#### Timeshare DUC Hardware Between Antennas

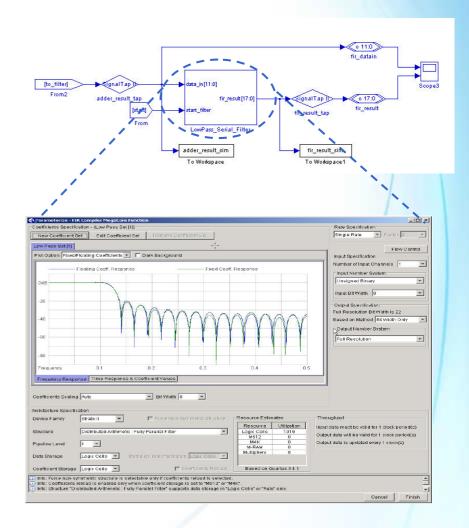

#### **DSP Builder Implementation: DUC Example Design With 2 Antennas**

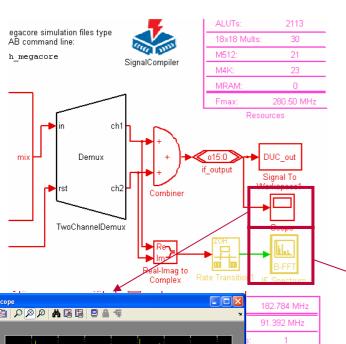

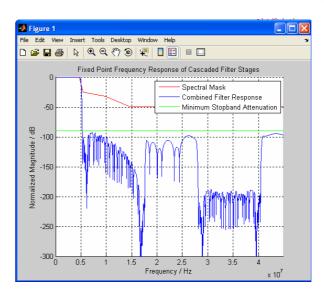

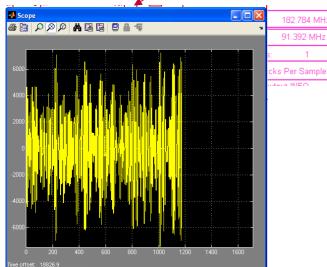

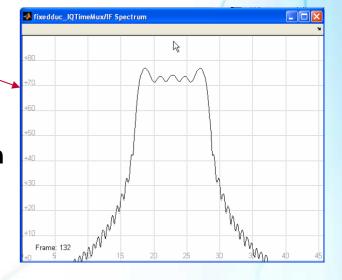

#### **Simulation**

## Cascaded Filter Output

**After Upconversion**

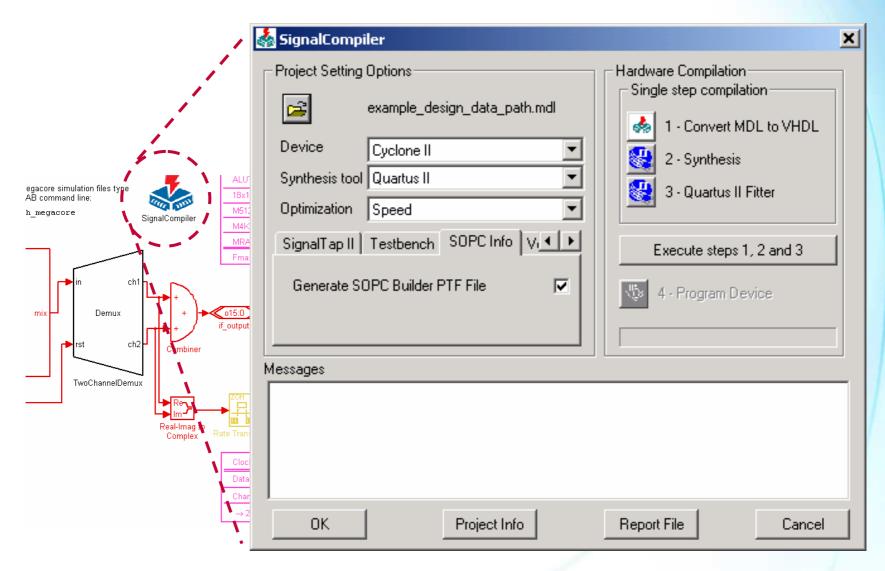

## Convert to VHDL: SignalCompiler

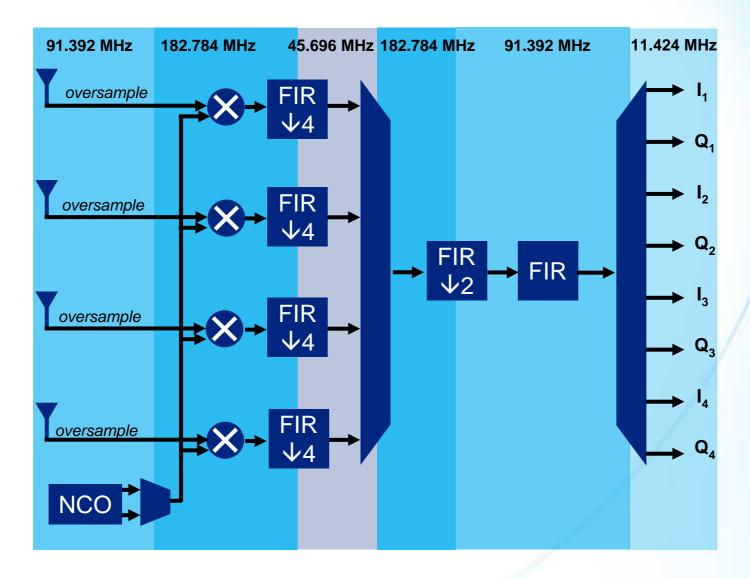

#### **DDC With 4 Antennas – Design Architecture**

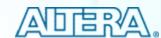

# DSP Builder Implementation: DDC Example Design With 4 Antennas

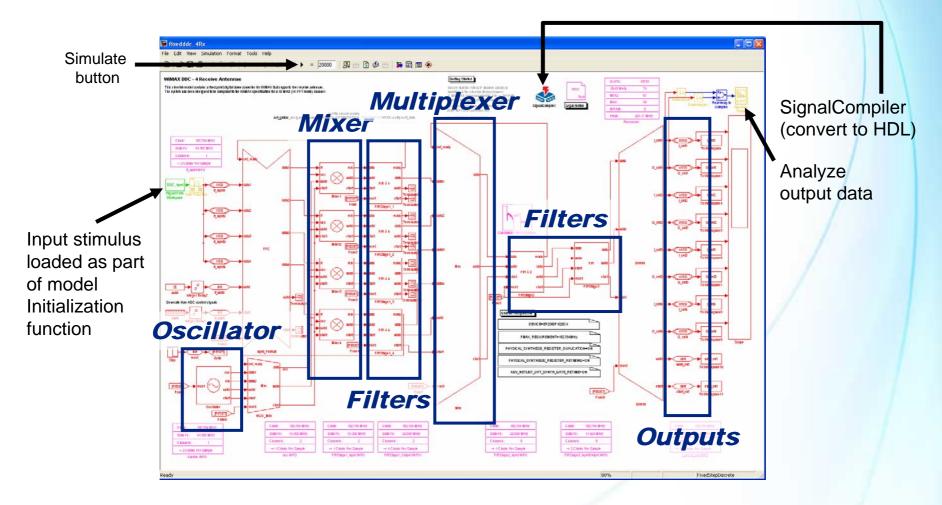

#### **2xRx DDC Architecture**

## **DUC and DDC Synthesis Results**

| Adaptive<br>look-up<br>tables<br>(ALUTs) | M512 | M4K | MRAM | Multipliers<br>18x18 | f <sub>max</sub><br>MHz |  |  |  |

|------------------------------------------|------|-----|------|----------------------|-------------------------|--|--|--|

| DUC Time Multiplexed IQ Design           |      |     |      |                      |                         |  |  |  |

| 2,113                                    | 21   | 23  | 0    | 30                   | 281                     |  |  |  |

| DUC 2 Antenna Design                     |      |     |      |                      |                         |  |  |  |

| 4,229                                    | 21   | 56  | 0    | 55                   | 193                     |  |  |  |

| DDC Time Multiplexed IQ Design           |      |     |      |                      |                         |  |  |  |

| 2,488                                    | 19   | 22  | 0    | 25                   | 293                     |  |  |  |

| DDC 4 Antenna Design                     |      |     |      |                      |                         |  |  |  |

| 10,753                                   | 67   | 69  | 0    | 74                   | 201                     |  |  |  |

## Highly Optimized and Cost Efficient Designs! More Information at www.altera.com