# Synopsys<sub>®</sub>

# Synthesis Methodology Guide

## Actel Corporation, Sunnyvale, CA 94086

© 1998 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 5579009-2

Release: April 1999

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Actel Corporation.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent from Actel Corporation.

#### Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

Adobe and Acrobat Reader are registered trademarks of Adobe Systems, Inc.

Cadence is a registered trademark of Cadence Design Systems, Inc.

Mentor Graphics is registered trademark of Mentor Graphics, Inc.

Synopsys, Design Compiler, VHDL Compiler, HDL Compiler, and Library Compiler are trademarks or registered trademarks of Synopsys, Inc.

UNIX is a registered trademark of X/Open Company Limited.

Verilog is a registered trademark of Open Verilog International.

Viewlogic is a registered trademark and MOTIVE is a trademark of Viewlogic Systems, Inc.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

# **Table of Contents**

|   | Introduction x                          |

|---|-----------------------------------------|

|   | Document Organization x                 |

|   | Document Assumptions xi                 |

|   | Document Conventions xi                 |

|   | HDL Keywords and Naming Conventions xii |

|   | Actel Manuals                           |

|   | On-Line Help xvii                       |

| 1 | Setup                                   |

|   | Software Requirements                   |

|   | System Setup                            |

|   | User Setup                              |

| 2 | Actel-Synopsys Design Flow              |

|   | Design Flow Illustrated                 |

|   | Design Flow Overview                    |

| 3 | Actel-Synopsys Coding Considerations    |

|   | Multiplexer Encoding                    |

|   | Finite State Machine Design             |

|   | DesignWare Module Coding                |

| 4 | Synthesis Constraints                   |

|   | Operating Conditions                    |

|   | Design Constraints                      |

|   | Design Hierarchy                        |

|   | Internal Tri-State                      |

|   | Inferring Buffers                       |

|   | Reducing the Maximum Fanout Value 62    |

|   | Register Type Preferences               |

|   | Avoid Using Certain Cells               |

|   | Register Balancing                      |

|   | Removing Attributes                     |

## Table of Contents

|   | Using (Q)CLKINT                                          |

|---|----------------------------------------------------------|

|   | Wide Decode Cells in 3200DX and 42MX                     |

| 5 | Actel-Synopsys Design Considerations 67                  |

|   | Compiling Designs with DesignWare Components 67          |

|   | Translating Designs from Other Technologies 68           |

|   | Translating a Design from one Actel family to another 69 |

|   | Translating Timing Constraints into Designer             |

|   | Assigning Pins in Synopsys                               |

|   | Using ACTmap to Optimize I/O Placement                   |

|   | Bus Array Syntax                                         |

|   | Script Mode Place and Route                              |

|   | Control Flow Commands                                    |

|   | Complex Act 3 I/O Mapping                                |

|   | Instantiating ACTgen Macros                              |

|   | Generating an EDIF Netlist                               |

|   | Generating a Structural HDL Netlist                      |

|   | Designing for Radiation Environments                     |

|   | Maintaining Technology Independence 87                   |

| A | Synthesis Library Information                            |

|   | Timing Parameters                                        |

|   | Attributes                                               |

|   | Max Fanout                                               |

|   | ACT 3 Specific Information                               |

|   | 54SX Specific Information                                |

|   | Additional Information                                   |

|   | Synthesis Library Operating Conditions                   |

| В | DesignWare Library Information                           |

|   | DesignWare Library Description                           |

|   | DesignWare Library Adders                                |

|   | DesignWare Library Subtractors 101                       |

## Table of Contents

|   | DesignWare Library Comparators   |

|---|----------------------------------|

|   | DesignWare Library Counters      |

|   | DesignWare Library Incrementer   |

|   | DesignWare Library Decrementer   |

|   | Improving Compilation Time       |

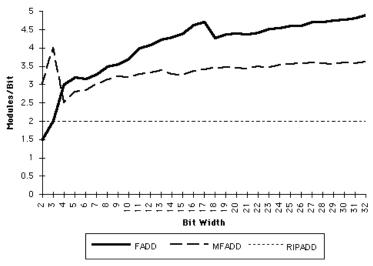

|   | Module Count and Performance     |

| C | Common Problems                  |

|   | Library Errors                   |

|   | Inferring DesignWare             |

|   | Internal Tri-State               |

|   | Multiplexer Inferencing          |

| D | Product Support                  |

|   | Actel U.S. Toll-Free Line        |

|   | Customer Service                 |

|   | Customer Applications Center     |

|   | Guru Automated Technical Support |

|   | Web Site                         |

|   | FTP Site                         |

|   | Electronic Mail                  |

|   | Worldwide Sales Offices          |

|   | Index 129                        |

# **List of Figures**

| Designware Libraries Directory Structure 4                |

|-----------------------------------------------------------|

| Synthesis Libraries Directory Structure                   |

| Actel-Synopsys Design Flow                                |

| Multiplexer Diagram                                       |

| FSM Diagram                                               |

| Compile-Characterize-Recompile Methodology Diagram 57     |

| Schematic Before Register Balancing                       |

| Schematic after Register Balancing                        |

| ACT 3 I/O Macros Directory Structure                      |

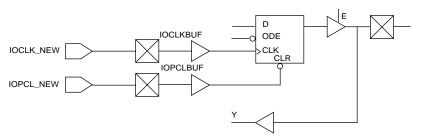

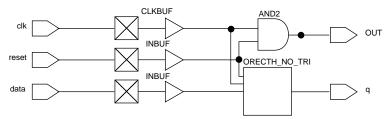

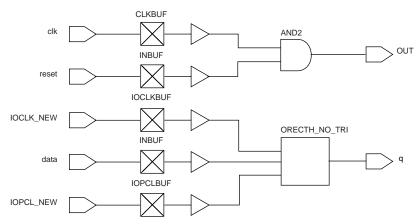

| IOPCLBUF and IOCLKBUF driven sequential cells             |

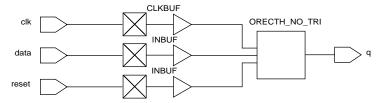

| Compilation Results                                       |

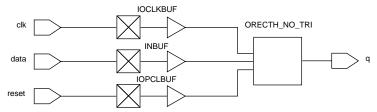

| Script Execution Results                                  |

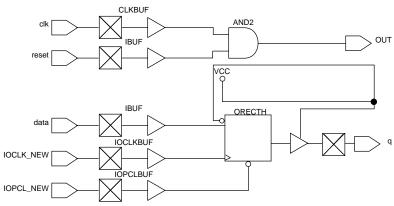

| "CLK" Pad Driving Sequential I/O Cells and Other Logic 77 |

| Corrected Design After Script Implementation              |

| Sequential I/O Cell to ACT 3 I/O Cell Link                |

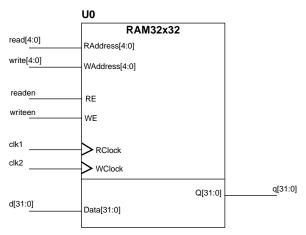

| ACTgen Generated 32 x 32 bit Dual Port RAM 83             |

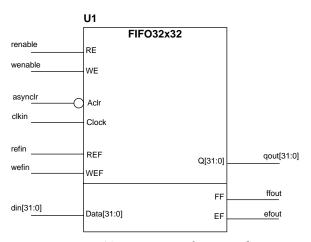

| ACTgen Generated 32 x 32 bit FIFO                         |

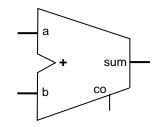

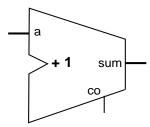

| DesignWare Adder Symbol                                   |

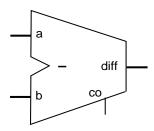

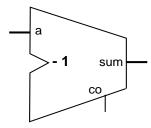

| DesignWare Subtractor Symbol                              |

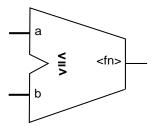

| DesignWare Comparator Symbol                              |

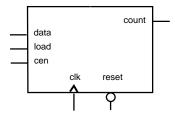

| DesignWare Counter Symbol                                 |

| DesignWare Incrementer Symbol                             |

| DesignWare Decrementer Symbol                             |

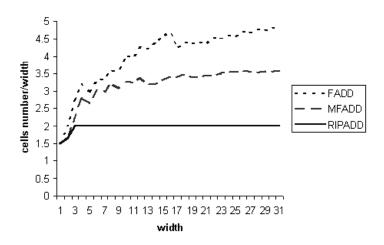

| Adder Module Count                                        |

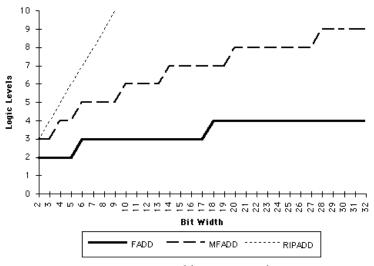

| Adder Logic Level                                         |

| 54SX Adder Module Count                                   |

| 54SX Adder Logic Level                                    |

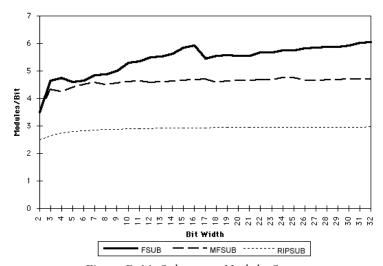

| Subtractor Module Count                                   |

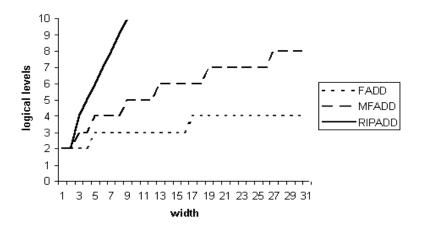

| Subtractor Logic Level                                    |

| 54SX Subtractor Module Count                              |

| 54SX Subtractor Logic Level                               |

| Comparator Module Count                                   |

## List of Figures

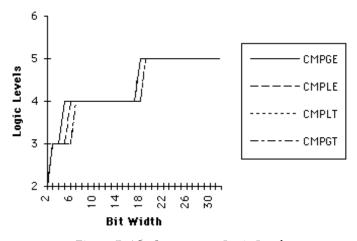

| Comparator Logic Levels .  |  |  |  |  |  |  |  |  |  | . 112 |

|----------------------------|--|--|--|--|--|--|--|--|--|-------|

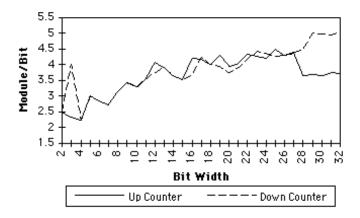

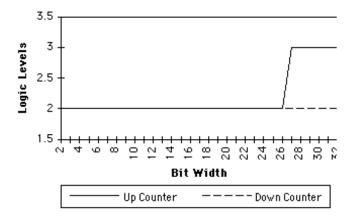

| Counter Module Count       |  |  |  |  |  |  |  |  |  | . 113 |

| Counter Logic Levels       |  |  |  |  |  |  |  |  |  | . 113 |

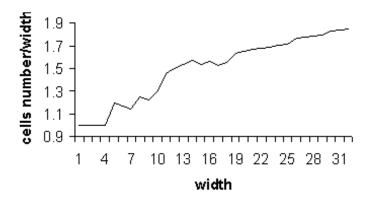

| Incrementer Module Count   |  |  |  |  |  |  |  |  |  | . 114 |

| Incrementer Logic Levels . |  |  |  |  |  |  |  |  |  | . 114 |

| Decrementer Module Count   |  |  |  |  |  |  |  |  |  | . 115 |

| Decrementer Logic Levels . |  |  |  |  |  |  |  |  |  | . 115 |

# **List of Tables**

| FSM Table                                          |

|----------------------------------------------------|

| Sequential Input Cells Available for Synthesis     |

| Sequential Output Cells Available for Synthesis    |

| ACT 1/40MX "dont_touch" and "dont_use" Macros 90   |

| ACT 2/1200XL "dont_touch" and "dont_use" Macros 90 |

| 3200DX/42MX "dont_touch" and "dont_use" Macros 91  |

| ACT 3 "dont_touch" and "dont_use" Macros 91        |

| 54SX "dont_touch" and "dont_use" Macros            |

| Macros that Cannot be Connected to HCLKBUF         |

| Default Operating Conditions                       |

| Synthesis Library Operating Conditions             |

| Supported Modules                                  |

| Adder Pin Description                              |

| Subtractor Pin Description                         |

| Comparator Pin Description                         |

| Counter Pin Description                            |

| Counter Operation Truth Table                      |

| Incrementer Pin Description                        |

| Decrementer Pin Description                        |

## Introduction

The *Synopsys Synthesis Methodology Guide* contains information about using Synopsys UNIX synthesis tools with the Actel Designer Series FPGA development software to create designs for Actel devices. Refer to the *Designing with Actel* manual for additional information about using the Designer series software and the Synopsys documentation for additional information about using Synopsys software.

## **Document Organization**

The *Synopsys Synthesis Methodology Guide* is divided into the following chapters:

**Chapter 1 - Setup** contains information and procedures about setting up Synopsys software for use in creating Actel designs.

**Chapter 2 - Actel-Synopsys Design Flow** illustrates and describes the design flow for creating Actel designs using Synopsys and Designer Series software.

**Chapter 3 - Actel-Synopsys Coding Considerations** describes Actel-Synopsys specific HDL coding techniques.

**Chapter 4 - Synthesis Constraints** contains descriptions, examples, and procedures for using design constraints on Actel designs.

**Chapter 5 - Actel-Synopsys Design Considerations** contains information and procedures to assist you in creating Actel designs with Synopsys and Designer Series software.

**Appendix A - Synthesis Library Information** describes the features of the Actel synthesis libraries available for use in design synthesis.

**Appendix B - DesignWare Library Information** describes the features of the Actel DesignWare libraries available for use in design synthesis.

**Appendix C - Common Problems** describes problems that may occur during synthesis and the solution to the problem.

**Appendix D - Product Support** provides information about contacting Actel for customer and technical support.

## Document Assumptions

The information in this manual is based on the following assumptions:

- 1. You have installed the Designer Series software.

- 2. You have installed the Synopsys software.

- 3. You are familiar with UNIX workstations and operating systems.

- 4. You are familiar with FPGA architecture and FPGA design software.

## **Document Conventions**

The following conventions are used throughout this manual.

Information that is meant to be input by the user is formatted as follows:

```

keyboard input

```

The contents of a file is formatted as follows:

```

file contents

```

HDL code appear as follows, with HDL keywords in bold:

```

entity actel is

port (

a: in bit;

y: out bit);

end actel;

```

Messages that are displayed on the screen appear as follows:

```

Screen Message

```

The <act\_fam> variable represents Actel device family library directories and files. To reference an actual family library directory or file, substitute the actual name of the family when you see this variable. Available families are act1, act2 (for ACT 2 and 1200XL devices), act3, 3200dx, 40mx, 42mx, and 54sx.

## HDL Keywords and Naming Conventions

There are naming conventions you must follow when writing Verilog or VHDL code. Additionally, Verilog and VHDL have reserved words that cannot be used for signal or entity names. This section lists the naming conventions and reserved keywords for each.

#### **VHDL**

The following naming conventions apply to VHDL designs:

- VHDL is not case sensitive.

- Two dashes "--" are used to begin comment lines.

- Names can use alphanumeric characters and the underscore "\_" character.

- Names must begin with an alphabetic letter.

- You may not use two underscores in a row, or use an underscore as the last character in the name.

- Spaces are not allowed within names.

- Object names must be unique. For example, you cannot have a signal named A and a bus named A(7 downto 0).

The following is a list of the VHDL reserved keywords that cannot be used in your design:

| abs                | downto   | library | postponed | subtype    |

|--------------------|----------|---------|-----------|------------|

| access             | else     | linkage | procedure | then       |

| after              | elsif    | literal | process   | to         |

| alias              | end      | loop    | pure      | transport  |

| all                | entity   | map     | range     | type       |

| and                | exit     | mod     | record    | unaffected |

| architecture       | file     | nand    | register  | units      |

| array              | for      | new     | reject    | until      |

| assert             | function | next    | rem       | use        |

| attribute          | generate | nor     | report    | variable   |

| begin              | generic  | not     | return    | wait       |

| block              | group    | null    | rol       | when       |

| body               | guarded  | of      | ror       | while      |

| buffer             | if       | on      | select    | with       |

| bus                | impure   | open    | severity  | xnor       |

| case               | in       | or      | shared    | xor        |

| component          | inertial | others  | signal    |            |

| configura-<br>tion | inout    | out     | sla       |            |

| constant           | is       | package | sra       |            |

| disconnect         | label    | port    | srl       |            |

## Verilog

The following naming conventions apply to Verilog HDL designs:

- Verilog is case sensitive.

- Two slashes "//" are used to begin single line comments. A slash and asterisk "/\*" are used to begin a multiple line comment and an asterisk and slash "\*/" are used to end a multiple line comment.

- Names can use alphanumeric characters, the underscore "\_" character, and the dollar "\$" character.

- Names must begin with an alphabetic letter or the underscore.

- Spaces are not allowed within names.

The following is a list of the Verilog reserved keywords that cannot be used in your design:

| always       | endfunction  | macromodule | realtime  | tran     |

|--------------|--------------|-------------|-----------|----------|

| and          | endmodule    | medium      | reg       | tranif0  |

| assign       | endprimitive | module      | release   | tranif1  |

| attribute    | endspecify   | nand        | repeat    | tri      |

| begin        | endtable     | negedge     | rnmos     | tri0     |

| buf          | endtask      | nmos        | rpmos     | tri1     |

| bufif0       | event        | nor         | rtran     | triand   |

| bufif1       | for          | not         | rtranif0  | trior    |

| case         | force        | notif0      | rtranif1  | trireg   |

| casex        | forever      | notif1      | scalared  | unsigned |

| casez        | fork         | or          | signed    | vectored |

| cmos         | function     | output      | small     | wait     |

| const        | highz0       | parameter   | specify   | wand     |

| deassign     | highz1       | pmos        | specparam | weak0    |

| default      | if           | posedge     | strength  | weak1    |

| defparam     | ifnone       | primitive   | strong0   | while    |

| disable      | initial      | pull0       | strong1   | wire     |

| edge         | inout        | pull1       | supply0   | wor      |

| else         | input        | pulldown    | supply1   | xnor     |

| end          | integer      | pullup      | table     | xor      |

| endattribute | join         | remos       | task      |          |

| endcase      | large        | real        | time      |          |

## **Actel Manuals**

The Designer Series software includes printed and on-line manuals. The on-line manuals are in PDF format on the CD-ROM in the "/ manuals" directory. These manuals are also installed onto your system when you install the Designer software. To view the on-line manuals, you must install Adobe® Acrobat Reader® from the CD-Rom.

The Designer Series includes the following manuals, which provide additional information on designing Actel FPGAs:

Designing with Actel. This manual describes the design flow and user interface for the Actel Designer Series software, including information about using the ACTgen Macro Builder and ACTmap VHDL Synthesis software.

Actel HDL Coding Style Guide. This guide provides preferred coding styles for the Actel architecture and information about optimizing your HDL code for Actel devices.

ACTmap VHDL Synthesis Methodology Guide. This guide contains information, optimization techniques, and procedures to assist designers in the design of Actel devices using ACTmap VHDL.

Silicon Expert User's Guide. This guide contains information and procedures to assist designers in the use of Actel's Silicon Expert tool.

DeskTOP Interface Guide. This guide contains information about using the integrated VeriBest® and Synplicity® CAE software tools with the Actel Designer Series FPGA development tools to create designs for Actel Devices.

Cadence® Interface Guide. This guide contains information and procedures to assist designers in the design of Actel devices using Cadence CAE software and the Designer Series software.

*Mentor Graphics* ® *Interface Guide*. This guide contains information and procedures to assist designers in the design of Actel devices using Mentor Graphics CAE software and the Designer Series software.

*MOTIVE™ Static Timing Analysis Interface Guide.* This guide contains information and procedures to assist designers in the use of the MOTIVE software to perform static timing analysis on Actel designs.

Synopsys® Synthesis Methodology Guide. This guide contains preferred HDL coding styles and information and procedures to assist designers in the design of Actel devices using Synopsys CAE software and the Designer Series software.

Viewlogic Powerview® Interface Guide. This guide contains information and procedures to assist designers in the design of Actel

devices using Powerview CAE software and the Designer Series software.

Viewlogic Workview Office Interface Guide. This guide contains information and procedures to assist designers in the design of Actel devices using Workview Office CAE software and the Designer Series software

VHDL Vital Simulation Guide. This guide contains information and procedures to assist designers in simulating Actel designs using a Vital compliant VHDL simulator.

*Verilog Simulation Guide.* This guide contains information and procedures to assist designers in simulating Actel designs using a Verilog simulator.

Activator and APS Programming System Installation and User's Guide. This guide contains information about how to program and debug Actel devices, including information about using the Silicon Explorer diagnostic tool for system verification.

*Silicon Sculptor User's Guide*. This guide contains information about how to program Actel devices using the Silicon Sculptor software and device programmer.

Silicon Explorer Quick Start. This guide contains information about connecting the Silicon Explorer diagnostic tool and using it to perform system verification.

Designer Series Development System Conversion Guide UNIX® Environments. This guide describes how to convert designs created in Designer Series versions 3.0 and 3.1 for UNIX to be compatible with later versions of Designer Series.

Designer Series Development System Conversion Guide Windows Environments. This guide describes how to convert designs created in Designer Series versions 3.0 and 3.1 for Windows to be compatible with later versions of Designer Series.

Actel FPGA Data Book. This guide contains detailed specifications on Actel device families. Information such as propagation delays, device package pinout, derating factors, and power calculations are found in this guide.

#### Introduction

*Macro Library Guide.* This guide provides descriptions of Actel library elements for Actel device families. Symbols, truth tables, and module count are included for all macros.

*A Guide to ACTgen Macros*. This Guide provides descriptions of macros that can be generated using the Actel ACTgen Macro Builder software.

## On-Line Help

The Designer Series software comes with on-line help. On-line help specific to each software tool is available in Designer, ACTgen, ACTmap, Silicon Expert, Silicon Explorer, Silicon Sculptor, and APSW.

## Setup

This chapter contains information about setting up UNIX Synopsys tools to create Actel designs. This includes setting environment variables and information about setting up a system to access the Actel macro and synthesis libraries. Refer to the Synopsys documentation for additional information about setting up Synopsys tools.

## Software Requirements

The information in this guide applies to the Actel Designer Series software release R1-1999 or later and Synopsys DC Compiler and FPGA Compiler. For specific information about which versions are supported with this release, go to the Guru automated technical support system on the Actel Web site (http://www.actel.com/guru) and type the following in the Keyword box:

third party

## System Setup

After installing Synopsys, make sure the proper environment variables are set in your UNIX shell script. The following are C shell variables. If you are using another shell, adjust the syntax accordingly.

```

setenv SYNOPSYS <synopsys_install_directory>

source $SYNOPSYS/admin/install/sim/bin/environ.csh

setenv ALSDIR <actel_install_directory>

setenv ACT_SYNOPDIR $ALSDIR/lib/synop

set path=($ALSDIR/bin $path)

set path=($SYNOPSYS/<operating_system>/syn/bin $path)

```

Replace the <operating\_system> variable in the "set path" line with "sparc" if you use SunOS, "sparcOS5" if you use Solaris, or "hp700" if you use HP-UX.

If you use SunOS or Solaris, the following variable must also be set:

```

setenv LD LIBRARY PATH $ALSDIR/lib

```

If you use HP-UX, the following variable must also be set:

```

setenv SHLIB_PATH $ALSDIR/lib

```

#### Chapter 1: Setup

Refer to the *Designing with Actel* manual and the Synopsys documentation for additional information about setting environment variables

## User Setup

If you use Actel macros or synthesis libraries when creating designs in Synopsys, you must setup your system to access them. This section describes how to access Actel DesignWare and synthesis libraries.

### Reanalyzing DesignWare Libraries

Before creating a design in Synopsys, you must reanalyze the encrypted DesignWare and simulation libraries to achieve compatibility with your version of Synopsys. During reanalysis, the existing DesignWare libraries are overwritten. If you wish to retain the old libraries for use with earlier Synopsys versions, copy the "\$ALSDIR/lib/synop" tree to a new location before you reanalyze the libraries.

### To reanalyze all installed Actel DesignWare libraries:

- 1. Acquire write permission.

- **2. Go to the "scripts" directory.** Type the following command at the prompt:

cd \$ACT\_SYNOPDIR/scripts

**3. Reanalyze the DesignWare libraries.** Type:

update\_all\_dw

#### To reanalyze a specific Actel family DesignWare library:

- 1. Acquire write permission.

- **2. Go to the "scripts/<act\_fam>" directory.** Type the following command at the prompt:

cd \$ACT\_SYNOPDIR/scripts/<act\_fam>

**3. Reanalyze the DesignWare library.** Type the following command at the prompt:

update\_dwact

### Accessing DesignWare Libraries

To access the DesignWare libraries, set the search path in the ".synopsys\_dc.setup" file to include the "actsetup.scr" file of the Actel device family you want to access and include the "DWACT" library and component package in your VHDL description each time you infer or instantiate a synthetic component from the DesignWare libraries. Add the following lines to the ".synopsys\_dc.setup" file to access the "actsetup.scr" file:

```

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

```

Add the following lines to your VHDL description to include the "DWACT" library and component package each time you infer or instantiate a synthetic component from the DesignWare libraries:

```

library dwact;

use dwact.dwact_components.all;

```

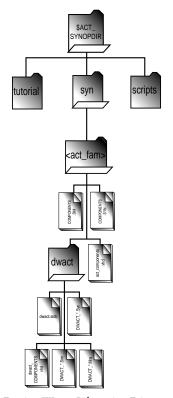

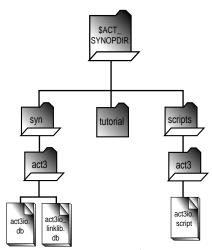

Figure 1-1 shows the directory structure for the DW libraries<sup>1</sup>.

Figure 1-1. DesignWare Libraries Directory Structure

The "dwact.sldb" file is a compiled description of the Actel synthetic libraries and "DWACT\_COMPONENTS.syn" is a "compile\_package" file. An ASCII version of the package file can also be found in the same directory. Refer to "DesignWare Module Coding" on page 31 for information about using the DesignWare library modules.

<sup>1.</sup> DesignWare libraries are not available for ACT 1 and 40MX devices.

### Accessing Synthesis Libraries

To access the synthesis libraries, set the search path in the ".synopsys\_dc.setup" file to include the "actsetup.scr" file of the Actel device family you want to access. Add the following lines to the ".synopsys\_dc.setup" file to access the "actsetup.scr" file:

```

actlib = get_unix_variable ("ACT_SYNOPDIR")

include actlib + /scripts/<act_fam>/actsetup.scr

```

Note: To target the 1200XL family, synthesize using the ACT 2 library and use the "XL" operating conditions for timing. Refer to "Synthesis Library Operating Conditions" on page 96 for additional information.

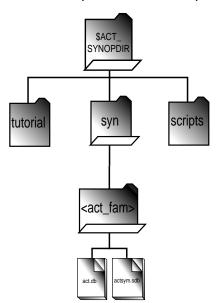

Figure 1-2 shows the directory structure for the Synthesis libraries.

Figure 1-2. Synthesis Libraries Directory Structure

### To verify the library version:

Type the following command at the prompt:

\$ACT\_SYNOPDIR/scripts/version

# Actel-Synopsys Design Flow

This chapter illustrates and describes the design flow for creating Actel designs using Synopsys tools and the Designer Series software.

## Design Flow Illustrated

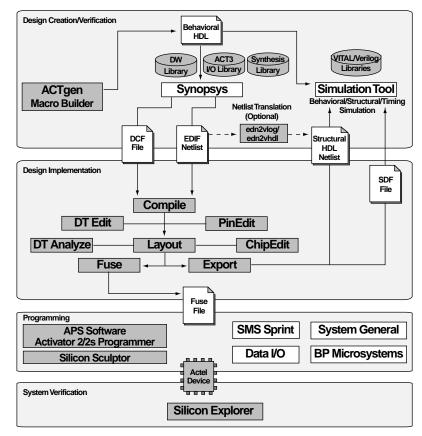

Figure 2-1 illustrates the design flow for creating an Actel device using Synopsys Designer Series software<sup>1</sup>.

Figure 2-1. Actel-Synopsys Design Flow

<sup>1.</sup> Actel-specific utilities/tools are denoted by the grey boxes in Figure 2-1.

## Design Flow Overview

The Actel-Synopsys design flow has four main steps; design creation/verification, design implementation, programming, and system verification. These steps are described in the following sections.

### Design Creation/ Verification

During design creation/verification, a design is captured in an RTL-level (behavioral) HDL source file. After capturing the design, a behavioral simulation of the HDL file can be performed to verify that the HDL code is correct. The code is then synthesized into an Actel gate-level (structural) netlist. After synthesis, a structural simulation of the design can be performed. Finally, an EDIF netlist is generated for import into Designer from which an HDL structural netlist is generated for structural and timing simulation.

#### HDL Design Source Entry

Enter your HDL design source using a text editor or a context-sensitive HDL editor. Your HDL design source can contain RTL-level constructs, as well as instantiations of structural elements, such as ACTgen macros.

#### **Behavioral Simulation**

You may perform a behavioral simulation of your design before synthesis. Behavioral simulation verifies the functionality of your HDL code. Typically, unit delays are used and a standard HDL test bench can be used to drive simulation. Refer to the *VHDL VITAL Simulation Guide* or *Verilog Simulation Guide* for information about performing behavioral simulation.

#### Synthesis

After you have created your HDL design source, you must synthesize it before placing and routing it in Designer. Synthesis transforms the behavioral HDL file into a gate-level netlist and optimizes the design for a target technology. Refer to the Synopsys documentation for information about performing design synthesis.

#### **EDIF Netlist Generation**

After you have created, synthesized, and verified your design, you must generate an EDIF netlist for place and route in Designer. This EDIF netlist is also used to generate a structural HDL netlist. Refer to "Generating an EDIF Netlist" on page 85 for information about generating an EDIF netlist.

#### Structural HDL Netlist Generation

Generate a structural HDL netlist from your EDIF netlist for use in structural and timing simulation by either exporting it from Designer or by using the Actel "edn2vlog" or "edn2vhdl" program. Refer to "Generating a Structural HDL Netlist" on page 86 for information about generating a structural netlist.

#### Structural Simulation

You may perform a structural simulation of your design before placing and routing it. Structural simulation verifies the functionality of your post-synthesis structural HDL netlist. Default unit delays included in the Actel libraries are used for every gate. Refer to the VHDL VITAL Simulation Guide or Verilog Simulation Guide for information about performing structural simulation.

## Design Implementation

During design implementation, a design is placed and routed using Designer. Additionally, static timing analysis can be performed on a design in Designer with the DT Analyze tool. After place and route, post-layout (timing) simulation may be performed.

#### Place and Route

Use Designer to place and route your design. Make sure to specify GENERIC as the EDIF Flavor and Verilog or VHDL as the Naming Style when importing the EDIF netlist into Designer. Refer to the *Designing with Actel* manual for information about using Designer.

### Static Timing Analysis

Use the DT Analyze tool in Designer to perform static timing analysis on your design. Refer to the *Designing with Actel* manual for information on using DT Analyze.

#### Chapter 2: Actel-Synopsys Design Flow

#### **Timing Simulation**

You may perform a timing simulation of your design after placing and routing it. Timing simulation requires timing information exported from Designer, which overrides default unit delays in the Actel libraries. Refer to the *Designing with Actel* manual for information about exporting timing information from Designer. Refer to the *VHDL VITAL Simulation Guide* or *Verilog Simulation Guide* for information about performing structural simulation.

## **Programming**

Program a device with programming software and hardware from Actel or a supported 3rd party programming system. Refer to the *Designing with Actel* manual and the *Activator and APS Programming System Installation and User's Guide* or *Silicon Sculptor User's Guide* for information about programming an Actel device.

## System Verification

You can perform system verification on a programmed device using the Actel Silicon Explorer diagnostic tool. Refer to the *Activator and APS Programming System Installation and User's Guide* or *Silicon Explorer Quick Start* for information about using the Silicon Explorer.

# **Actel-Synopsys Coding Considerations**

This chapter describes preferred coding styles for the Actel architecture when using Synopsys synthesis and simulation tools. Examples of HDL code are also given. Included in this chapter is information about multiplexer encoding, finite state machine design, and DesignWare module coding. Refer to the *Actel HDL Coding Style Guide* for additional information about HDL coding for Actel devices.

## Multiplexer Encoding

The multiplexer based Actel architecture provides area and speed efficient implementations if multiplexers are inferred using case statements. Multiplexer inference using case statements is more efficient than inference of priority encoders using the if-then-else statements. This coding style provides the synthesis tool a good starting point because case statements imply that all conditions are mutually exclusive.

You can synthesize a multiplexer using a case statement in your HDL code. However, current synthesis technology is based on "reconstruction of logic" where the logic is broken into boolean terms, optimized, and mapped to gates. Often, it is difficult to reconstruct a multiplexer when it is broken down.

Use the Synopsys directive, "full\_case parallel\_case" to force multiplexer inference. You should also embed an attribute, "infer\_mux," in the HDL code to instruct (V)HDL Compiler that certain case statements should be inferred as generic multiplexer cells (MUX\_OPs). (V)HDL Compiler maps these MUX\_OPs in the design to multiplexers in the technology.

## Multiplexer Inferencing Variables

Three "hdlin" attributes determine how and when MUX\_OPs are inferred by (V)HDL compiler. These variables can be set in the ".synopsys\_dc.setup" file or in a compile script during compilation. In the following examples, the attributes have been set in a compile script. After setting the "hdlin" and compile variables, constraints are set on the design. Typical constraints are delay constraints (such as "max\_delay") and fanout constraints (such as "max\_fanout"). Failure to set the "max\_fanout" constraint can result in a design that has excessive fanout on nets (>24) resulting in errors during compilation in Designer. The three "hdlin" variables are described below with recommended settings when targeting the Actel architecture.

#### hdlin\_infer\_mux

The "hdlin\_infer\_mux" variable controls MUX\_OP inferencing for the current design and all subsequent designs unless the variable is changed. This variable can be set to three values: "default" (MUX\_OPs are inferred for case statements that have the "infer\_mux" attribute or directive attached), "none" (no MUX\_OPs are inferred) and "all" (MUX\_OPs are inferred for every case statement in the design). For best results when targeting the Actel architecture, set this variable to "all."

#### hdlin\_dont\_infer\_mux\_for\_resoruce\_sharing

The "hdlin\_don\_infer\_mux\_for\_resoruce\_sharing" variable determines whether MUX\_OPs are inferred when two or more synthetic operators drive the inputs of the MUX\_OP. The default setting of "true" prevents the inference of MUX\_OPs when synthetic operators drive the inputs of the MUX\_OP. Setting the variable to "false" allows a MUX\_OP to be inferred. For best results when targeting the Actel architecture, set this variable to "false."

### hdlin mux size limit

The "hdlin\_mux\_size\_limit" variable sets the maximum size of the MUX\_OP to be inferred. The default value is 32. This variable should be set to a larger value when multiplexers with more than 32 inputs are inferred. However, this results in longer compilation time.

# Compilation Variables

In addition to the "hdlin" variables, two compile variables are used to control multiplexer logic. These are described below with recommended settings for best results when targeting the Actel architecture:

## compile\_create\_mux\_op\_hierarchy

When the "compile\_create\_mux\_op\_hierarchy" variable is set to "true" (default), (V)HDL Compiler creates MUX\_OPs with their own level of hierarchy. When "false," (V)HDL Compiler removes this level of hierarchy. For best results when targeting the Actel architecture, set this variable to "true."

#### compile\_mux\_no\_boundary\_optimization

When the "compile\_mux\_no\_boundary\_optimization" variable is set to "false" (default), (V)HDL Compiler performs boundary optimization on all MUX\_OP implementations. When "true," no boundary optimization is performed. Boundary optimization can result in sub-optimal implementations when inferred multiplexers have inputs connected to constant values. For best results when targeting the Actel architecture, set this variable to "true."

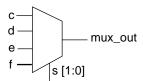

## Multiplexer Inferencing

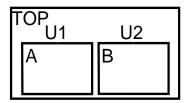

MUX\_OPs are only inferred for case statements contained in processes (VHDL) or always blocks (Verilog). MUX\_OPs are not inferred for ifthen-else statements or case statements contained within if-then-else statements. Consequently, case statements should be always be used when describing multiplexers in Verilog or VHDL. The following examples describe the behavioral syntax for inferring a 4 to 1 multiplexer using a case statement. Figure 3-1 illustrates the multiplexer.

Figure 3-1. Multiplexer Diagram

### Verilog

```

module mux4_1 (c, d, e, f, s, mux_out);

input c, d, e, f;

input [1:0] s;

output mux_out;

reg mux_out;

always @(c or d or e or f or s)

begin

case (s)

2'b00 : mux_out = c;

2'b01 : mux_out = d;

2'b10 : mux_out = e;

default : mux_out = f;

endcase

end

endmodule

```

#### **VHDL**

```

library ieee;

library synopsys;

use ieee.std_logic_1164.all;

use synopsys.attributes.all;

entity mux4_1 is

port (c, d, e, f : in std_logic;

: in std_logic_vector(1 downto 0);

: out std_logic );

mux_out

end mux4_1;

architecture behave of mux4_1 is

mux1: process (s, c, d, e, f)

begin

case s is

when "00" => mux_out <= c;</pre>

when "01" => mux_out <= d;

when "10" => mux_out <= e;

when others => mux_out <= f;</pre>

end case;

end process mux1;

end behave;

```

## Synopsys Script

To force (V)HDL Compiler to infer multiplexers, the compile variables and "hdlin" variables must be set properly. This can be done in the ".synopys\_dc.setup" file or in a compile script. The following is an example compile script.

```

/* Script file for mux4_1 design */

/* read Actel Synopsys setup script and set Mux inferencing

Switches*/

/* this could also be done in the .synopsys_dc.setup file */

actlib = get_unix_variable ("ACT_SYNOPDIR")

include actlib + /scripts/<act_fam>/actsetup.scr

/* Set Mux inferencing switches */

hdlin_infer_mux = all;

compile_mux_no_boundary_optimization = true

hdlin_dont_infer_mux_for_resource_sharing = false

/* read design file - use this for Verilog design*/

read -f verilog mux4_1.v

```

```

/* read design file - use this for VHDL design */

read -f VHDL mux4_1.vhd

current_design = mux4_1

/* set max_fanout constraint*/

max_fanout 12

/* set delay constraint on mux4_1 from S[1:0] to output */

set_max_delay 20 -to { "mux_out" } -from { "s<1>" }

set_max_delay 20 -to { "mux_out" } -from { "s<0>" }

set_operating_conditions COMWCSTD

compile -map_effort medium

set_port_is_pad all_inputs()

set_port_is_pad all_outputs()

insert_pads

/* write out EDIF netlist */

write -f edif -h -o mux4_1.edn

```

## Wide Multiplexers

When the number of multiplexer inputs is larger than four, effective use of the Synopsys multiplexer inference attributes, variables, and delay constraints are required to produce an optimal implementation in the Actel architecture. When the number of multiplexer inputs is not a power of four (such as 11) the implementation created by (V)HDL Compiler may use multiplexers with all the inputs tied to logic 1 or logic 0. These multiplexers are removed by the Actel Designer software during design compilation to produce a more area efficient implementation. The following examples describe the behavioral syntax for inferring an 11 to 1 multiplexer.

#### Verilog

```

module mux11 (s, a, b, c, d, e, f, g, h, i, j, k, mux_out);

input [3:0] s;

input a, b, c, d, e, f, g, h, i, j, k;

output mux_out;

reg mux_out;

// create an 11:1 mux using a case statement

always @ ({s[3:0]} or a or b or c or d or e or f or g or h or

i or j or k)

begin: mux_blk

case ({s[3:0]}) // synopsys full_case parallel_case

```

```

4'b0000 :

mux_out = a;

4'b0001:

mux_out = b;

4'b0010 :

mux_out = c;

4'b0011 :

mux_out = d;

4'b0100 :

mux_out = e;

4'b0101:

mux_out = f;

4'b0110 :

mux_out = g;

4'b0111 :

mux_out = h;

4'b1000 :

mux_out = i;

4'b1001 :

mux_out = j;

4'b1010 :

mux_out = k;

default:

mux_out = 1'b1;

endcase

end

endmodule

```

#### **VHDL**

```

library ieee;

library synopsys;

use ieee.std_logic_1164.all;

use synopsys.attributes.all;

entity mux11 is

port (a, b, c, d, e, f, g, h, i, j, k: in std_logic;

s : in std_logic_vector(3 downto 0);

mux_out : out std_logic );

end mux11;

architecture behave of mux11 is

mux1: process (s, a, b, c, d, e, f, g, h, i, j, k)

begin

case s is

when "0000" => mux_out <= a;</pre>

when "0001" => mux_out <= b;

when "0010" => mux_out <= c;</pre>

when "0011" => mux_out <= d;</pre>

when "0100" => mux_out <= e;</pre>

when "0101" => mux_out <= f;</pre>

when "0110" => mux out <= q;

when "0111" => mux_out <= h;</pre>

when "1000" => mux_out <= i;</pre>

when "1001" => mux_out <= j;</pre>

when "1010" => mux_out <= k;</pre>

when others => mux_out <= '1';

end case;

end process mux1;

end behave;

```

#### Synopsys Script

The following example compile script sets the compile and "hdlin" variables. A "max\_delay" constraint has been set from the select lines S[3:0] to "mux\_out." A tight constraint was placed on S[3:2] while a looser constraint was placed on S[1:0] to ensure that the low order bits are driven by S[1:0]. This causes (V)HDL compiler to build a 16 to 1 mux with five inputs connected to logic 1.

```

/* Script file for 11:1 multiplexer design */

actlib = get_unix_variable ("ACT_SYNOPDIR")

include actlib + /scripts/<act_fam>/actsetup.scr

/* Set Mux inferencing switches

* /

hdlin_infer_mux = all

compile mux no boundary optimization = true

hdlin_dont_infer_mux_for_resource_sharing = false

/* read design files - use the following for VHDL*/

read -f verilog mux11.vhd

/* read design files - use the following for Verilog */

read -f verilog mux11.v

current_design = mux11

max fanout = 12

/* force short delay on SEL[3:2] so designer will remove

unneeded mux */

set_max_delay 5 -to { "mux_out" } -from { "S<3>" }

set_max_delay 5 -to { "mux_out" } -from { "S<2>" }

/* set longer delay from SEL[1:0] */

set_max_delay 20 -to { "mux_out" } -from { "S<1>" }

set_max_delay 20 -to { "mux_out" } -from { "S<0>" }

set_operating_conditions COMWCSTD

compile -map_effort medium

report_area > mux11.rpt

set_port_is_pad all_inputs()

set_port_is_pad all_outputs()

insert_pads

write -f edif -h -o mux11.edn

```

## Registered Multiplexers

In a datapath application, multiplexers drive registers. These structures can quickly be inferred using the MUX\_OP attributes. As in the previous examples, a combination of compile variables and constraints is required to get the optimum implementation.

#### Verilog

```

module reg_mux11 (rst, clk, s, a, b, c, d, e, f, g, h, i, j, k,

mux_out);

input [3:0] s;

input a, b, c, d, e, f, g, h, i, j, k;

input clk, rst;

output mux_out;

reg mux_out;

out

// synopsys infer_mux "mux_blk"

// create a registered 11:1 mux using a case statement

always @ (posedge clk or negedge rst)

begin: mux_blk

if (~rst)

mux_out = 1'b0;

case ({s[3:0]}) // synopsys full_case parallel_case

4'b0000 :

mux_out = a;

4'b0001 :

mux_out = b;

4'b0010 :

mux_out = c;

4'b0011 :

mux_out = d;

4'b0100 :

mux_out = e;

4'b0101 :

mux_out = f;

4'b0110 :

mux_out = gi

4'b0111 :

mux_out = h;

4'b1000 :

mux_out = i;

4'b1001 :

mux_out = j;

4'b1010 : mux_out = k;

default:

mux_out = 1'b1;

endcase

end

endmodule

```

#### **VHDL**

```

library ieee;

library synopsys; -- for synopsys mux inferencing

use ieee.std_logic_1164.all;

use synopsys.attributes.all; -- for synopsys mux inferencing

entity reg_mux11 is

port

(s: in std_logic_vector (3 downto 0); -- mux select

a, b, c, d, e, f, g, h, i, j, k : in std_logic;

clk, rst : in std_logic;

mux_out : out std_logic); -- mux output

end reg_mux11;

architecture synth of reg_mux11 is

begin

proc1: process (rst, clk)

begin

if (rst = '0') then

mux_out <= '0';

elsif (clk 'event and clk = '1') then

case s is

when "0000"

=> mux_out <= a;

when "0001"

=> mux_out <= b;

when "0010"

=> mux_out <= c;

when "0011"

=> mux_out <= d;

when "0100"

=> mux_out <= e;

when "0101"

=> mux_out <= f;

when "0110"

=> mux_out <= g;

when "0111"

=> mux_out <= h;

when "1000"

=> mux_out <= i;

when "1001"

=> mux_out <= j;

when "1010"

=> mux out <= k;

when others

=> mux_out <= '1';

end case;

end if;

end process proc1;

end synth;

```

#### Synopsys Script

The following example compile script sets the compile and "hdlin" variables. A "max\_delay" constraint has been set from the select lines S[3:0] to the MUX\_OUT register. A tight constraint was placed on S[3:2] while a looser constraint was placed on S[1:0] to ensure that the low order bits are driven by S[1:0]. This causes (V)HDL compiler to build a 16 to 1 mux with five inputs connected to logic 1. One of the multiplexers is removed during compile phase in Designer.

```

/* Script file for reg_mux11.v design*/

actlib = get unix variable ("ACT SYNOPDIR")

include actlib + /scripts/<act_fam>/actsetup.scr

/* Set Mux inferencing switches*/

hdlin_infer_mux = all

compile_mux_no_boundary_optimization = true

hdlin_dont_infer_mux_for_resource_sharing = false

/* read design files - use the following for VHDL*/

read -f vhdl reg_mux11.vhd

/* read design files - use the following for Verilog*/

read -f verilog reg_mux11.v

current_design = reg_mux11

max fanout 12

/* force short delay on S[3:2] so designer will remove

unneeded mux*/

set_max_delay 5 -to find(cell, mux_out_reg) -from { "S<3>" }

set_max_delay 5 -to find(cell, mux_out_reg) -from { "S<2>" }

/* set longer delay from S[1:0] */

set_max_delay 20 -to find(cell, mux_out_reg) -from { "S<1>" }

set_max_delay 20 -to find(cell, mux_out_reg) -from { "S<0>" }

/* set clock constraint*/

create_clock -name "clk" -period 25 -waveform { "0" "12.5" }

{ "clk" }

set operating conditions COMWCSTD

compile -map_effort medium

set_port_is_pad all_inputs()

set_port_is_pad all_outputs()

insert_pads

write -f edif -h -o reg_mux11.edn

```

# Under Utilized Case

If a case statement is not fully specified, i.e., when the number of data inputs specified for the MUX\_OPs is not the same as the number of data inputs required based on the number of selected lines, (V)HDL Compiler may not create an efficient implementation. In the example below, there should be 32 independent cases because the select line is 5-bits wide. However, when the most significant bit of the select s4 is logic 1, the output is always logic 0 and only 16 cases are specified. Proper use of multiplexer inferencing variables and constraints result in an efficient implementation for the Actel architecture. For Example:

### Verilog

```

module org_mux_32_1 (data, s, y);

input[4:0] s;

input[31:0] data;

output y;

reg y;

//synopsys infer_mux "mux"

always @(data or s)

begin: mux

case(s)

5'h00 : y = data[0];

5'h01 : y = data[1];

5'h02 : y = data[2];

5'h03 : y = data[3];

5'h04 : y = data[4];

5'h05 : y = data[5];

5'h06 : y = data[6];

5'h07 : y = data[7];

5'h08 : y = data[8];

5'h09 : y = data[9];

5'h0a : y = data[10];

5'h0b : y = data[11];

5'h0c : y = data[12];

5'h0d : y = data[13];

5'h0e : y = data[14];

5'h0f : y = data[15];

default: y = 1'd0;

endcase

end

endmodule

```

#### **VHDL**

```

library ieee;

library synopsys;

use ieee.std_logic_1164.all;

use synopsys.attributes.all;

entity org_mux_32_1 is

port (data: in std_logic_vector(31 downto 0);

s : in std_logic_vector(4 downto 0);

y : out std_logic );

end org_mux_32_1;

architecture behave of org_mux_32_1 is

-- include the next line to use mux_op inferencing

attribute infer_mux of mux1: label is "true";

begin

mux1: process (s, data)

begin

case s is

when "00000" => y <= data(0);

when "00001" => y <= data(1);</pre>

when "00010" => y <= data(2);</pre>

when "00011" => y <= data(3);</pre>

when "00100" => y <= data(4);</pre>

when "00101" => y <= data(5);</pre>

when "00110" => y <= data(6);</pre>

when "00111" => y <= data(7);</pre>

when "01000" => y <= data(8);</pre>

when "01001" => y <= data(9);

when "01010" => y <= data(10);

when "01011" => y <= data(11);</pre>

when "01100" => v <= data(12);</pre>

when "01101" => y <= data(13);</pre>

when "01110" => y <= data(14);</pre>

when "01111" => y <= data(15);</pre>

when others => y <= '0';

end case;

end process;

end behave;

```

#### Synopsys Script

To force (V)HDL Compiler to infer an area efficient multiplexer, the compile constraints must be set properly. The following example compile script sets the constraints.

```

/* Script file for org_mux_32_1.vhd design */

sh date

actlib = get_unix_variable ("ACT_SYNOPDIR")

include actlib + /scripts/<act_fam>/actsetup.scr

/* Set Mux inferencing switches */

compile_mux_no_boundary_optimization = true

hdlin_dont_infer_mux_for_resource_sharing = false /* allows

best implementation of mux */

/* read design files - use the following for VHDL */

read -f vhdl org_mux_32_1.vhd

/* read design files - use the following for Verilog */

read -f vhdl org_mux_32_1.v

current_design = org_mux_32_1

/* force shortest delay on s[4]*/

set_max_delay 5 -to { "y "} -from { "s<4>" }

/* force short delay on s[3:2] so designer will remove

unneeded mux

* /

set_max_delay 9 -to { "y" } -from { "s<3>" }

set_max_delay 9 -to { "y" } -from { "s<2>" }

/* set longer delay from s[1:0] */

set_max_delay 20 -to { "y" } -from { "s<1>" }

set_max_delay 20 -to { "y" } -from { "s<0>" }

set_operating_conditions COMWCSTD

compile -map_effort medium

set_port_is_pad all_inputs()

set_port_is_pad all_outputs()

insert_pads

write -f edif -h -o org_mux_32_1.edn

```

# Finite State Machine Design

Because of sequential element abundance in the Actel architecture, the one-hot encoding for state machines can generate an area and speed optimized design.

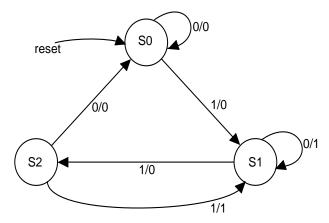

You must code the state machine as a regular compact encoding, and the Finite State Machine (FSM) optimization must be used to extract the states and generate the bit per state methodology. If you code the bit per state technique in the HDL code, Synopsys does not generate an area and performance optimized state machine. For example, consider a simple Mealy FSM illustrated in Figure 3-2 and Table 3-1.

Figure 3-2. FSM Diagram

| Table 3-1. | FSM | Table |

|------------|-----|-------|

|            |     |       |

| Present State | Next State |     | Output (z) |     |

|---------------|------------|-----|------------|-----|

|               | a=0        | a=1 | a=0        | a=1 |

| S0            | S0         | S1  | 0          | 0   |

| S1            | S1         | S2  | 1          | 0   |

| S2            | S0         | S1  | 0          | 1   |

The state machine is described with two processes. One process defines the next state assignments (state registers) and the other process describes the combinatorial portion of the design that determines the state assignment.

In the following examples, the signal type, "pres\_state," defines the current state of the state machine and the signal, "next\_state," defines the next state of the state machine, depending on the current state and input. A reset assignment sets the state machine to the state "S0."

### Verilog

```

module mealy_ent ( a, clock, reset, z );

input a, clock, reset;

output z;

reg [1:0] pres_state, next_state;

reg z;

parameter S0 = 2'b00, S1 = 2'b01, S2 = 2'b10;

always @ (posedge clock or negedge reset )

if (!reset) pres_state = 2'b00;

else

pres_state = next_state;

always @ (pres_state)

case (pres_state) //synopsys parallel_case full_case

S0 : if (a)

begin

next_state = S1;

z = 1'b0;

end

else

begin

next_state = S0;

z = 1'b0;

end

S1 :if (a)

begin

next_state = S2;

z = 1'b0;

else

begin

```

next\_state = S1;

```

z = 1'b1;

end

S2 : if (a)

begin

next_state = S1;

z = 1'b1;

end

else

begin

next_state = S0;

z = 1'b0;

end

endcase

end

endmodule

VHDL

library ieee;

use ieee.std_logic_1164.all;

entity mealy_ent is

port (

: in std_logic;

clock : in std_logic;

reset : in std_logic;

: out std_logic);

end mealy_ent;

architecture mealy_arc_d of mealy_ent is

type state_type is (s0, s1, s2);

signal pres_state, next_state :state_type;

begin

--next state assignment; synchronizing process

sync: process (reset, clock)

begin

if ( reset = '0' ) then

pres_state <= s0;--async reset

else

if (clock'event and clock='1')then

pre_state <= next_state;--assign next state</pre>

end if;

end if;

```

```

end process sync;

--process to hold combinatorial logic that determines the

--next_state

comb: process (pres_state, a)

begin

case pres_state is

when s0 =>

if (a='0')then

z <= '0';

next_state <= S0;</pre>

else

z <= '0';

next_state <= s1;</pre>

end if;

when s1 =>

if (a='0')then

z <= '1';

next_state <= s1;</pre>

else

z <= '0';

next_state <= s2;</pre>

end if;

when s2 =>

if (a='0')then

z <= '0';

next_state <= s0;</pre>

else

z <= '1';

next_state <= 1;</pre>

end if;

end case;

end process comb;

```

end mealy\_arc\_d;

# Extracting an FSM from a Sequential Design

After completing the behavioral description of the state machine, you must select the state machine style. Use the following procedure to extract and optimize designs. You can use this procedure when the entire design is the state machine or when the state machines registers are buried within the context of a larger design:

**1. Read design.** Type one of the following commands at the prompt:

```

read -f vhdl state.vhd /* for vhdl */

read -f verilog state.v /* for verilog */

```

**2. Set the current design to your state machine.** Type the following command at the prompt:

```

current_design = mealy_ent

```

**3. Set the clock constraints.** Type the following commands at the prompt:

```

create_clock -period 10 -waveform {0 5} clock

dont_touch_network clock

set drive 0 clock

```

**4. Map the design.** If the design is not mapped, run compile to map the design to gates. Type the following command at the prompt:

```

compile -map effort medium

```

**5. Define variables.** Define the variables that identify the state register names and find the state registers in the design. Type the following commands at the prompt:

```

state_reg_name = pres_state

state_regs = find (cell, state_reg_name + "*")

```

**6. Group the FSM.** If the entire design is a state machine, this step is optional. Grouping the FSM section of a circuit produces a new level of hierarchy containing just the FSM state vector flip-flops and their associated logic. The new design is still in netlist format. If all flip-flops in the design are not part of the state machine, Type the following command at the prompt to allow the compiler to identify the state registers:

```

set_fsm_state_vector state_regs

```

**7. Group the FSM subset of the design.** Type the following command at the prompt:

```

group -fsm -design_name mealy_ent_fsm

```

**8. Set the current design to the FSM section of the design.** Type the following command at the prompt:

```

current_design = mealy_ent_fsm

```

9. Extract FSM. Extracting an FSM from a circuit changes the representation from a netlist format to FSM "state\_table" format. For specific optimization methods, refer to the *Design Compiler Reference Manual*. Type the following command at the prompt:

```

extract

```

The remaining steps only describe the one-hot encoding methods.

**10. Specify the state vector flip-flops.** Type the following command at the prompt:

```

set_fsm_state_vector state_regs

```

The order of the flip-flops must agree with the order of the state vector bits (i.e., each bit in the state vector represented by one flip-flop order).

**11. (Optional) Set the state encoding.** Type the following command at the prompt:

```

set_fsm_encoding "s0=0", "s1=1", ...

```

State encoding provides the Design Compiler with the names and values of each state.

**12. Extract the FSM.** Extracting the FSM converts the circuit into an FSM. Type the following command at the prompt:

extract

**13. Minimize the state-transition logic.** Type the following command at the prompt:

```

reduce fsm

```

# Manual One-Hot State Encoding

Actel does not recommend using the manual one-hot encoding in HDL. This method produces inefficient state machines.

# Automatic FSM Encoding Styles

The (V)HDL Compiler can automatically select the most appropriate encoding style by selecting auto as the encoding style. Type the following commands to let (V)HDL Compiler select the encoding style:

```

set_fsm_encoding { }

set_fsm_encoding_style auto

```

This encoding style uses a proprietary algorithm. This algorithm's primary objective is to determine a set of encoding that reduces the complexity of the combinatorial logic while using minimum number of encoding bits. Consequently, this encoding style is targeted for area optimization as smaller area reduces delay. The maximum supported state vector length for automatic encoding is 30 bits.

# Multiple Resets in FSM

The FSM compiler may not generate optimal results with multiple resets in the FSM. If you are using multiple resets, add "AND" statements to the reset signals in a separate module so that the state machine has a single reset.

#### Moore is Less

The Moore state machine includes fewer states than the Mealy state machine because the outputs are derived solely from the present state of the flip-flops. The Mealy state machine's outputs are determined by the state of the flip-flops and the inputs.

# Power On and Reset

For simulation, the state machine initializes into the left most value of the enumeration type. However, for synthesis, the state where the machine powers on is not clear. Because (V)HDL Compiler performs state encoding on the machine's enumeration type, the state machine may power on in a state not defined in HDL. Therefore, to achieve simulation and synthesis consistency, it is important to supply a reset to the state machine.

If you want to perform one-hot encoding, you must supply the state machine with a reset. Remember that only one register must be active. All other registers must be reset or inactive. Make sure that no logic exists on the reset network. You can use the "dont\_touch\_network" command to ensure that no logic is generated for the reset network.

# DesignWare Module Coding

Through inference, Synopsys can synthesize efficient design modules from HDL operators. However, in most cases the designs are not optimal implementations for the Actel architecture. To maximize performance, use the Actel DesignWare libraries.

The Actel DesignWare libraries support synthetic modules such as adders, subtractors, comparators, incremeters, decremeters and counters. These modules are optimized for the Actel architecture.

Note: To target the 1200XL family, synthesize using the ACT 2 library and use the "XL" operating condition for timing Refer to "Synthesis Library Operating Conditions" on page 96 for information.

You can use Actel DesignWare library components in the following ways.

**Method A:** You can allow Synopsys to infer the best implementation for the HDL operator. Synopsys makes a decision based on the design's area and timing constraints. Actel DesignWare library modules are selected only if there are strict timing constraints and if the modules are in the critical path.

**Method B:** You can select a specific arithmetic implementation (+, -) or logical operator  $(<, \le, >, \ge)$  by explicit statements enclosed within comment characters.

**Method C:** You can manually instantiate the DesignWare library modules by name. You must already know the parameters for module instantiation. Currently, Actel only offers counters for instantiation.

The following examples show how Method A, Method B, and Method C are applied to select the Actel DesignWare library modules. The examples in this chapter are located in the following directory:

```

$ACT_SYNOPDIR/tutorial/designware

```

Refer to "DesignWare Library Information" on page 99 for additional information.

#### **Adders**

There are three types of DesignWare adders: RIPADD (ripple carry adder), MFADD (medium fast adder), and FADD (fast adder). Bit vectors range from 2 to 32.

#### Method A

The following example shows how to implement a Verilog 16-bit adder using Method A.

```

// verilog/add16.v

module adder (c, a, b);

input[15:0]a, b;

output[15:0]c;

wire[15:0]a, b, c;

assign c=a+b;

```

#### endmodule

The following example shows how to implement a VHDL 8-bit adder with carry in "cin" and carry out "cout" using Method A:

```

-- vhdl/add_c.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity adder is

generic (width : integer := 8);

port (a, b: in unsigned (width-1 downto 0);

cin: in std_logic;

cout: out std_logic;

```

```

y: out unsigned (width-1 downto 0));

end adder;

architecture rtl of adder is

begin

process (a,b,cin)

variable temp_a,temp_b,temp_y:unsigned(a'length downto 0);

begin

temp_a := '0' & a;

temp_b := '0' & b;

temp_y := temp_a + temp_b + cin;

y <= temp_y(a'length-1 downto 0));

cout <= temp_y(a'length);

end process;

end rtl;</pre>

```

The following design script file compiles the preceding HDL descriptions. The constraint forces Synopsys to use a Actel DesignWare adder instead of a Synopsys adder:

```

/* adder.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

/* use the following line to read Verilog source code */

read -format verilog add16.v

/* use the following line to read VHDL source code */

read -format vhdl add_c.vhd

current_design = adder

set_max_delay 10 -from all_inputs() -to all_outputs()

set_operating_conditions MILBC-3

compile

write -hierarchy -format db -output adder.db

exit

```

#### Method B

The following example shows how to implement a Verilog 32-bit adder using Method B. The text enclosed in the comment line (/\* \*/) allows Synopsys to choose the adder's FADD implementation. You can select "a1" as the arithmetic operation of the FADD description (DWACT\_ADD).

```

module adder (clk, reset, dataa, datab, sum, cout);

output [31:0] sum;

output cout;

input [31:0] dataa, datab;

input clk, reset;

// *******declare output types*******

wire [31:0] sum;

wire cout;

// *******declare internal types******

reg [31:0] suminternal;

assign sum[31:0] = suminternal[31:0];

assign cout = suminternal[31]

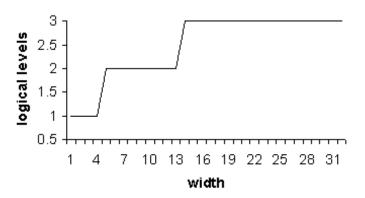

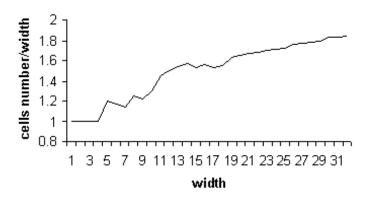

always @(posedge clk or negedge reset)

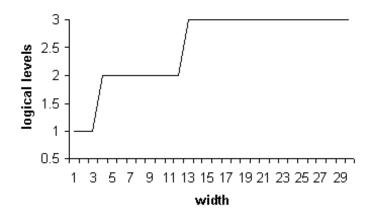

begin

if (reset == 0)

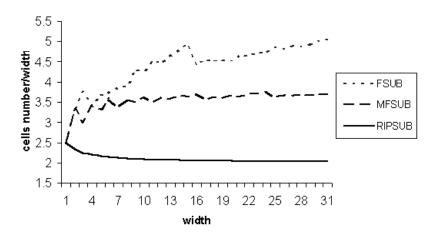

suminternal[31:0] <= 32'b0;

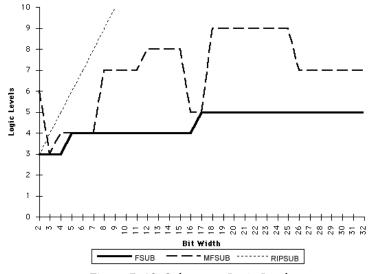

begin : lab_1

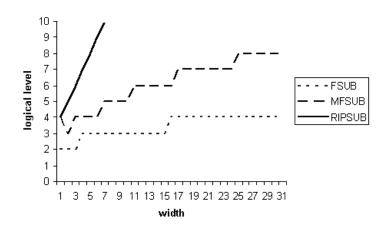

/*

synopsys resource r0:

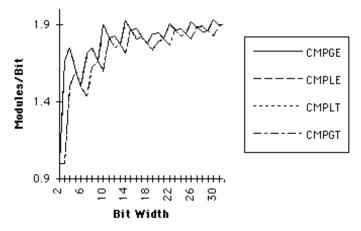

map_to_module = "DWACT_ADD"

implementation = "FADD"

ops = "lab 2";

suminternal[31:0] <= dataa[31:0] + datab[31:0];</pre>

//synopsys label lab_2

end

end

endmodule

```

The following example shows how to implement a VHDL 4-bit adder using Method B:

```

-- vhdl/fadd4.vhd

library ieee, dwact, synopsys;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use synopsys.attributes.all;

use dwact.dwact_components.all;

entity adder is

port ( a, b : in unsigned (3 downto 0);

```

```

c :out unsigned (3 downto 0)

);

end adder;

architecture impl1 of adder is

begin

process(a,b)

constant r0: resource :=0;

attribute map_to_module of r0: constant is "dwact_add";

attribute implementation of r0: constant is "fadd";

attribute ops of r0: constant is "a1";

begin

c <= a+b; -- pragma label a1

end process;

end impl1;

The following design script file compiles the preceding HDL

descriptions:

/* fadd.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

/* use the following line to read Verilog source code */

read -format verilog fadd32.v

/* use the following line to read VHDL source code */

read -format vhdl fadd4.vhd

current_design = adder

set_operating_conditions INDTC-2

compile

report_area > adder.area

write -hierarchy -format db -output adder.db

```

exit

### **Subtractors**

There are three types of DesignWare subtractors: RIPSUB (ripple carry subtractor), MFSUB (medium fast subtractor), and FSUB (fast subtractor). Bit vectors range from 2 to 32.

#### Method A

The following example show how to implement a Verilog 16-bit subtractor using Method A:

```

// verilog/sub16.v

module sub (c, a, b);

input[15:0]a,b;

output[15:0]c;

wire[15:0]a,b,c;

assign c = a-b;

endmodule

```

The following example shows how to implement a VHDL 10-bit subtractor using Method A.

```

-- vhdl/sub10.vhd

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity sub is

port (in1, in2: unsigned (9 downto 0);

diff: out std_logic_vector (9 downto 0));

end sub;

architecture impl1 of sub is

begin

diff <= in1 - in2;

end impl1;</pre>

```

The following design script file compiles the preceding HDL descriptions. This script file allows timing constraint on input to output. The constraint forces synthesis of an Actel DesignWare subtractor instead of a Synopsys subtractor.

```

/* subt.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

/* use the following line to read Verilog source code */

read -format verilog sub16.v

/* use the following line to read VHDL source code */

read -format vhdl sub10.vhd

current_design = sub

set_max_delay 10 -from all_inputs() -to all_outputs()

set_operating_conditions COMWCSTD

compile

write -hierarchy -format db -output sub.db

exit

```

#### Method B

The following example shows how to implement a Verilog 16-bit subtractor using Method B. The text enclosed in the comment line (/\* \*/) allows Synopsys to choose the subtractor's FSUB implementation. You can select "a1" as the arithmetic operation of the FSUB description (DWACT\_SUB).

```

// verilog/fsub16.v

module sub (c, a, b);

input[15:0]a, b;

output[15:0]c;

wire[15:0]c;

wire[15:0]c;

always @ (a or b)

begin: blk01

/* synopsys resource r0:

map_to_module = "DWACT_SUB",

implementation = "FSUB",

ops = "al";

*/

c = a - b; //synopsys label al

end

endmodule

```

The following example shows how to implement a VHDL 4-bit subtractor using Method B.

```

-- vhdl/fsub4.sub

library ieee, dwact, synopsys;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use synopsys.attributes.all;

use dwact.dwact_components.all;

entity sub is

port ( a, b : in unsigned (3 downto 0);

c :out unsigned (3 downto 0)

end sub;

architecture impl1 of sub is

begin

process(a,b)

constant r0: resource :=0;

attribute map_to_module of r0: constant is "dwact_sub";

attribute implementation of r0: constant is "mfsub";

attribute ops of r0: constant is "a1";

c <= a-b; -- pragma label a1

end process;

end impl1;

```

The following design script file compiles the preceding HDL descriptions:

```

/* fsub.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

/* use the following line to read Verilog source code */

read -format verilog fsub16.v

/* use the following line to read VHDL source code */

read -format vhdl fsub4.vhd

current_design = sub

set_operating_conditions COMWCSTD

compile

write -hierarchy -format db -output sub.db

exit

```

# **Comparators**

There are four types of DesignWare comparators available for different HDL operations: less than, greater than, less than equal to, and greater than equal to. Refer to "DesignWare Library Comparators" on page 102 for additional information.

#### Method A

The following example shows how to implement a Verilog 16-bit comparator using Method A:

```

// verilog/comp16.v

module comp (c, a, b);

input [15:0]a, b;

output c;

wire [15:0]a,b;

wire c;

assign c = (a < b);

endmodule</pre>

```

The following design script file compiles the preceding HDL descriptions. The constraint forces synthesis of an Actel DesignWare comparator instead of a Synopsys comparator.

```

/* comp16.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

read -format verilog comp16.v

current_design = comp

set_max_delay 10 -from all_inputs() -to all_outputs()

set_operating_conditions COMWCSTD

compile

write -hierarchy -format db -output comp.db

exit

```

#### Method B

The following example shows how to implement a Verilog 16-bit comparator using Method B. The text enclosed in the comment line (/\* \*/) allows Synopsys to choose the comparator's FCOMP implementation. You can select "a1" as the arithmetic operation of the FCOMP description (DWACT\_CMPLT).

```

// verilog/fcomp16.v

module comp (c, a, b);

input [15:0]a,b;

output c;

wire [15:0]a, b;

regc;

always @ (a or b)

begin : blk01

/* synopsys resource r0:

map_to_module = "DWACT_CMPLT",

implementation = "FCOMP",

ops = "al"

*/

c <= (a < b); //synopsys label al

end

endmodule</pre>

```

The following design script file compiles the preceding HDL descriptions:

```

/* fcomp16.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

read -format verilog fcomp16.v

current_design = comp

set_operating_conditions COMWCSTD

compile

write -hierarchy -format db -output comp.db

exit

```

## Counters

Counters are only available for instantiation. Refer to "DesignWare Library Counters" on page 103 for names and descriptions of the available DesignWare counters.

#### Method C

The following example shows how to instantiate a Verilog 8-bit up counter using Method C.

```

// verilog/count8.v

module count (data, q, sload, enable, aclr, clock);

input [7:0]data;

input sload, enable, aclr, clock;

output [7:0]q;

dwact_up_ctr #(8) u0( data, q, sload, enable, aclr, clock);

endmodule

```

Note: The variable "# (8)" defines the counter's bit width. Refer to "DesignWare Library Counters" on page 103 or the "DWACT\_components.vhd" file located in the "\$ACT\_SYNOPDIR/syn/<act\_fam>/dwact" directory for pin ordering information.

The following example shows how to implement a VHDL 10-bit counter using Method C.

```

-- vhdl/count10.vhd

library ieee, dwact, synopsys;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use synopsys.attributes.all;

use dwact.dwact_components.all;

entity count is

port ( data :in std_logic_vector (9 downto 0);

load, cen, reset, clk:in std_logic;

q :out std_logic_vector (9 downto 0)

);

end count;

architecture impl1 of count is

attribute implementation of u0: label is "tlacnt";

begin

u0: dwact_dn_ctr

```

### Chapter 3: Actel-Synopsys Coding Considerations

```

generic map (width => 10)

port map (

data => data,

q => q,

load => load,

cen => cen,

reset => reset,

clk => clk

);

end impl1;

```

The following design script file compiles the preceding HDL descriptions:

```

/* counter.scr */

script_lib = get_unix_variable ("ACT_SYNOPDIR")

include script_lib + /scripts/<act_fam>/actsetup.scr

/* use the following line to read Verilog source code */

read -format verilog count8.v

/* use the following line to read VHDL source code */

read -format vhdl count10.vhd

current_design = count

dont_touch count

set_operating_conditions COMTC-1

compile

write -hierarchy -format db -output count.db

exit

```

### Incrementers