ASICmaster™ User's Guide

# PRE-PRODUCTION For the latest version of this document, check the User area on Actel's website at:

http://www.actel.com/user

Windows® NT™ and UNIX® Environments

## Actel Corporation, Sunnyvale, CA 94086

© 1999 Actel Corporation. All rights reserved.

Printed in the United States of America

Part Number: 5579018-0

Release: June 1999

No part of this document may be copied or reproduced in any form or by any means without prior written consent from Actel.

Actel makes no warranties with respect to this documentation and disclaims any implied warranties of merchantability or fitness for a particular purpose. Information in this document is subject to change without notice. Actel assumes no responsibility for any errors that may appear in this document.

This document contains confidential proprietary information that is not to be disclosed to any unauthorized person without prior written consent from Actel Corporation.

#### Trademarks

Actel and the Actel logotype are registered trademarks of Actel Corporation.

ProASIC and ASICmaster are trademarks of Gatefield Corporation.

Adobe and Acrobat Reader are registered trademarks from Adobe Systems, Inc.

Verilog is a registered trademark of Open Verilog International.

UNIX is a registered trademark of X/Open Company Limited.

Windows is a registered trademark and Windows NT is a trademark of Microsoft Corporation in the U.S. and other countries.

All other products or brand names mentioned are trademarks or registered trademarks of their respective holders.

|   | Introduction                                             |

|---|----------------------------------------------------------|

|   | Document Organization                                    |

|   | Document Assumptions                                     |

|   | Documentation Conventions                                |

| 1 | ASICmaster Overview                                      |

|   | Design Flow Illustrated                                  |

|   | ASICmaster Task Flows and Iterations                     |

|   | Design Integrity                                         |

|   | Design Hints                                             |

|   | Using ProASIC Global Routing Resources                   |

|   | Implementing Memories                                    |

| 2 | Using ASICmaster                                         |

|   | Invoking ASICmaster                                      |

|   | Starting a Project Work Session                          |

|   | Design Executive Window                                  |

|   | Setting Design Project Preferences and Managing Files 16 |

|   | Selecting Tasks                                          |

|   | Specifying Netlist Formats                               |

|   | Selecting Netlists                                       |

|   | Specifying the Top Cell and Top Library                  |

|   | Specifying a ProASIC Device                              |

|   | Selecting Constraint Files                               |

|   | Specifying Place and Route Options                       |

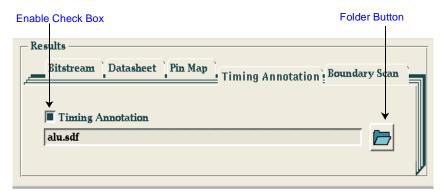

|   | Enabling Delay Calculation and File Generation           |

|   | Setting Operating Conditions                             |

|   | Setting the Text Editor                                  |

|   | Saving Designs                                           |

|   | Running an ASICmaster Task Cycle                         |

| 3 | Viewing Results                                          |

| ~ | Viewing Report Files                                     |

|   | Session Report                                              | 39  |

|---|-------------------------------------------------------------|-----|

|   | Command Report                                              | 41  |

|   | Task Reports                                                | 42  |

|   | Viewing Output Data Files                                   | 45  |

|   | Viewing the Design Layout                                   | 48  |

|   | Viewer Menu Commands                                        | 58  |

| 4 | Using Constraints                                           |     |

|   | Types of Constraints                                        | 63  |

|   | Timing Constraints.                                         | 63  |

|   | Constraint File Syntax                                      | 64  |

|   | Global Resource Constraints                                 | 67  |

|   | Netlist Optimization Constraints                            | 71  |

|   | Placement Contraints                                        | 73  |

|   | JTAG Constraints                                            | 81  |

| 5 | Back Annotating Timing Information                          | 83  |

|   | Generating a Timing File                                    | 84  |

|   | Back Annotating Post-Layout Delays in the CAE Environment . | 86  |

| 6 | Using ASICmaster in TTY and Batch Modes                     |     |

|   | Command Line Options                                        | 87  |

|   | Using TTY Mode                                              |     |

|   | Using Batch Mode                                            |     |

|   | Creating a Batch Script File.                               | 89  |

|   | TTY and Batch Commands                                      | 93  |

|   | Specifying Tasks.                                           | 93  |

|   | The Set Command                                             | .05 |

| 7 | Troubleshooting                                             | 09  |

|   | General Optimization and Troubleshooting Guidelines1        |     |

|   | Correcting Netlist and Design Problems                      | 09  |

|   | Common Problems and Solutions                               | 11  |

|   | Common Simulation Problems and Solutions                    | 14  |

|   | Correcting Place and Route Problems       |

|---|-------------------------------------------|

|   | Common Error Messages                     |

|   | Back Annotation Problems                  |

| A | File and Command Selection                |

|   | Using File Extensions                     |

|   | Restricting the Types of Files Listed     |

|   | Traversing Directories                    |

|   | Using Mnemonics and Keyboard Accelerators |

|   | Keeping Pull-Down Menus Displayed         |

|   | Using the Escape Key to Cancel Displays   |

| В | Supported Netlist Formats and Constructs  |

|   | Netlist Formats Accepted by ASICmaster    |

|   | Netlist Constructs Supported              |

| С | The Design (*.dtf) Directory              |

|   | Files Created by ASICmaster               |

|   | designState File Contents                 |

| D | Batch Script Syntax                       |

| E | The .amrc Startup File                    |

|   | Parameters for the Design Executive       |

|   | Parameters for the Netlist Importer       |

|   | Parameters for the Viewer                 |

| F | Product Support                           |

|   | Actel U.S. Toll-Free Line                 |

|   | Customer Service                          |

|   | Customer Applications Center              |

|   | Guru Automated Technical Support          |

|   | Web Site                                  |

|   | FTP Site                                  |

|   |                                           |

| Electronic Mail |           |     |   | • |   |   |   |   |   |   |   | • |   |   |   | • |   |   | .155 |

|-----------------|-----------|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|------|

| Worldwide Sale  | s Offices |     | • | • |   |   |   |   |   |   |   |   | • | • |   |   |   |   | .156 |

| Indon           |           |     |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   | 1    |

| Index           |           | • • | · | • | • | · | • | · | • | · | · | · | · | · | • | • | · | · | .15/ |

# List of Figures

| ASICmaster Design Flow                                 |

|--------------------------------------------------------|

| Main Menu and Copyright Information Window             |

| Tools Menu Window       11                             |

| Design Selection File Browser                          |

| Design Executive Window                                |

| The Tasks Menu                                         |

| The Tasks Selection List                               |

| Design Options Window                                  |

| Design Executive Window Input Area                     |

| Netlist File Selection Browser   23                    |

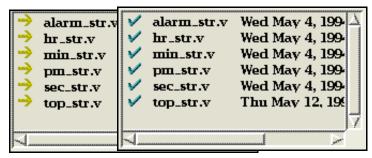

| Netlist Files Before and After You Import the Netlists |

|                                                        |

| Part Selection Browser                                 |

| Results Area of the Design Executive Window            |

| Operating Conditions                                   |

| User Options Window                                    |

| Sample Session Report                                  |

| Starting a ASICmaster Task Run                         |

| Task Selection List                                    |

| Power Estimation Window                                |

| View Menu                                              |

| Session Report                                         |

| Command Report Window                                  |

| Sample Netlist Report                                  |

| View menu                                              |

| Sample Datasheet                                       |

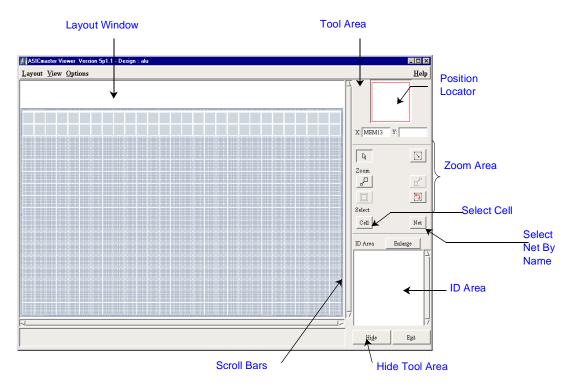

| ASICmaster Viewer Window                               |

| Position Indicator                                     |

| The Select Net By Name Window                          |

| Options Window                                         |

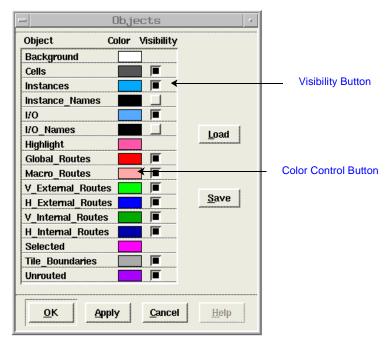

| The Objects Window                                     |

| Printer Window                                         |

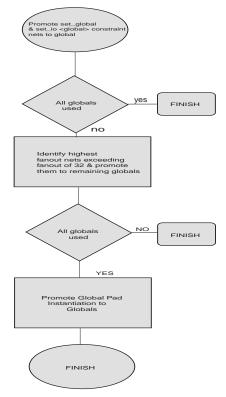

| Promotion Scheme                                       |

## List of Figures

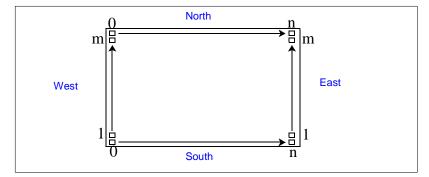

| Pad Locations                                     |

|---------------------------------------------------|

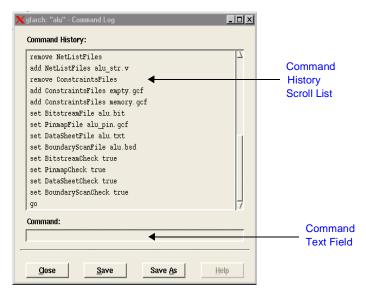

| Design Executive Window                           |

| Tasks Selection Window                            |

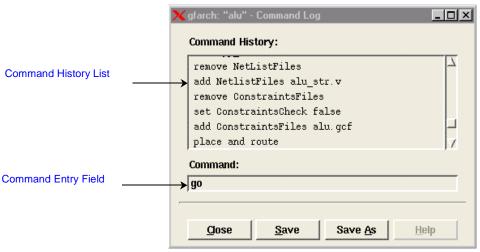

| Command Log Window                                |

| Batch Script Sample                               |

| Filter Menu on Design Selection File Browsers     |

| Tools for Traversing Directories                  |

| Directory Hierarchy Pop-up Menu Selection         |

| Expanded Design Selection File Browser            |

| History Menu on the Design Selection File Browser |

| Identifying Mnemonics and Keyboard Accelerators   |

| A Tear-Off Menu                                   |

| A Torn-Off Menu                                   |

| Default .amrc File                                |

# List of Tables

# Introduction

ASIC master is a layout system that reads structural netlists and produces optimal design layouts for Actel's ProASIC devices using timing driven place and route.

The *ASICmaster User's Guide* contains information and procedures for using ASICmaster to place and route designs for Actel's ProASIC family of devices. This includes an overview of ASICmaster and the design flow and information about using ASICmaster for layout, delay calculation, and program file generation.

Also is included information about viewing the results of place and route, and information about generating place and route constraint files and post layout back annotation files for timing simulation. Additionally, information about using ASICmaster in command line and batch is included.

# Document Organization

The ASIC master User's Guide is divided in to the following chapters:

**Chapter 1** - **ASICmaster Overview** describes the design flow and outlines the tasks that can be performed using ASICmaster.

**Chapter 2 - Using ASIC master** explains how to use ASIC master to select a design and start a design project work session. It also describes how to use basic Design Executive tools, set project preferences, place and route a design, and generate files, such as the bitstream device programming file.

**Chapter 3** - **Viewing Results** describes how to view ASIC master results, including layout views, output data, and log files.

**Chapter 4** - **Using Constraints** describes how to create place and route constraint files for ASICmaster.

**Chapter 5 - Timing Analysis** explains how to calculate post-layout delays and perform back annotation.

**Chapter 6 - Using the ASIC master in TTY and Batch Modes** describes how to use ASIC master in interactive command-line mode and batch mode.

#### Introduction

**Chapter 7** - **Troubleshooting** presents useful hints and advice for successful operation.

**Appendix B- File and Command Selection** describes user interface features not covered in other chapters.

**Appendix B** - **Supported Netlist Formats and Constructs** describes netlist formats and the constructs supported by ASICmaster.

**Appendix C** - **The Design (\*.dtf) Directory** explains the contents of the .dtf design directory. Each .dtf directory contains an ASIC master database for a design.

**Appendix D** - **Batch Script Syntax** describes the syntax for batch scripts that run ASICmaster.

**Appendix E** - **The .amrc Startup File** describes the .amrc file used to configure ASICmaster.

**Appendix F - Product Support** provides information about contacting Actel for customer and technical support.

# Document Assumptions

The information in this guide is based on the following assumptions:

- 1. You have installed the ASIC master software.

- 2. You are familiar with the principles of digital design.

- 3. You are familiar with UNIX or Microsoft Windows NT operating systems.

# Documentation Conventions

Unless otherwise noted in the text, this guide follows these documentation conventions:

Information that is meant to be input by the user is formatted as follows:

- *Italic* type is used in text, syntax, and examples to identify placeholders that need to replaced with specific words or values. It is also used selectively for emphasis.

- <> (angle brackets) identify a key or key combination that to press, such as <g>, <Return> or <Ctrl+g>. (Ctrl refers to the Control key.)

- ASICmaster graphical user interfaces and the documentation conventions used in the Actel documentation represent <Ctrl>-*key* and <Alt>-*key* sequences in slightly different ways.

- For example:

- To indicate holding down the <Ctrl> key and pressing the <g> key, the *interfaces* use <Ctrl+G>.

- To indicate holding down the <Ctrl> key and pressing the <g> key, the *manual* uses <Ctrl+g>.

- To indicate holding down the <Ctrl> and <Shift> keys while pressing the <g> key, the *interfaces* use <Ctrl+Shift+G>.

- To indicate holding down the <Ctrl> and <Shift> keys while pressing the <g> key, the *manual* uses <Ctrl+Shift+G>.

[] (square brackets) enclose lists of optional items.

{ } (braces) enclose lists of required items.

| (vertical bar) separates:

# **ProASIC Series Manuals**

This book is a part of the ProASIC series of manuals. All books in the series are listed below. Users can order these publications through an Actel sales representative.

ASICmaster Installation and Licensing Guide provides information and procedures for installing and licensing the ASICmaster software.

*ASICmaster User's Guide* provides information about the design flow for creating designs for ProASIC device. It includes information and procedures for placing and routing designs and also information on using timing constraints.

*MEMORYmaster User's Guide* provides information and procedures for generating embedded and distributed memories and instantiating then into a design.

*ProASIC Macro Library Guide* provides descriptions of ProASIC library elements for Actel's ProASIC device families. Symbols, truth tables, and timing parameters are included for all macros.

*ProASIC Interface Guide* provides information and procedures for designing Actel's ProASIC devices in Exemplar synthesis, Synopsys synthesis, Verilog simulation, and VHDL simulation environments.

# **ASICmaster Overview**

This chapter describes the design flow for creating designs for Actel ProASIC devices using ASIC master and third-party tools. It also describes the tasks, task cycles, and iterations to perform in ASIC master.

# Design Flow Illustrated

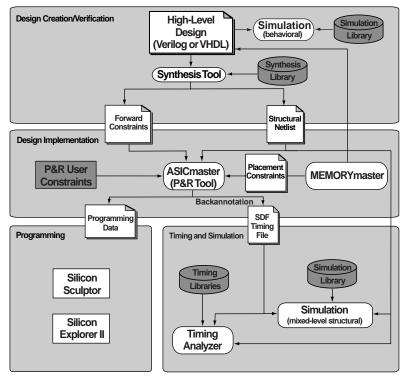

Figure 1-1 shows the design flow for an Actel ProASIC device using ASICmaster and third-party software.

Figure 1-1. ASICmaster Design Flow

# ASICmaster Task Flows and Iterations

This section describes the steps that are typically performed with ASICmaster after a design has been created for a ProASIC device, synthesized, and a netlist generated.

- 1. Start a project, set project preferences and select a device.

- 2. Import and check the netlist and constraint files.

- 3. Place and route the design. ASICmaster is also used to iterate the device-selection and/or netlist-import cycles (and, if necessary, the design analysis, design synthesis, and/or design definition processes).

- 4. Generate post-layout delays and timing back annotation files for simulation/timing analysis.

- 5. Use third-party tools to perform simulation and timing analysis using the post-layout delays. As needed, iterate the design analysis, device-selection, layout, and/or file-generation cycles (and, if necessary, the design synthesis and/or design definition processes).

- 6. Generate device programming bitstream file.

- 7. Program the device using one of the supported device programmers.

- 8. Generate the design datasheet, boundary scan file and pin map.

### Starting a Project

After launching ASICmaster, the first task is setting the layout and device programming project preferences for the design to create a design database. ASICmaster uses the project preferences to add parameters to the database, control task operations, and alert users to potential and actual problems. It is important that ASICmaster has as much information as possible about the environment in which the design is being created. Project preferences to set include specifying the netlist that describes the design, the ProASIC device for the design implementation, the timing and back annotation file, and the pin-out file.

Additionally, specifying anticipated operating conditions, including temperature, voltage, and process allows ASICmaster to use the operating conditions as additional timing parameters to calculate post-layout delays

After successful timing verification and post-layout, the datasheet and the bitstream programming file are added to the JTAG file as additional project preferences.

# Importing a Netlist

The netlist is the design information source for the project. Netlists can be in EDIF 2.0.0, VHDL, or Verilog format. Only one format can be used for a design. When a netlist is imported, ASICmaster checks the netlist format and design rules, imports the netlist and constraint files specified during project set up, and incorporates the data into the design project database. ASICmaster also checks the constraint files for the following:

- Verifies whether the design and device are compatible in terms of gate and I/O counts.

- Develops optimal parameters for the use of global resources and assigns them to high fanout nets when appropriate.

- Checks for consistency between the design and the project setup and physical design parameters and constraints.

- Optimizes the design by removing redundant, non-functioning, and non-required logic. critical path nets are shielded by inserting buffers to disconnect the path from high fanout loading.

## Error Detection and Reporting

If errors are detected in a netlist, device, or constraint file, a message is displayed and the task run is terminated. Common reasons for failure are:

- One (or more) netlist file is in an unsupported format.

- The netlist files are not all in the same format.

- One (or more) netlist file fails a design rule or electrical check.

- The device and the netlists are incompatible in terms of gate count or I/O resources.

- Constraints are incompatible with the design description, device characteristics, or both.

The error report can be viewed to determine the cause of the error. Refer to "Viewing Results" on page 39 for additional information. Reports can also be viewed to get more information about the operation as a whole, including information on system warning messages.

### Place and Route

The main function of ASIC master is to place and route a design to yield the desired circuit performance. After the netlist and constraint files are successfully imported, all the information necessary to guide a favorable place and route task has been collected. The following sections summarize the layout-related operations and indicate task iterations that might be performed to optimize task results.

## Mapping Package I/O Pins to I/O Signals

When ASIC master imports the netlist and device data, it automatically checks I/O requirements. The placement program automatically places each I/O signal in the optimum position for successful operation.

Manual assignment can also be performed using constraint files. Refer to "Using Constraints" on page 63 for additional information.

Note: A single output signal can be allocated to multiple output buffers to increase drive strength.

## Avoiding Excessive Constraints

The usual reason for routing failure is that the design has been over constrained through too stiff timing budgets or fixed placements. Avoid over constraining designs, especially for the first few runs of a design. Constraints limit ASICmaster's ability to create optimal physical layouts. Specific constraints can be added later to supplement the design parameters that ASICmaster automatically generates and to guide place and route.

| Generating and<br>Back<br>Annotating<br>Delays | After achieving a satisfactory layout, post-layout delays can be generated<br>and a back annotation file can be created if post-layout delay calculation is<br>enabled. The post-layout calculation extracts pin-to-pin, interconnect net<br>information, and RC data and performs delay analysis on each net and<br>generates a back annotation file in SDF format. |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                | This information is used to verify a design during simulation/timing<br>analysis. If the simulation/analysis results indicate problems, the design<br>should be put through synthesis and design definition cycles before<br>repeating the layout cycle and any required ASICmaster tasks.                                                                           |

| Design<br>Optimization                         | ASIC master report files and iterating tasks should be used to optimize the design. When iterating only to optimize the design after a previously successful layout, all subsequent processing usually succeeds. If the design                                                                                                                                       |

has only minor changes users can recycle the previous placement in an ECO mode and run placement refinement.

#### **Optimizing Inverters**

If ASIC master is run with Netlist Optimization enabled, (default mode) inverters that do not limit fanout are removed from the design netlist.

#### **Timing Optimization**

Timing optimization can be performed by iterating the design analysis and layout cycle on a design until it meets timing and layout requirements. Refer to "Back Annotating Timing Information" on page 83 for additional information.

## Generating Files

Once the design meet timing and layout requirements, the device programming bitstream, datasheet, JTAG and pin map files can be generated. Refer to "Design Executive Window" on page 14 for additional information.

# Design Integrity

ASICmaster offers a combination of safeguards that protect the integrity of a design, and flexibility to override the safeguards when necessary. ASICmaster keeps track of a design project and ensures that follow the design flow is followed to maintain the integrity of the project database and to keep the design project synchronized with the design state.

By default the system performs tasks in the order shown in the task list in "ASICmaster Task Flows and Iterations" on page 2 using the results from each stage as input for the next stage. Additionally, only tasks required to produce the stated outputs are performed and users are prompted for required inputs for each task.

Although ASIC master performs tasks in a specific order, the system can perform a subset of these operations to suit the current design state unless an operation violates one of the safeguards.

For example, if a design is placed and routed but post-layout delays violate timing requirements, ASICmaster can be directed to only optimize place and route and recalculate the delays. File checking or any other task previously is not repeated unless any of the input files have also changed between runs.

ASIC master processes a design incrementally by default. It keeps track of successfully completed tasks and does not repeat them. If prerequisites for a task are missing, the system either automatically supplies them or prompts the user to supply them.

# Design Hints

The design netlist is the main input for ASICmaster. When creating a design, device usage and ASICmaster features can be maximized by using the following the guidelines:

- Use standard design practices.

- Use the automatic global resource assignments that ASIC master makes and, if appropriate, add constraints.

- Use the automatic mapping that ASIC master makes between package pins and the design's I/O signals and, if appropriate, add constraints.

- Avoid over constraining a design so that ASICmaster can apply its algorithms to the best advantage for place and route.

- Implement tristates, memories, and hierarchical blocks with ASICmaster-supported elements.

- Create well structured and well organized design descriptions.

- Avoid asynchronous designs. They are difficult to verify, are less robust, and typically include problems such as hazard and race conditions.

- When gating clocks, ensure that the gate signals are stable when the clock is active. Otherwise, glitches might be propagated through the circuit.

- Use a minimum of logic before the first flip-flop or after the last flip-flop on signals that are to be driven on or off chip to provide as much time as possible to drive the signal off the chip and onto the next chip.

• To ensure that process variations do not adversely affect reliability, always design with worst-case processes in mind.

# Using ProASIC Global Routing Resources

Use the automatic global resource assignments that ASICmaster makes. Each ProASIC device includes four dedicated global lines that all tiles in the array can access. These lines exhibit very low skew. When ASICmaster imports the netlist and device data, it can automatically assign unused global resources to the nets with the highest fanouts (for example, clock and reset signals).

If high fanout signals mapped by ASICmaster to global resources are buffered, ASICmaster automatically removes these buffers. ProASIC devices provide automatic buffering for global resources.

Signals can also be assigned to the global resources by using ASICmaster global primitives in netlists, and by specifying constraint files for ASICmaster. Refer to "Global Resource Constraints" on page 67 for additional information.

The checker contains a description of the highest fanout nets in a design and the results of automatic global assignments. If user constraints appear not to have been honored, refer to this report file.

# Implementing Memories

All ProASIC devices support embedded memories. Synchronous or asynchronous two port RAMs and FIFOs can be generated by MEMORYmaster and imported into the synthesis and simulation environments. ASICmaster also supports distributed memories. Although this implementation of memories is much less efficient in terms of gate utilization, it may be appropriate for smaller memories in a design.Refer to the *MEMORYmaster User's guide* for additional information.

# Using ASICmaster

This chapter explains how to select a design and start a design project work session using the ASICmaster graphical user interface. It describes how to use the Design Executive, set project preferences, place and route a design, and generate files such as the bitstream file of device-programming data. Refer to "File and Command Selection" on page 117 for additional information about using the graphical user interface.

# Invoking ASICmaster

Each ASICmaster design project processes a single design and creates programming and other files for the design. When a project is started, ASICmaster creates a database for it.

ASICmaster can be used from the graphic user interface, in TTY mode<sup>1</sup>, or in batch mode. Many designers use the graphical interface while they are learning to use ASICmaster. As they become more familiar with the system, they change to command-line or batch mode to speed up their work or to automatically repeat ASICmaster task cycles. This chapter describes ASICmaster primarily in terms of its graphic user interface. Refer to "Using ASICmaster in TTY and Batch Modes" on page 87 for information about using ASICmaster in batch and command-line mode.

## To invoke ASICmaster:

### PC

Choose ASICmaster 5.0 from the ASICmaster menu under Programs in the Start menu.

## UNIX

• Type the following command at the prompt:

asicmaster&

<sup>1.</sup> Available on UNIX only

#### Chapter 2: Using ASIC master

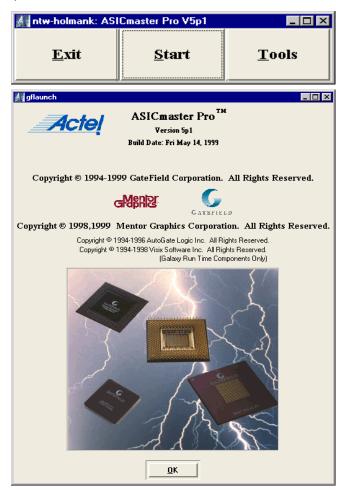

# **Main Menu** Starting ASIC master in graphical mode displays the main menu and copyright information windows as shown in Figure 2-1.

To close the copyright window, click OK at the bottom of the window or click any button in the main menu.

Figure 2-1. Main Menu and Copyright Information Window

The Following commands are available from the Main menu:

### Exit

Terminates ASICmaster program.

### Start

Starts an ASIC master work session and displays the Design Selection window to select a design project.

### Tools

Opens the tools menu, as shown in Figure 2-2 below.

| 🗙 ASICmaster Tools 💶 🛛 🗙           |  |  |  |  |  |  |  |

|------------------------------------|--|--|--|--|--|--|--|

| <u>S</u> tart Design               |  |  |  |  |  |  |  |

| Build Embedded Memories            |  |  |  |  |  |  |  |

| Build <u>D</u> istributed Memories |  |  |  |  |  |  |  |

| <u>P</u> artition                  |  |  |  |  |  |  |  |

| Help                               |  |  |  |  |  |  |  |

|                                    |  |  |  |  |  |  |  |

| <u></u>                            |  |  |  |  |  |  |  |

Figure 2-2. Tools Menu Window

**Tools Menu** The following commands are available from the Tools menu:

### Start Design

Brings up the design selection window to begin a new design or open an existing one.

## **Build Embedded Memories**

Invokes the Embedded MEMORYmaster, which creates RAMs or FIFOs that are mapped to embedded memory resources on ProASIC devices. Refer to the *MEMORYmaster User's Guide* for additional information.

Chapter 2: Using ASIC master

### **Build Distributed Memories**

Invokes the Distributed MEMORYmaster, which creates RAMs or FIFOs that are mapped to logic tiles on ProASIC devices. Refer to the *MEMORYmaster User's Guide* for additional information.

### Partition

Starts the Auspy Partitioning System.

### Close

Closes the Tools menu.

# Starting a Project Work Session

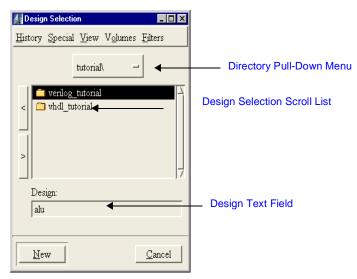

Clicking the Start button in the Main menu opens displays the Design Selection file browser to select a design, as shown in Figure 2-3.

Figure 2-3. Design Selection File Browser

# Selecting a Design

Each design project is identified by a design name. Existing designs can be selected or new designs can be created and design project databases are created in the Design Selection file browser. The design must reside in a directory that the user owns or has read, write, and execute permissions. because new files are created in the directory as ASICmaster is used.

The types of files shown in the file browser can be restricted (for example, to Verilog or EDIF or VHDL files) using the browser's Filters menu. Refer to "Restricting the Types of Files Listed" on page 118 for additional information.

### To open an existing design file:

- 1. Click the design name in the Design Selection scroll list in the browser.

- 2. Press Return or click the Open button. A message window is displayed to notify you that ASICmaster is opening the design file.

#### To create and open a new design file:

- **1.** Enter the name of the file in the Design text field. You do not need not include the .dtf extension.

- **2. Press Return or click the New button.** A message window is displayed to notify you that ASICmaster is creating the design file.

- Note: When the Design Selection file browser is displayed, the New and Apply buttons are inactive (dimmed) before entering or selecting a design. When a design name is entered in the Design text field, the buttons become active. If a selection from the directory pull-down menu is made, the New button is replaced by the Open button.

# Design Executive Window

When a design file is opened or created, the Design Executive window is displayed. The design name appears in the Window Title Bar, as shown in Figure 2-4. The Design Executive is the primary user interface tool. It includes a menu bar, text fields for entering project preferences, and two buttons that start the main ASICmaster functions.

| Design Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Martw-holmank: Design "alu" - ASICmaster Pro V5p1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ×               |

| Design Tasks View Options Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | P               |

| Input<br>Netlist Constraints<br>Top Cell Part<br>Top Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | > Input Area    |

| Run<br>GO<br>Timing Driven<br>Placement Refinement<br>Show Tasks<br>Incremental Routing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Run Area        |

| Results Bitstream Datasheet Pin Map Timing Annotation Boundary Scan Bitstream Bitstrea | Results<br>Area |

Show Task Check Box

Figure 2-4. Design Executive Window

## Design Executive Functions

The Design Executive is used to add and removed from lists, and to order files in lists. For example, if multiple netlists are being imported, they must be ordered so that files that rely on other files for definitions are listed in the order of dependency. The Design Executive is also used to set project preferences, to select the target ProASIC device, and to set place and route options. In addition it is used to select tasks for ASICmaster to perform, including enabling or disabling tasks such as delay calculation and datasheet generation.

The design's parameter settings are stored in an ASIC master database and affect all task runs. If an existing design has been opened, the text fields in the Design Executive window shows the current settings.

# Input Area

The Input area is used to specify what files are used in a design. The Input area contains two types of file management buttons, Folder buttons and Eraser buttons. The Folder buttons open file browsers, which are used to locate and specify files, such as netlists to import for the design.

The Eraser buttons in the Input area remove selected files in file lists in the Design Executive.

# Run and Area

The Run area is used to specify place and route parameters and whether the Tasks selection list appears when users start a task run. It includes the Go button, which automatically starts performing tasks or prompts users to select tasks that have not been run successfully for a design, are appropriate for the current design state and match the project preference settings and any task selections made.

### **Results Area**

The Results Area is used to enable delay calculation, file generation, including the device programming bitstream file, and specify names for results files. The Results area includes a Folder button.

Design Executive Menus

The Design Executive menus contain commands that can be selected to perform tasks. Refer to the sections below for additional information performing tasks with a specific menu. Refer to "File and Command Selection" on page 117 For information about using mnemonics and accelerator keys to select menus and enter commands.

### Design Menu

"Saving Designs" on page 33.

### Tasks Menu

"Limiting the Task Flow" on page 18.

#### View Menu

"Viewing Report Files" and "Viewing Results" on page 39.

### **Options Menu**

"Specifying Netlist Formats" on page 21 and "Setting Operating Conditions" on page 31.

# Setting Design Project Preferences and Managing Files

After starting ASICmaster, the first task is setting the layout and deviceprogramming project preferences for the ProASIC device. The setup information becomes part of ASICmaster database for the design project. The following must be specified:

- One or more netlists.

- A target ProASIC device for the design.

- Place and route options, such as "Timing Driven."

The following preferences can also be set:

- Specify the ASIC master task flow limits and specifications.

- Identify constraint files for ASICmaster to import.

- Enable post-layout delay calculation and generate back annotation files.

- Generate the device programming bitstream and other output files.

The project preferences are set by entering required data in the Design Executive window and by running commands from the Options and Tasks menus in the Design Executive window. The following sections explain how to limit the task flow, specify netlist files, and set the other parameters that the Design Executive controls.

# Selecting Tasks

ASICmaster automatically identifies the prerequisite tasks and data for any run. For example, if constraint files are changed for a design, the next time place and route is run, the system automatically selects the Check Input task. The system does this because ASICmaster must validate each constraint file before creating a layout for the netlist. Before setting parameters and processing a design, ASICmaster automatically defines the task flow as follows:

- Import the netlist.

- Check the input data.

- Place and route the design.

When setting parameters and processing the design, ASICmaster adjusts the task flow and its requirements. At any given time, ASICmaster derives the flow and requirements based on:

- Parameter settings recently set in the Design Executive Window.

- Design flow rules. See Chapter 1, "ASICmaster Overview" on page 1.

- The current design state, defined by stored parameter settings.

- Netlist filenames and path name and the status of each netlist including whether ASIC master has imported the file and whether the original file has been altered since the import operation.

The system's task flow and prerequisites can be changed at any time without interfering with ASICmaster's prerequisites for task runs and some of ASICmaster's current task prerequisites can be overridden to force the system to perform or omit specific tasks. ASICmaster monitors the state of the design and stores design-related parameter values and a lastmodification time-stamp data in a file.

Refer to "The Design (\*.dtf) Directory" on page 137 "Redefining Task Prerequisites and Flow" on page 36," and "Redefining Task Prerequisites and Flow" on page 36 for additional information.

## Limiting the Task Flow

The task flow can be limited by defining the last task in the sequence of tasks that ASICmaster performs. For example, a design's layout can be optimized without generating the device programming bitstream or other external output files. If ASICmaster does not generate these files, runs proceed faster. There are two ways to limit the task flow:

- Use the Tasks Menu.

- Use the Tasks selection list in the Tasks window.

In some cases, the task flow can not be limited. For example, If a netlist for the design has been altered, the Tasks menu cannot be used to omit Check Input. Or if Import Netlist is selected, place and route cannot be omitted. See "Redefining Task Prerequisites and Flow" on page 36 for additional information about limiting the task flow.

## Using the Tasks Menu

The Tasks menu, as shown in Figure 2-5 on page 19, limits ASICmaster to performing a selected task and all related tasks that are required for successful task performance for the current design state. It also Immediately executes those tasks or displays the file selection list.

## To use the Tasks menu:

1. Click the Tasks menu in the Design Executive Window. The Tasks menu is displayed.

| 🗙 Tasks                       | _ 🗆 🗵        |

|-------------------------------|--------------|

| Place & Route                 | Ctrl+P       |

| <u>R</u> un Script            | Ctrl+R       |

| Import Netlist                | Ctrl+I       |

| <u>S</u> elect Part           | Ctrl+E       |

| Check Input                   | Ctrl+C       |

| Calculate <u>T</u> iming      | Ctrl+T       |

| <u>G</u> enerate Bitstream    | Ctrl+B       |

| Generate <u>B</u> oundaryscan | Ctrl+Shift+B |

| Generate <u>D</u> atasheet    | Ctrl+D       |

| Generate Pin <u>M</u> ap      | Ctrl+M       |

| <u>E</u> dit Pin Map          | Ctrl+Shift+E |

| Estimate Po <u>w</u> er       | Ctrl+Shift+P |

Figure 2-5. The Tasks Menu

2. Choose a task by double-clicking its name. ASICmaster limits the task flow and immediately performs tasks.

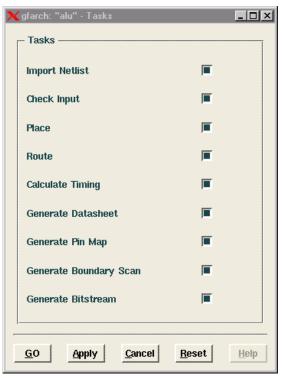

## Using the Tasks Selection List

The Task Selection list, shown in Figure 2-6 on page 20 displays the tasks ASICmaster has selected for the current run. The Task Selection list can be used to override some of ASICmaster's task prerequisites to force the system to perform or omit specific tasks.

## To use the Tasks Selection list during a ASIC master run:

1. Check the Show Tasks box in the Design Executive window. The Tasks Selection list is only displayed during each time a task run is started if this box is checked. For information on using the list, see "Redefining Task Prerequisites and Flow" on page 36.

| X | gfarch: "alu" - Tasks                              | _ 🗆 🗙 |

|---|----------------------------------------------------|-------|

| Г | - Tasks                                            |       |

|   | Import Netlist                                     |       |

|   | Check Input                                        |       |

|   | Place 🔳                                            |       |

|   | Route                                              |       |

|   | Calculate Timing                                   |       |

|   | Generate Datasheet                                 |       |

|   | Generate Pin Map                                   |       |

|   | Generate Boundary Scan                             |       |

|   | Generate Bitstream                                 |       |

|   |                                                    |       |

|   | <u>GO</u> <u>Apply</u> <u>Cancel</u> <u>R</u> eset | Help  |

Figure 2-6. The Tasks Selection List

- 2. Check the box next to the task(s) to perform. Uncheck any tasks that you do not want performed.

- **3.** Click the GO or Apply button at the bottom of the Tasks window. Selecting a task on the list does not immediately execute it or its associated tasks.

# Specifying Netlist Formats

The netlist file type can be set in ASICmaster. ASICmaster supports EDIF 2.0.0, Verilog, and VHDL netlist formats. Before ASICmaster imports the netlists specified, it verifies that the netlist files being imported are in a supported format. Refer to "Supported Netlist Formats and Constructs" on page 129 for additional information

## To set the netlist file format for a design:

1. In the Design Executive window, choose the Design command from the Options menu. The Design Options window is displayed, as shown in Figure 2-7.

| 🗙 gfarch: "alu" - Design Options      | - D×                                                                                     |  |

|---------------------------------------|------------------------------------------------------------------------------------------|--|

| Netlist Format:                       | Verilog 🛁                                                                                |  |

| Timing Report:                        | 🔷 Fastest 🛛 Typical 🔶 Slowest                                                            |  |

| - SDF Parameters for Commercial Grade |                                                                                          |  |

| Operating Conditions:                 | Best Typical Worst                                                                       |  |

| Junction Temperature (C):             | Min         Тур         Мах           0         7 \[]_25         7 \[]_70         7 \[]_ |  |

| Juncuon Temperature (C).              | <u>иах Тур Min</u>                                                                       |  |

| Core Voltage (V):                     | 2.75 7 1 2.50 7 1 2.25 7 1                                                               |  |

| Process:                              | Best - Typical - Worst -                                                                 |  |

| Default Pad Load (pF): 50 7 ]         |                                                                                          |  |

| <u>O</u> K <u>C</u> ancel             | Default Help                                                                             |  |

Figure 2-7. Design Options Window

- 2. Click the Netlist Format pull down menu and choose the appropriate netlist format.

- 3. Click OK.

# Selecting Netlists

To begin a design, one or more netlist files must be selected. Once selected, the netlist(s) are displayed in the Input area of the Design Executive window, as shown in Figure 2-8.

Note: All netlists for a design must be in the same format.

| Netlist File Scroll List                                                          | Constraints File Scroll List |

|-----------------------------------------------------------------------------------|------------------------------|

| Netlist Folder Button                                                             | Constraints Folder Button    |

| 🚮 ntw-holmank: Design "alu" - ASICmaster Pro V                                    |                              |

| Design Tasks View Options                                                         | Help                         |

| Input<br>Netlist<br>E:\programs\asicmaster5p1\t<br>Top Cell<br>alu<br>Top Library | Constraints                  |

| Netlist Fraser Button                                                             | Constraints Eraser Button    |

Figure 2-8. Design Executive Window Input Area

#### To add netlists:

1. Click the Netlist Folder button in the Design Executive window. The Netlist File Selection browser is displayed, as shown in Figure 2-9. If the file format has been set, the filenames that appear are limited to those in the format specified.

| - "alu" - Netlist File Select 🖡 🗌            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| History Special View Filters                 | Personal Per |

| tutorial_dir/                                | File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 🚱 alu 🖌                                      | Selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>alu.v</li> <li>alu_str.v</li> </ul> | List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| test.v                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

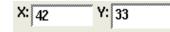

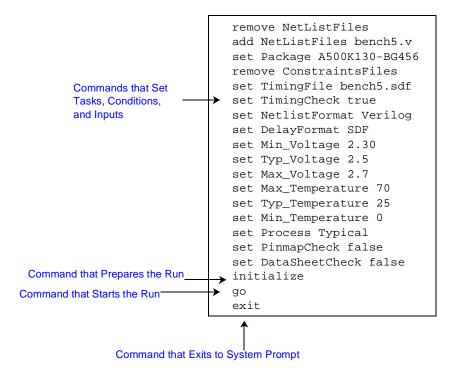

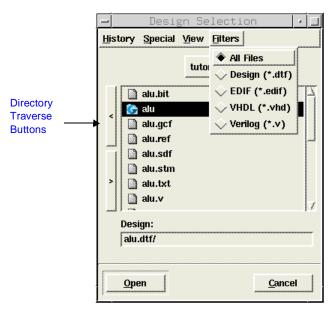

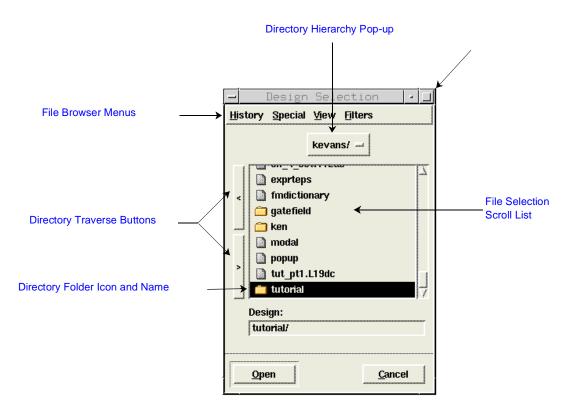

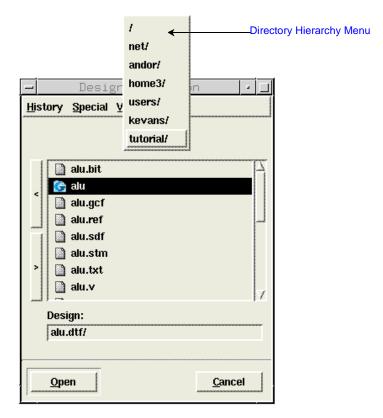

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |