# Introduction to WebPACK 4.1 for CPLDs

Using Xilinx WebPACK Software to Create CPLD Designs for the XS95 Board

Release date: 10/29/2001

All XS-prefix product designations are trademarks of XESS Corp.

All XC-prefix product designations are trademarks of Xilinx.

#### **Table of Contents**

| Wł  | hat This Is and <i>Is Not</i>                                                                                                                                                                                                                 | 1                                                  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| CP  | PLD Programming                                                                                                                                                                                                                               | 3                                                  |

| Ins | stalling WebPACK                                                                                                                                                                                                                              | 5                                                  |

|     | Getting WebPACK                                                                                                                                                                                                                               | 5                                                  |

|     | Installing WebPACK                                                                                                                                                                                                                            | 8                                                  |

|     | Getting XSTOOLs                                                                                                                                                                                                                               | 8                                                  |

|     | Installing XSTOOLs                                                                                                                                                                                                                            | 9                                                  |

| Ou  | ır First Design                                                                                                                                                                                                                               | 10                                                 |

|     | An LED Decoder                                                                                                                                                                                                                                | 10                                                 |

|     | Starting WebPACK Project Navigator                                                                                                                                                                                                            | 12                                                 |

|     | Describing Your Design With VHDL                                                                                                                                                                                                              | 18                                                 |

|     | Checking the VHDL Syntax                                                                                                                                                                                                                      | 25                                                 |

|     |                                                                                                                                                                                                                                               |                                                    |

|     | Fixing VHDL Errors                                                                                                                                                                                                                            | 26                                                 |

|     | Fixing VHDL Errors         Synthesizing the Logic circuitry for Your Design                                                                                                                                                                   |                                                    |

|     |                                                                                                                                                                                                                                               | 29                                                 |

|     | Synthesizing the Logic circuitry for Your Design                                                                                                                                                                                              | 29<br>30                                           |

|     | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD                                                                                                                                                 | 29<br>30<br>32                                     |

|     | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit                                                                                                                             | 29<br>30<br>32<br>34                               |

|     | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit<br>Constraining the Fit                                                                                                     | 29<br>30<br>32<br>34<br>39                         |

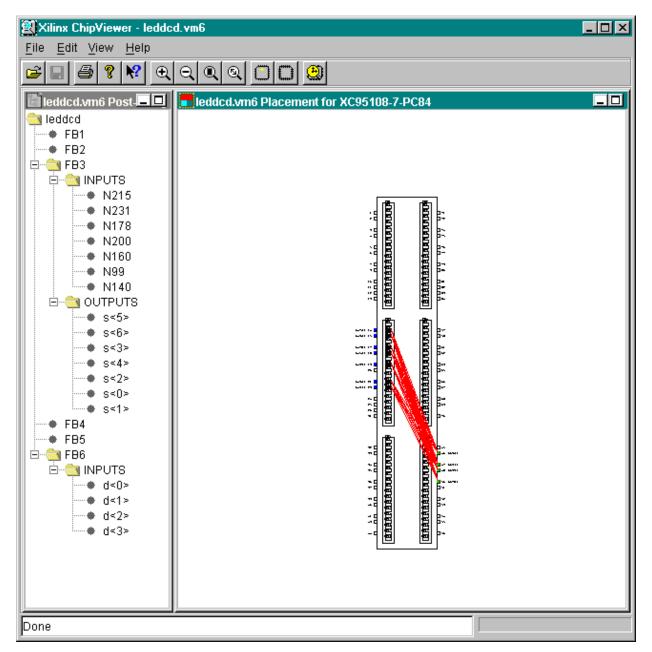

|     | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit<br>Constraining the Fit<br>Viewing the Chip                                                                                 | 29<br>30<br>32<br>34<br>39<br>45                   |

|     | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit<br>Constraining the Fit<br>Viewing the Chip<br>Generating the Bitstream                                                     | 29<br>30<br>32<br>34<br>39<br>45<br>52             |

| Hie | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit<br>Constraining the Fit<br>Viewing the Chip<br>Generating the Bitstream<br>Downloading the Bitstream                        | 29<br>30<br>32<br>34<br>39<br>45<br>52<br>55       |

| Hie | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit<br>Constraining the Fit<br>Viewing the Chip<br>Generating the Bitstream<br>Downloading the Bitstream<br>Testing the Circuit | 29<br>30<br>32<br>34<br>39<br>45<br>52<br>55<br>56 |

| Hie | Synthesizing the Logic circuitry for Your Design<br>Fitting the Logic Circuitry Into the CPLD<br>Checking the Fit<br>Constraining the Fit<br>Viewing the Chip<br>Generating the Bitstream<br>Downloading the Bitstream<br>Testing the Circuit | 29<br>30<br>32<br>34<br>39<br>45<br>55<br>55<br>56 |

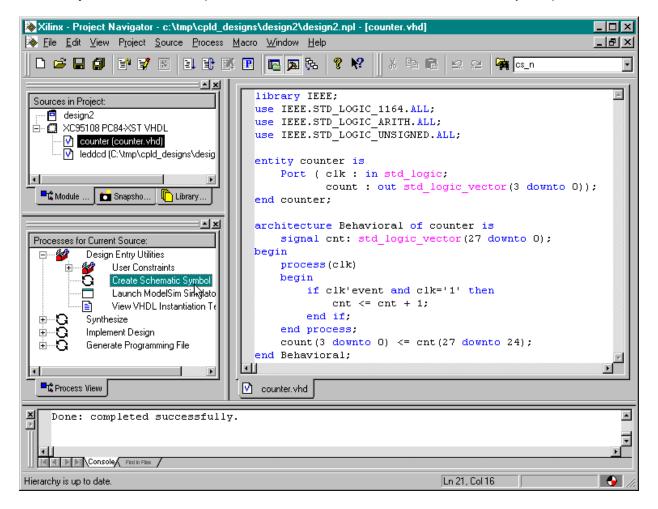

| Adding a Counter                                | 61  |

|-------------------------------------------------|-----|

| Tying Them Together                             | 66  |

| Checking the VHDL Syntax                        | 97  |

| Constraining the Design                         | 98  |

| Synthesizing the Logic Circuitry for the Design | 99  |

| Fitting the Logic Circuitry Into the CPLD       | 100 |

| Checking the Fit                                | 102 |

| Checking the Timing                             | 104 |

| Generating the Bitstream                        | 106 |

| Downloading the Bitstream                       | 112 |

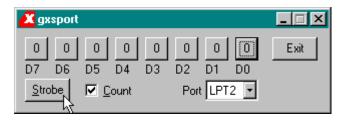

| Testing the Circuit                             | 113 |

| Going Further                                   | 114 |

### What This Is and *Is Not*

There are numerous requests on newgroups that go something like this:

"I am new to using programmable logic like FPGAs and CPLDs. How do I start? Is there a tutorial and some free tools I can use to learn more?"

Xilinx has released their WebPACK on the web so that anyone can download a free set of tools for CPLD and FPGA-based logic designs. And XESS Corp. has written this tutorial that attempts to give you a gentle introduction to using the WebPACK tools. (Other programmable logic manufacturers have also released free toolsets. Someone else will have to write a tutorial for them.)

This tutorial shows the use of the WebPACK tools on two simple design examples: 1) an LED decoder and 2) a counter which displays its current value on a seven-segment LED. Along the way, you will see:

- How to start a CPLD project.

- How to target a design to a particular type of CPLD.

- How to describe a logic circuit using VHDL and/or schematics.

- How to detect and fix VHDL syntactical errors.

- How to synthesize a netlist from a circuit description.

- How to fit the netlist into a CPLD.

- How to check device utilization and timing for a CPLD.

- How to generate a bitstream for a CPLD.

- How to download a bitstream to program a CPLD.

- How to test the programmed CPLD.

That said, it is important to say what this tutorial will not teach you:

- It will not teach you how to design logic with VHDL.

- It will not teach you how to choose the best type of FPGA or CPLD for your design.

- It will not teach you how to arrange your logic for the most efficient use of the resources in a CPLD.

- It will not teach you what to do if your design doesn't fit in a particular CPLD.

- It will not show you every feature of the WebPACK software and discuss how to set every option and property.

In short, this is just a tutorial to get you started using the Xilinx WebPACK CPLD tools. After you go through this tutorial you should be able to move on to more advanced topics.

## 1

### **CPLD Programming**

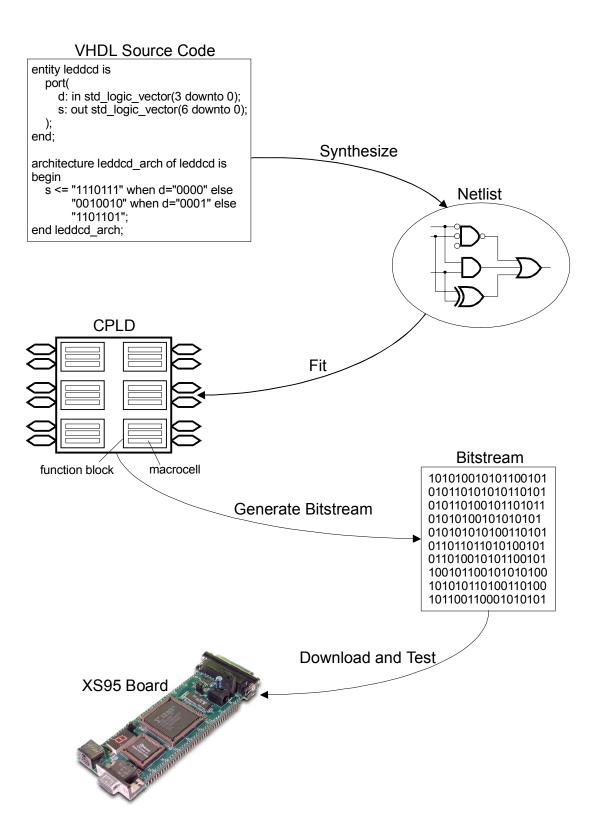

Implementing a logic design with a CPLD usually consists of the following steps (depicted in the figure which follows):

- 1. You enter a description of your logic circuit using a *hardware description language* (HDL) such as VHDL or Verilog. You can also draw your design using a schematic editor.

- 2. You use a *logic synthesizer* program to transform the HDL or schematic into a *netlist*. The netlist is just a description of the various logic gates in your design and how they are interconnected.

- 3. You use a *fitter* program to map the logic gates and interconnections into the CPLD. The CPLD consists of several *function blocks* which can be further decomposed into *macrocells* that can perform logic operations. The function blocks and macrocells are interwoven with various *routing matrices*. The fitter assigns gates from your netlist to various macrocells in the function blocks and opens or closes switches in the routing matrices to connect the gates together.

- 4. Once the fitting is complete, a program extracts the state of the switches in the routing matrices and generates a *bitstream* where the ones and zeroes correspond to open or closed switches. (This is a bit of a simplification, but it will serve for the purposes of this tutorial.)

- 5. The bitstream is *downloaded* into a physical CPLD chip (usually embedded in some larger system). The electronic switches in the CPLD open or close in response to the binary bits in the bitstream. Upon completion of the downloading, the CPLD will perform the operations specified by your HDL code or schematic.

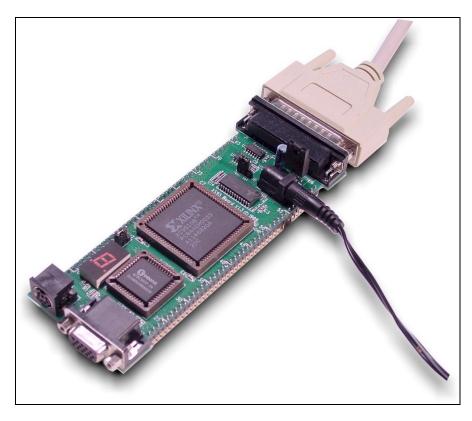

That's really all there is to it. Xilinx WebPACK provides the HDL and schematic editors, logic synthesizer, fitter, and bitstream generator software. The XSTOOLs from XESS provide utilities for downloading the bitstream into an <u>XS95 Board</u> containing a Xilinx XC95108 CPLD.

## 2

## **Installing WebPACK**

#### **Getting WebPACK**

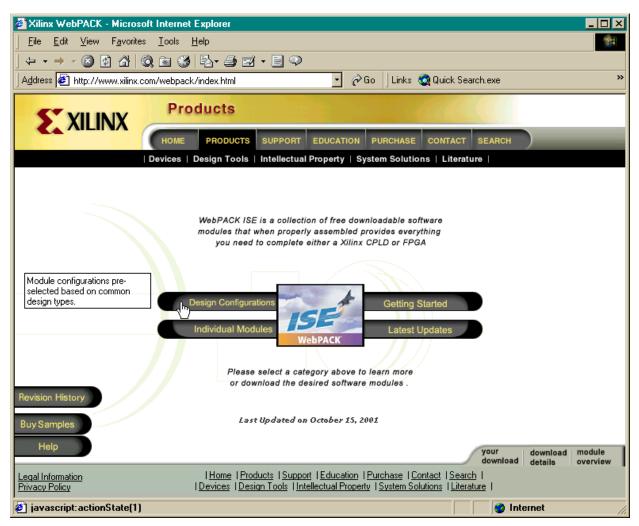

Before downloading the WebPACK software you will have to register at <u>http://www.Xilinx.com/xlnx/xil\_entry2.jsp?sMode=login&group=webpack</u>. You will choose a user ID and password and then you will be allowed to enter the site. Then you can go to <u>http://www.Xilinx.com/webpack/index.html</u> to begin downloading the WebPACK software. After entering the WebPACK homepage, click on the Design Configurations button as shown on the next page.

Next, click on the Select All button. This will select all the WebPACK software modules that cover both FPGA and CPLD designs.

| 🚰 Xilinx WebPACK - Microso                        | oft Internet Explorer                  |               |                      |              |                 |                                                            |                                                |

|---------------------------------------------------|----------------------------------------|---------------|----------------------|--------------|-----------------|------------------------------------------------------------|------------------------------------------------|

| <u>File E</u> dit <u>V</u> iew F <u>a</u> vorites | : <u>T</u> ools <u>H</u> elp           |               |                      |              |                 |                                                            | 191<br>191                                     |

| ← → → ⊗ 🐼 🖓 (0                                    | Q 🖻 🧭 🖏 - 🍠 🖻                          | - 📃 🗼         |                      |              |                 |                                                            |                                                |

| Address 🛃 http://www.xilinx.c                     |                                        |               | • @                  | Go Links (   | 🗿 Quick Sea     | arch.exe                                                   | »>                                             |

| <b>E</b> XILINX                                   | Products                               |               |                      |              |                 |                                                            |                                                |

|                                                   | HOME PRODUCTS                          | SUPPORT       | EDUCATION            | PURCHASE     | CONTACT         | SEARCH                                                     |                                                |

|                                                   | Devices   Design Tools                 | Intellectual  | Property   Sy        | stem Solutio | ns   Literat    | ure                                                        |                                                |

| Design Connigurations                             | PLD Design<br>PGA Design<br>PGA Design | ducts   Suppo | t   <u>Education</u> |              | Intact   Searce | Design Type<br>CPLD Des<br>FPGADes<br>Select A<br>Select A | ry Choice<br>ed Modules<br>a:<br>sign:<br>sign |

Then click on the Download button to begin downloading the WebPACK software.

| Xilinx WebPACK - Micros       | oft Internet Explorer                                         |                                                              |                             |                |                                                 |                                                                 |

|-------------------------------|---------------------------------------------------------------|--------------------------------------------------------------|-----------------------------|----------------|-------------------------------------------------|-----------------------------------------------------------------|

|                               | s <u>T</u> ools <u>H</u> elp                                  |                                                              |                             |                |                                                 |                                                                 |

|                               | Q 🖻 🧭 🔁 🗗                                                     |                                                              |                             | A Database     |                                                 |                                                                 |

| Address 🖉 http://www.xilinx.c | com/webpack/index.html                                        | c                                                            | ≻Go ∐Links ⊧                | 🧕 Quick Sea    | arch.exe                                        |                                                                 |

| <b>XILINX</b>                 | Products                                                      |                                                              |                             |                |                                                 |                                                                 |

|                               | HOME PRODUCTS                                                 | SUPPORT EDUCATION                                            | PURCHASE                    | CONTACT        | SEARCH                                          |                                                                 |

|                               | Devices   Design Tools                                        | Intellectual Property                                        | System Solutio              | ns   Literat   | ure                                             |                                                                 |

| Design Conligurations         | PLD Design<br>PGA Design<br>I Home   Proc<br>I Devices   Desi | ducts   Support   Education<br>gn Tools   Intellectual Prope | <u>Purchase</u>   <u>Cc</u> | ontact   Searc | Design Type<br>CPLD Des<br>FPGA Des<br>Deselect | ry Choice<br>ed Modules<br>a:<br>sign:<br>sign<br>TAIL Download |

Click on the link to download the WebPACK software in the Download WebPACK window. You can use either the FTP or the HTTP link. (You can also download the demo version of the ModelSim HDL simulator but we will not discuss the operation of that software in this tutorial.)

| 🖉 Download Web                            | PACK - Microsoft Inter                                                             | net Explorer                              | <u> </u>               |

|-------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------|------------------------|

| <b>E</b> XILINX                           | Download Manag                                                                     | er                                        | *                      |

| WebPACK installat<br>save each file to yo | ule selections, you will<br>ion files. Please select e<br>ur hard disk. Then run e | ither the FTP or H<br>ach installer execu | TTP link and<br>table. |

|                                           | s <u>Download Accelerato</u><br>ple to resume interrupte                           |                                           | timize your            |

| WebPACK 4.1WP1.0                          | ) - October 15, 2001                                                               |                                           |                        |

| WebPACK_41wp10<br>MXE_41wp10_full_        |                                                                                    | 110.25M <u>F</u><br>38.58M <u>F</u>       |                        |

| Total download size                       | e:                                                                                 | 148.83M                                   |                        |

| Estimated Total Dov                       | wnload Time:                                                                       | T1:<br>56k:                               | 14 Min<br>354 Min      |

| Disk Space Require<br>Maximum Disk Spac   | d:<br>ce Required During Inst                                                      | 430.87M                                   | 304 IVIIII             |

|                                           |                                                                                    |                                           |                        |

|                                           |                                                                                    |                                           |                        |

|                                           |                                                                                    |                                           |                        |

|                                           |                                                                                    |                                           |                        |

|                                           |                                                                                    |                                           |                        |

|                                           |                                                                                    |                                           | <b>T</b>               |

#### Installing WebPACK

After the WebPACK software download completes, double-click the .EXE file. The installation script will run and install the software. Accept the default settings for everything and you shouldn't have any problems.

#### Getting XSTOOLs

If you are going to download your CPLD bitstreams into an XS95 Board, then you will need to get the XSTOOLS software from <u>http://www.xess.com/ho07000.html</u>. Just download the <u>xstools4.exe</u> file.

#### Installing XSTOOLs

Double-click the xstools4.exe file. The installation script will run and install the software. Accept the default settings for everything.

## **Our First Design**

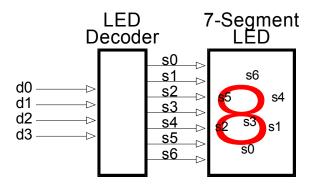

#### An LED Decoder

The first CPLD design we will try is an LED decoder. An LED decoder takes a four-bit input and outputs seven signals which drive the segments of an LED digit. The LED segments will be driven to display the digit corresponding to the hexadecimal value of the four input bits as follows:

| Four-bit Input | Hex Digit | LED Display |

|----------------|-----------|-------------|

| 0000           | 0         | 0           |

| 0001           | 1         | ľ           |

| 0010           | 2         | 5           |

| 0011           | 3         | 3           |

| 0100           | 4         | ч           |

| 0101           | 5         | 5           |

| 0110           | 6         | 6           |

| 0111           | 7         | ٦           |

| 1000           | 8         | 8           |

| 1001           | 9         | 9           |

| 1010           | A         | 8           |

| 1011           | В         | 8           |

| 1100           | С         | C           |

| 1101           | D         | D           |

| 1110           | E         | E           |

| 1111           | F         | F           |

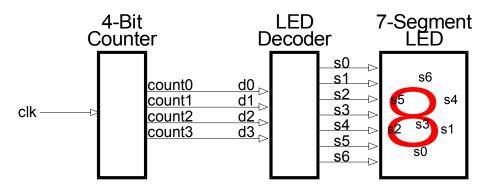

A high-level diagram of the LED decoder looks like this:

#### Starting WebPACK Project Navigator

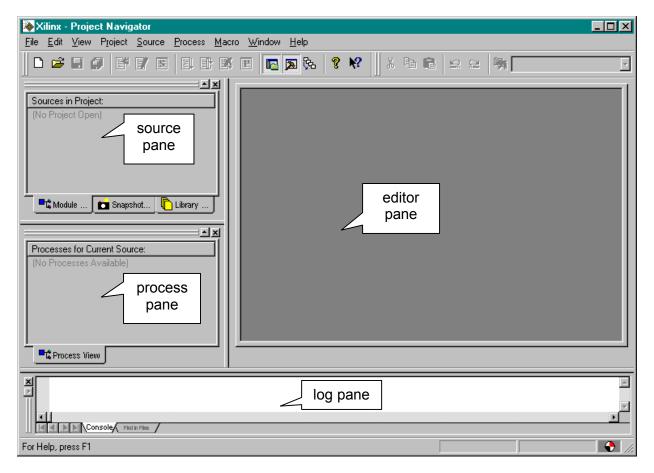

We start WebPACK by double-clicking the **Project** icon, ,on the desktop. This will bring up an empty project window as shown below. The window has four panes:

- 1. A **source pane** that shows the organization of the source files that make up our design. There are four tabs so we can view the source files, functional modules, or HDL libraries for our project or look at various snapshots of the project.

- 2. A **process pane** that lists the various operations we can perform on a given object in the source pane.

- 3. A log pane that displays the various messages from the currently running process.

- 4. An **editor pane** where we can enter HDL code. Schematics are entered in a separate window.

To start our design, we must create a new project by selecting the File → New Project item from the menu bar.

| 💫 Xilinx - Project Navigator                                       |                                                                | ×  |

|--------------------------------------------------------------------|----------------------------------------------------------------|----|

| <u>File</u> <u>E</u> dit <u>V</u> iew P <u>r</u> oject <u>S</u> ou | urce <u>P</u> rocess <u>M</u> acro <u>W</u> indow <u>H</u> elp |    |

| New Project<br>Open P <u>r</u> oject<br>Open Exa <u>m</u> ple      |                                                                |    |

| Close Projec <u>t</u><br>Sa <u>v</u> e Project As                  |                                                                |    |

| <u>N</u> ew Ctrl+N<br>Open Ctrl+O<br>Close                         |                                                                |    |

| <u>S</u> ave Ctrl+S<br>Save <u>A</u> s<br>Print Ctrl+P             |                                                                |    |

| Save Alj                                                           |                                                                | 11 |

| Recent Projects                                                    |                                                                |    |

| E <u>x</u> it                                                      |                                                                | 11 |

|                                                                    |                                                                | Ш  |

| Process View                                                       |                                                                | 9  |

|                                                                    |                                                                |    |

|                                                                    |                                                                |    |

| Create a new project                                               |                                                                |    |

This brings up the **New Project** window where we can enter the location of our project files, project name, the target device for this design, and the tools used to synthesize logic from our source files.

| New Project                                           |                                           |              |                  | × |

|-------------------------------------------------------|-------------------------------------------|--------------|------------------|---|

| Project <u>N</u> ame:<br> <br>Project Device Options: | Project <u>L</u> ocation<br>C:Wilinx_WebF |              | - <del>1</del> 2 |   |

| Property Name                                         |                                           | Value        |                  | Т |

| Device Family                                         |                                           | XC9500 CPLDs |                  |   |

| Device                                                |                                           | XC95108 PC84 |                  |   |

| Design Flow                                           |                                           | EDIF         |                  |   |

| OK.                                                   | Cancel                                    |              |                  |   |

Click on the ... button next to the Project Location field and use the **Browse for Folder** window to select a folder where our project files will be stored. For our design examples, we will store everything in the C:\tmp\cpld\_designs folder.

| Browse for Folder  | ? ×      |

|--------------------|----------|

| Select Directory   |          |

|                    |          |

|                    | -        |

| RECYCLED           |          |

| SC 👘               |          |

| 🗄 💼 sdram          |          |

| 🗈 💼 🛄 SNAPSHOT     |          |

| i i temp           |          |

|                    |          |

|                    |          |

| 🗄 🔂 fpga_designs 🧏 |          |

|                    |          |

|                    |          |

|                    | <b>_</b> |

|                    |          |

|                    |          |

| OKC                | ancel    |

|                    |          |

Next we will give our LED decoder design the descriptive title of design1 by typing it into the Project name field.

| ew Project            |               |                  |                       |  |

|-----------------------|---------------|------------------|-----------------------|--|

| Project <u>N</u> ame: |               | Project Location | n:                    |  |

| design1               |               | C:\tmp\cpld_d    | esigns\design1        |  |

| Project Device Option | ns:           |                  |                       |  |

|                       | Property Name |                  | Value                 |  |

|                       |               |                  | Value<br>XC9500 CPLDs |  |

|                       |               |                  |                       |  |

To set the family of CPLD devices we will target with this design, click in the Value field of the Device Family property. Select the XC9500 CPLDs entry in the pop-up menu that appears.

| New Project                                               |               |                  | ×                     |

|-----------------------------------------------------------|---------------|------------------|-----------------------|

| Project <u>N</u> ame:<br>design1<br>Project Device Option | ns:           | Project Location |                       |

| F                                                         | Property Name |                  | Value                 |

| Device Family                                             |               |                  | XC9500 CPLDs          |

| Device                                                    |               |                  | Virtex2               |

| Design Flow                                               |               |                  | VirtexE               |

|                                                           |               |                  | CoolRunner2 CPLDs     |

|                                                           | OK            | Cancel           | XC9500 CPLDs          |

|                                                           | N             |                  | XC9500XL CPLDs が      |

|                                                           |               |                  | XC9500XV CPLDs        |

|                                                           |               |                  | CoolRunner XPLA3 CPLD |

Then click in the Value field of the Device property to select a particular device within the device family. For our designs, we will select the XC95108 PC84 since this is the device used in the XS95 Board where we will test our design.

| New Project                                                 |                                           |                                                                                  | ×          |

|-------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------|------------|

| Project <u>N</u> ame:<br>design1<br>Project Device Options: | Project <u>Locatior</u><br>C:\tmp\cpld_de |                                                                                  |            |

| Property Name                                               |                                           | Value                                                                            |            |

| Device Family                                               |                                           | XC9500 CPLDs                                                                     |            |

| Device                                                      |                                           | XC95108 PC84                                                                     | •          |

| Design Flow OK                                              | Cancel                                    | XC95108 PC84<br>XC95144 PQ160<br>XC95144 PQ100<br>XC95144 TQ100<br>XC95216 HQ208 | <b>↓</b> 3 |

|                                                             |                                           | XC95216 PQ160<br>XC95216 BG352                                                   | -          |

Finally, our design will be done using VHDL so click in the Value field of the Design Flow property and select XST VHDL from the pop-up menu. This enables the Xilinx VHDL synthesizer.

| New Project                                                 |                                            |                                   | ×  |

|-------------------------------------------------------------|--------------------------------------------|-----------------------------------|----|

| Project <u>N</u> ame:<br>design1<br>Project Device Options: | Project <u>L</u> ocatior<br>C:\tmp\cpld_de |                                   |    |

| Property Name                                               |                                            | Value                             |    |

| Device Family                                               |                                            | XC9500 CPLDs                      |    |

| Device                                                      |                                            | XC95108 PC84                      |    |

| Design Flow                                                 |                                            | XST VHDL                          | -  |

|                                                             |                                            | EDIF                              |    |

| ΟΚ                                                          | Cancel                                     | XST VHDL                          |    |

|                                                             |                                            | XST Verilog                       | 15 |

|                                                             |                                            | ABEL XST Verilog<br>ABEL XST VHDL |    |

Once all the fields are set, click on OK in the **New Project** window. Now the Sources pane in the **Project Navigator** window contains two items:

- 1. A project object called design1.

- 2. A chip object called XC95108 PC84 XST VHDL.

| Elle Edit View Project Source Process Macro Window Help     Sources in Project:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Xilinx - Project Navigator - C:\tmp\cpld_de                                                | signs\design1\design1.npl      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------|

| Sources in Project:<br>Casigni<br>XC95108 PC84XST VHDL<br>Casigni<br>XC95108 PC84XST VHDL<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Casigni<br>Ca | <u>File E</u> dit <u>V</u> iew P <u>r</u> oject <u>S</u> ource <u>P</u> rocess <u>M</u> ac | ro <u>W</u> indow <u>H</u> elp |

| Sources in Project  Cesign1  CXC35108 PC84XST VHDL  CXC35108 PC84XST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Ш                                                                                          |                                |

| Processes for Current Source:<br>(No Processes Available)<br>Process View<br>(Empty Log)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Sources in Project:<br>design1<br>XC95108 PC84-XST VHDL                                    |                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Processes for Current Source:<br>(No Processes Available)                                  |                                |

| For Help, press F1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                            |                                |

#### Describing Your Design With VHDL

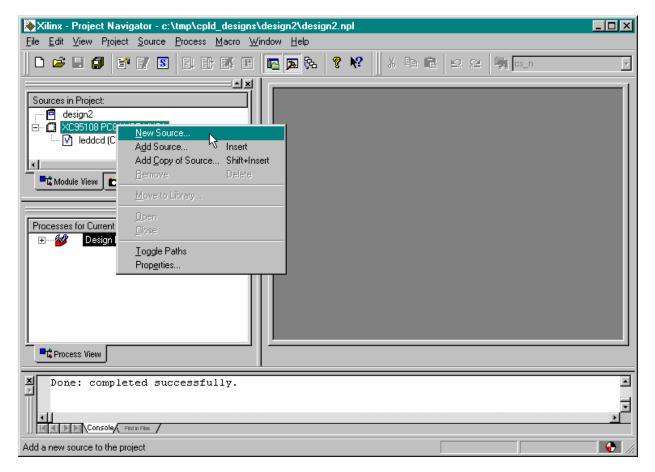

Once all the project set-up is complete, we can begin to actually design our LED decoder circuit. We start by adding a VHDL file to the *design1* project. Right-click on the XC95108 PC84 object in the Sources pane and select New Source ... from the pop-up menu as shown below.

| 💊 Xilinx - Project N                                 | avigator - C:\tmp\cpl                                     | l_designs\de                     | sign1\desig    | n1.npl     |     |              |          | _ D ×  |

|------------------------------------------------------|-----------------------------------------------------------|----------------------------------|----------------|------------|-----|--------------|----------|--------|

| <u>F</u> ile <u>E</u> dit <u>V</u> iew P <u>r</u> oj | ject <u>S</u> ource <u>P</u> rocess                       | <u>Macro W</u> indo              | w <u>H</u> elp |            |     |              |          |        |

| 🛛 🗅 🖨 🗶                                              | e e s   e s                                               | 1                                | <b>3</b> 🔊     | १ <b>№</b> | × P | <b>B</b> 2 2 | <b>1</b> |        |

| Sources in Project:                                  |                                                           |                                  |                |            |     |              |          |        |

|                                                      | New Source<br>Add Source<br>Add Copy of Source<br>Elemove | Insert<br>Shift+Insert<br>Delete |                |            |     |              |          |        |

| <br>■\$ Module [                                     | Move to Library                                           |                                  |                |            |     |              |          |        |

|                                                      | <u>O</u> pen<br><u>C</u> lose                             |                                  |                |            |     |              |          |        |

| Processes for Curre                                  | <u>T</u> oggle Paths<br>Prop <u>e</u> rties               |                                  |                |            |     |              |          |        |

| Process View                                         |                                                           |                                  | -              |            | _   |              |          |        |

| (Empty Log                                           |                                                           |                                  |                |            |     |              |          | ×<br>× |

| Add a new source to the                              | e project                                                 |                                  |                |            |     |              |          |        |

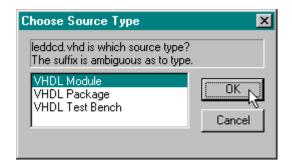

This causes a window to appear where we must select the type of source file we want to add. Since we are describing the LED decoder with VHDL, just highlight the VHDL Module item. Then we type the name of the module, leddcd, into the File Name field and click on Next.

| New                                                                                                                                  | ×                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| User Document<br>VHDL Module<br>Schematic<br>Vhdl Library<br>VHDL Package<br>VHDL Test Bench<br>Test Bench Waveform<br>State Diagram | File Name:<br>Ieddcd<br>Logation:<br>c:\tmp\cpld_designs\design1 |

| < <u>B</u> ack N                                                                                                                     | ext > Cancel Help                                                |

Then the **Define VHDL Source** window appears where we declare the inputs and outputs to the LED decoder circuit. In the first row, click in the Port Name field and type in d (the name of the inputs to the LED decoder). The **d** input bus has a width of four, so click in the MSB field and increment the upper range of the input field to 3 while leaving 0 in the LSB field.

| Define VHDL Source     |                                                                   |        |      | ×    |

|------------------------|-------------------------------------------------------------------|--------|------|------|

|                        |                                                                   |        |      | _    |

| Entity Name leddo      | :d                                                                |        |      |      |

| Architecture Name Beha | vioral                                                            |        |      | _    |

| P. ( Horas             | <b>B</b> <sup>1</sup> <b>B</b> <sup>1</sup> <b>B</b> <sup>1</sup> |        | 1.00 |      |

| Port Name              | Direction                                                         | MSB    | LSB  |      |

| d                      | in                                                                | 3      | 0    |      |

|                        | in                                                                |        |      |      |

|                        | 1                                                                 | + +    |      |      |

|                        |                                                                   |        |      |      |

| < <u>B</u>             | ack <u>N</u> ext>                                                 | Cancel | H    | Help |

Perform the same operations to create the seven-bit wide **s** bus that drives the LEDs.

| Define VHDL Source | ce             |                |     |      | 2    |

|--------------------|----------------|----------------|-----|------|------|

|                    |                |                |     |      |      |

| Entity Name        | leddcd         |                |     |      |      |

| Architecture Name  | Behavioral     |                |     |      |      |

| Port Name          |                | Direction      | MSB | LSB  | -    |

| d                  | in             |                | 3   | 0    |      |

| S                  | in             |                | 6   | 0    |      |

|                    | in             |                |     |      |      |

|                    |                |                |     |      |      |

|                    | < <u>B</u> ack | <u>N</u> ext > | Car | ncel | Help |

We must also click in the Direction field for the  $\mathbf{s}$  bus and select out from the pop-up menu in order to make the  $\mathbf{s}$  bus signals into outputs.

| efine VHDL Source    |                    |      |     | >    |  |  |  |  |

|----------------------|--------------------|------|-----|------|--|--|--|--|

| Entity Name leddod   |                    |      |     |      |  |  |  |  |

|                      |                    |      |     | _    |  |  |  |  |

| Architecture Name Be | enavioral          |      |     |      |  |  |  |  |

| Port Name            | Direction          | MSB  | LSB | 1    |  |  |  |  |

| d                    | in                 | 3    | 0   |      |  |  |  |  |

| s                    | out                | 6    | 0   |      |  |  |  |  |

|                      | in                 |      |     |      |  |  |  |  |

|                      | inout              | ·    |     |      |  |  |  |  |

|                      |                    | 1    |     |      |  |  |  |  |

|                      | in                 |      |     | _    |  |  |  |  |

|                      | in                 |      |     | _    |  |  |  |  |

|                      | in                 |      |     | _    |  |  |  |  |

|                      | in                 |      |     | _    |  |  |  |  |

|                      | in<br>:-           |      |     | _    |  |  |  |  |

|                      | in                 |      |     | _    |  |  |  |  |

|                      | in                 |      |     | -    |  |  |  |  |

|                      |                    |      |     |      |  |  |  |  |

|                      | Back <u>N</u> ext> | Canc | el  | Help |  |  |  |  |

|                      |                    |      |     |      |  |  |  |  |

Click on Next in the **Define VHDL Source** window and we will get a summary of the information we just typed in:

| N                                                                                                                            | ew Source Inform                         | nation        |                    |               |            |      | × |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------|--------------------|---------------|------------|------|---|

|                                                                                                                              | Project Navigator<br>following specifica |               | a new sk           | eleton source | e with the |      |   |

| Source Type: VHDL Module<br>Source Name: leddcd<br>Entity Name: leddcd<br>Architecture Name: Behavioral<br>Port Definitions: |                                          |               |                    |               |            |      |   |

|                                                                                                                              |                                          | d<br>s        | vector:<br>vector: | 3:0<br>6:0    | in<br>out  |      |   |

|                                                                                                                              |                                          |               |                    |               |            |      |   |

|                                                                                                                              | Source Directory                         | r:            |                    |               |            |      |   |

|                                                                                                                              |                                          | < <u>B</u> ac | k [                | Finish 💦      | Cancel     | Help |   |

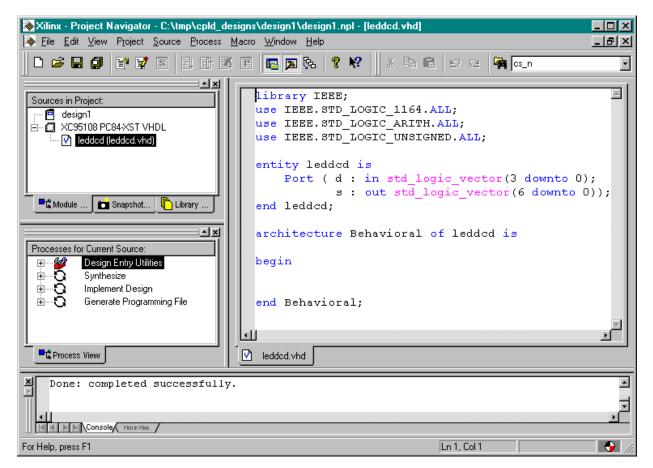

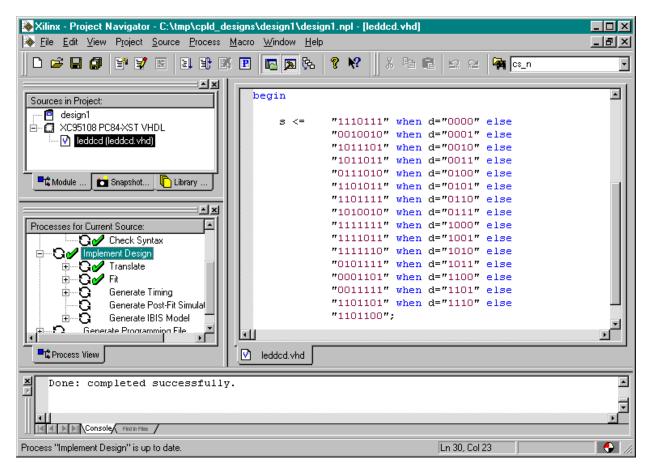

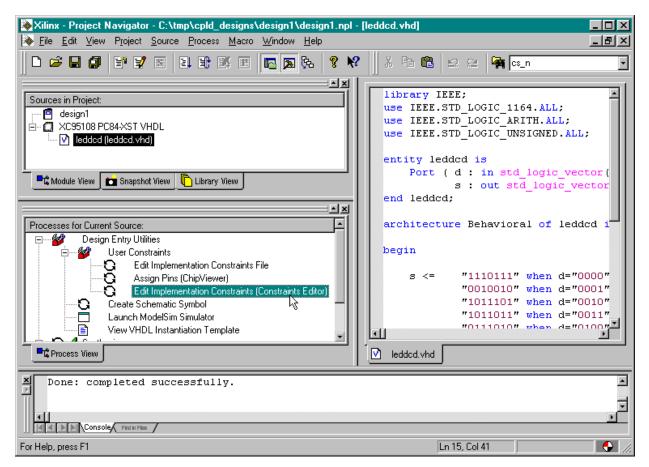

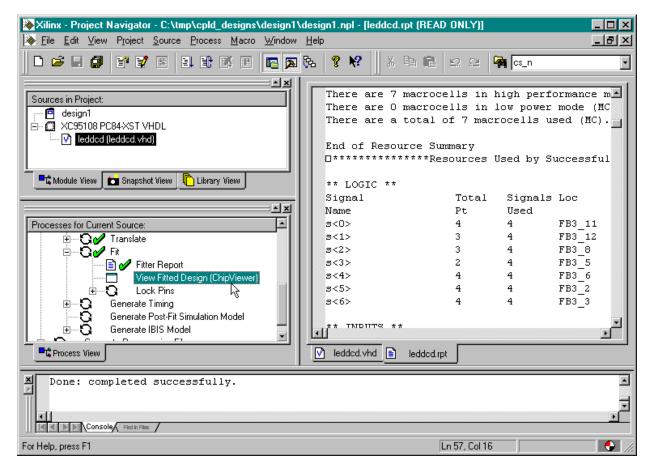

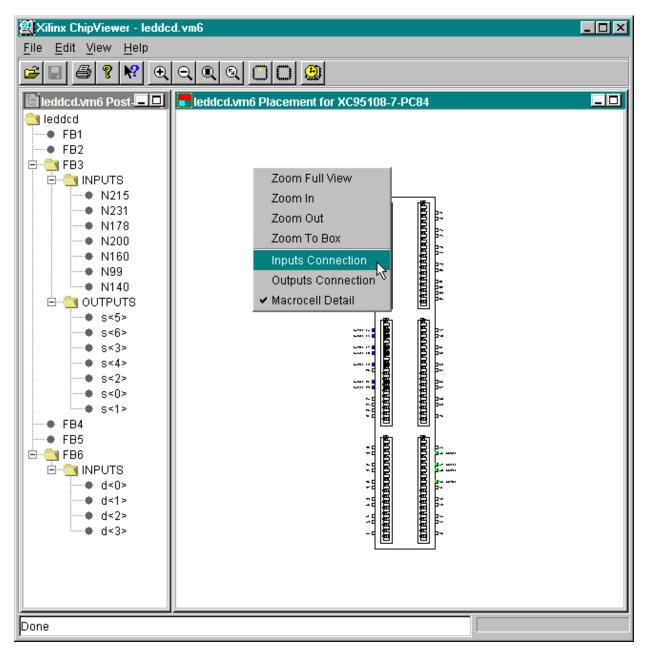

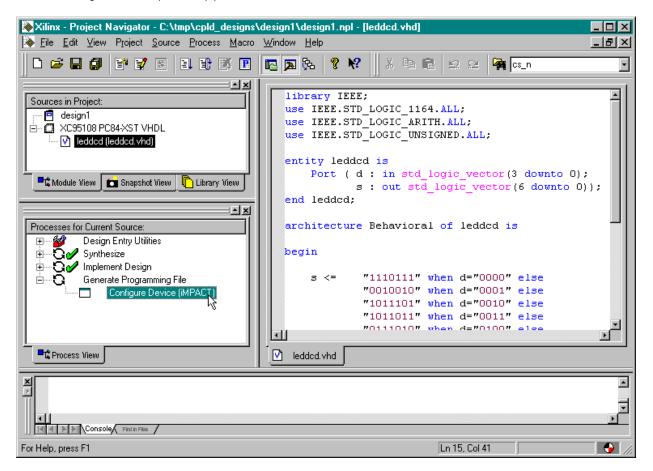

After clicking on Finish, the editor pane of the **Project Navigator** window displays a VHDL skeleton for our LED decoder. (We also see the leddcd.vhd file has been added to the Sources pane.) Lines 1-4 create links to the IEEE library and packages that contain various useful definitions for describing a design. The LED decoder inputs and outputs are declared in the VHDL entity on lines 6-9. We will describe the logic operations of the decoder in the architecture section between lines 13 and 16.

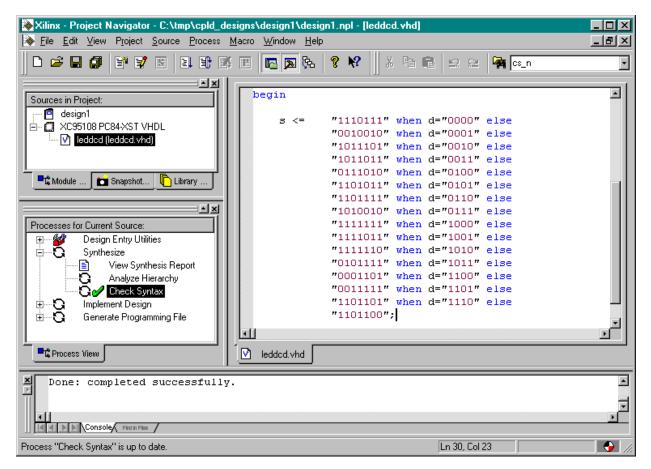

The completed VHDL file for the LED decoder is shown below. The architecture section contains a single statement which assigns a particular seven-bit pattern to the **s** output bus for any given four-bit input on the **d** bus (lines 15-30).

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use IEEE.STD LOGIC ARITH.ALL;

use IEEE.STD LOGIC UNSIGNED.ALL;

entity leddcd is

Port ( d : in std logic vector(3 downto 0);

s : out std logic vector(6 downto 0));

end leddcd;

architecture Behavioral of leddcd is

begin

s <=

"1110111" when d="0000" else

"0010010" when d="0001" else

"1011101" when d="0010" else

"1011011" when d="0011" else

"0111010" when d="0100" else

"1101011" when d="0101" else

"1101111" when d="0110" els

"1010010" when d="0111" else

"11111111" when d="1000" else

"1111011" when d="1001" else

"11111110" when d="1010" else

"01011111" when d="1011" else

"0001101" when d="1100" else

"00111111" when d="1101" else

"1101101" when d="1110" else

"1101100"

end Behavioral;

```

Once the VHDL source is entered, we click on the 🔚 button to save it in the leddcd.vhd file.

#### Checking the VHDL Syntax

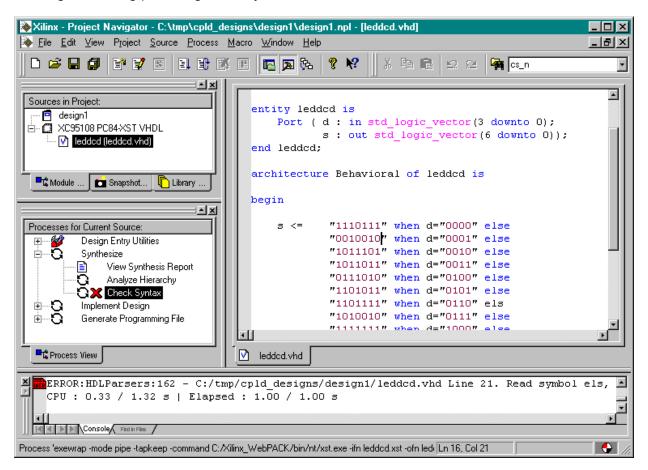

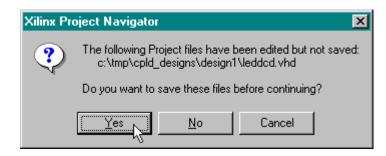

We can check for errors in our VHDL by highlighting the leddcd object in the Sources pane and then double-clicking on Check Syntax in the Process pane as shown below.

| Xilinx - Project Navigator - C:\tmp\cpld_des                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                  | - D ×<br>- B × |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 🗷 🚾 🗛 😵 😵 🛛 X 🛍 🛍 🗠 🗠 🙀 🗠 n                                                                                                                                                                                                                                      | •              |

| Sources in Project:<br>Control design1<br>Control Control | <pre>library IEEE;<br/>use IEEE.STD_LOGIC_1164.ALL;<br/>use IEEE.STD_LOGIC_ARITH.ALL;<br/>use IEEE.STD_LOGIC_UNSIGNED.ALL;<br/>entity leddcd is<br/>Port ( d : in std_logic_vector(3 downto 0);<br/>s : out std_logic_vector(6 downto 0));<br/>end leddcd;</pre> |                |

| Module 🖿 Snapshot 🖺 Library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | architecture Behavioral of leddcd is                                                                                                                                                                                                                             |                |

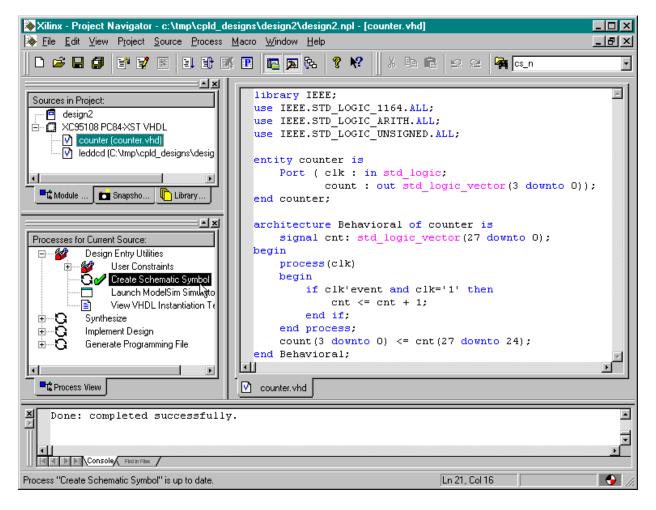

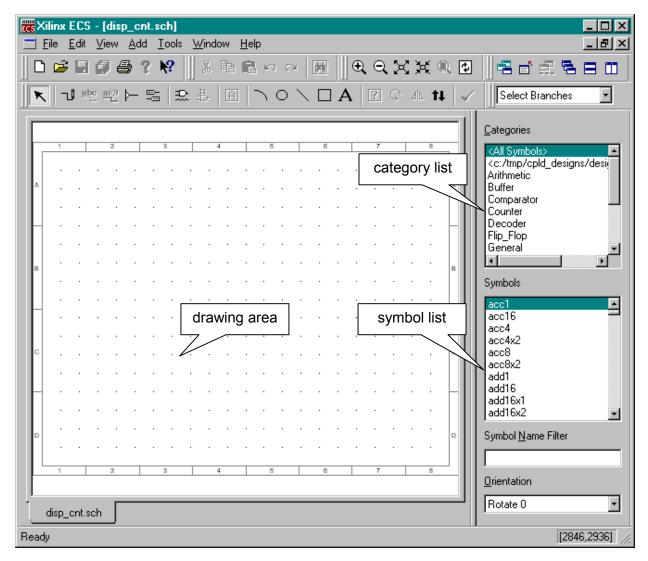

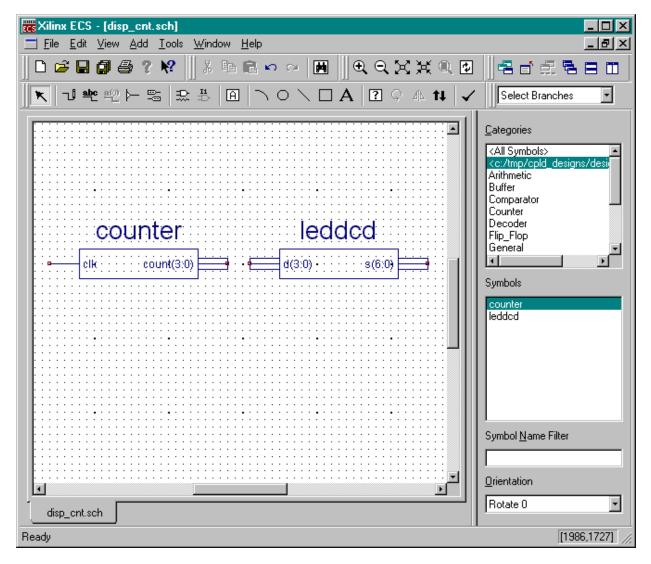

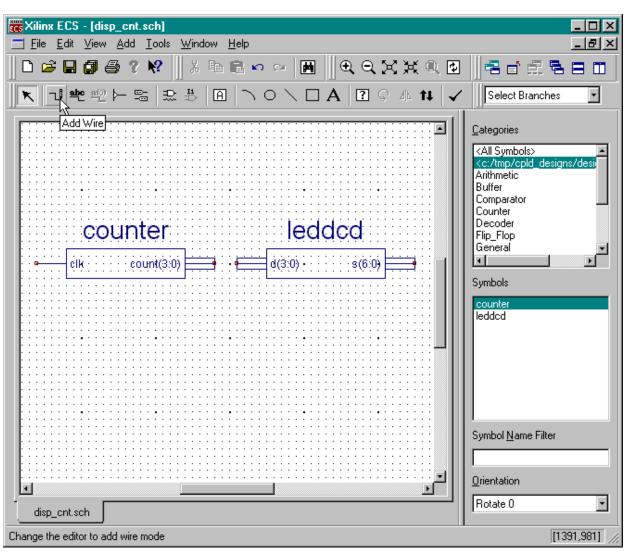

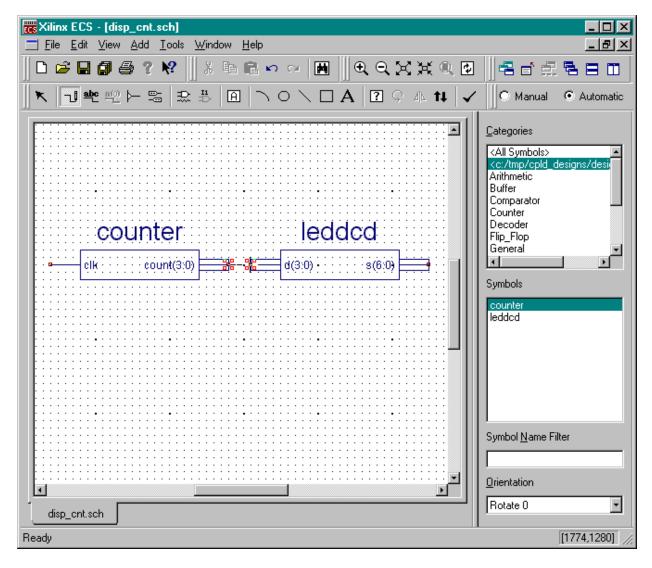

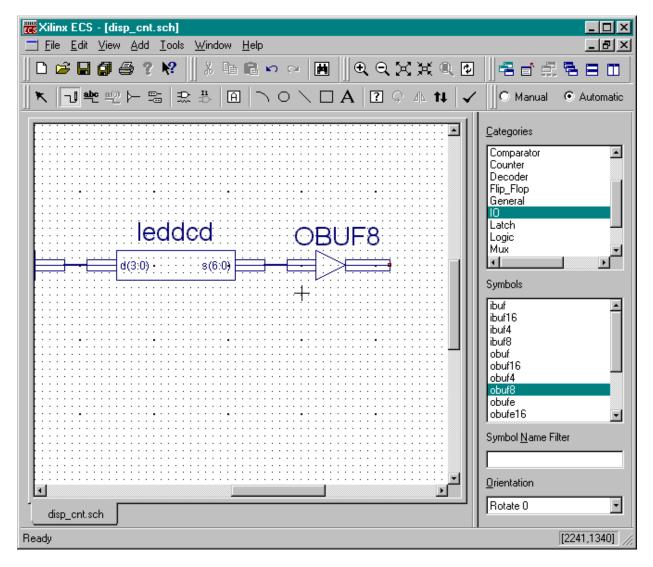

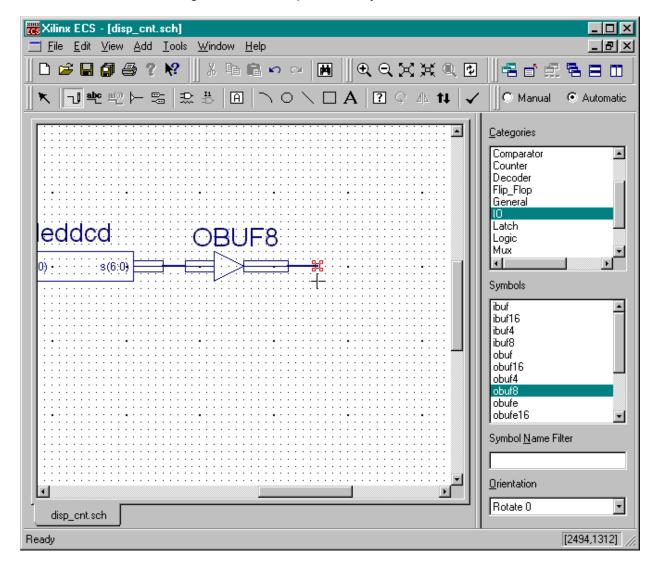

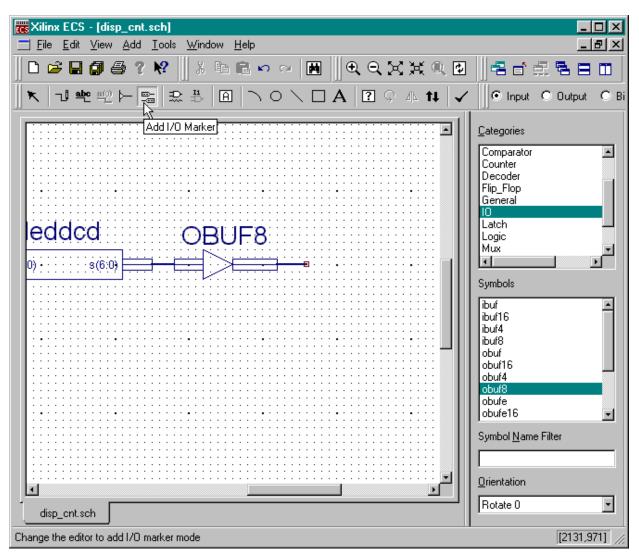

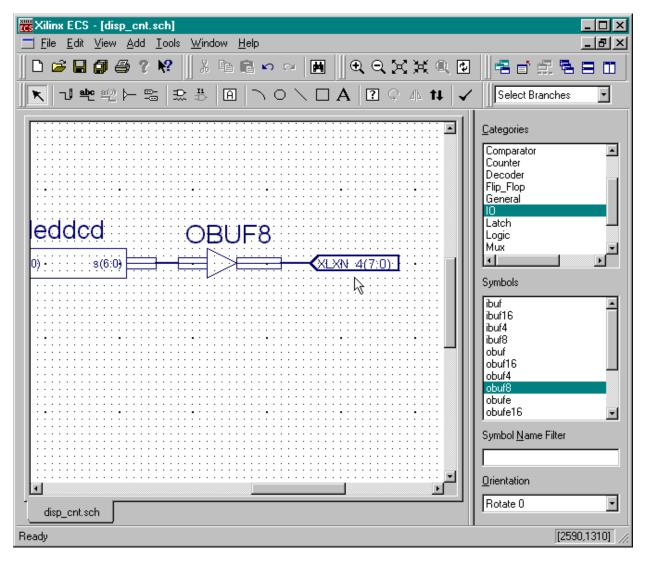

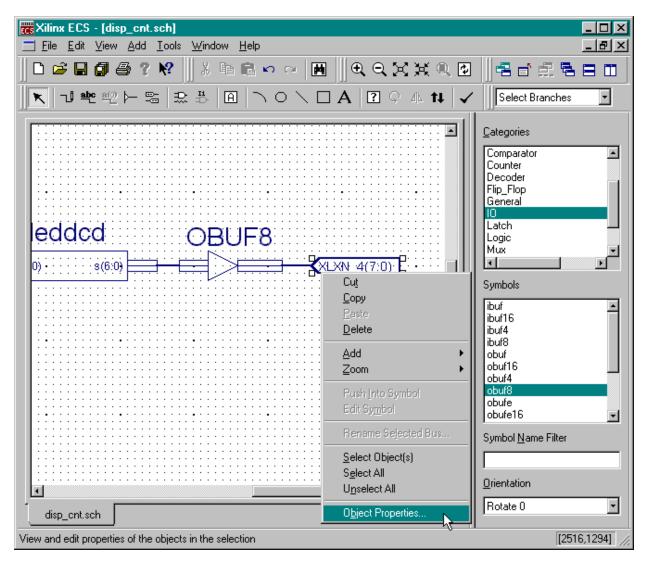

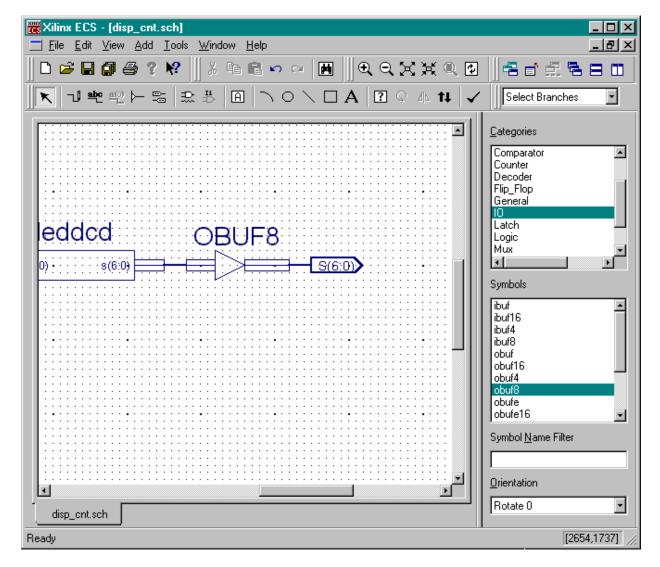

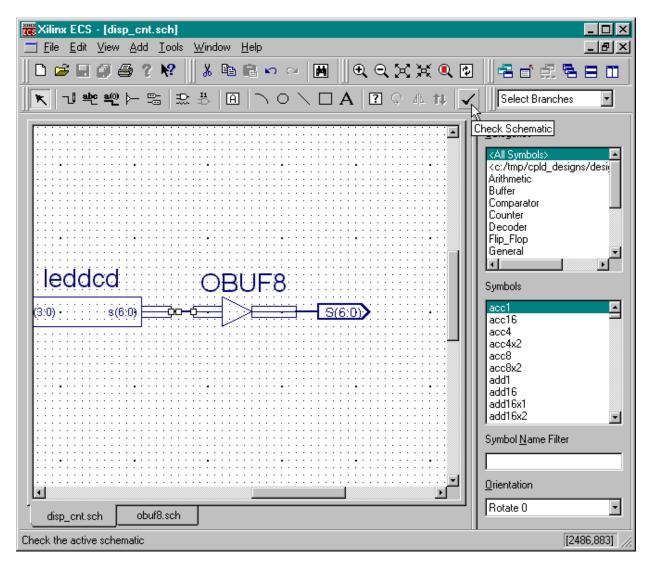

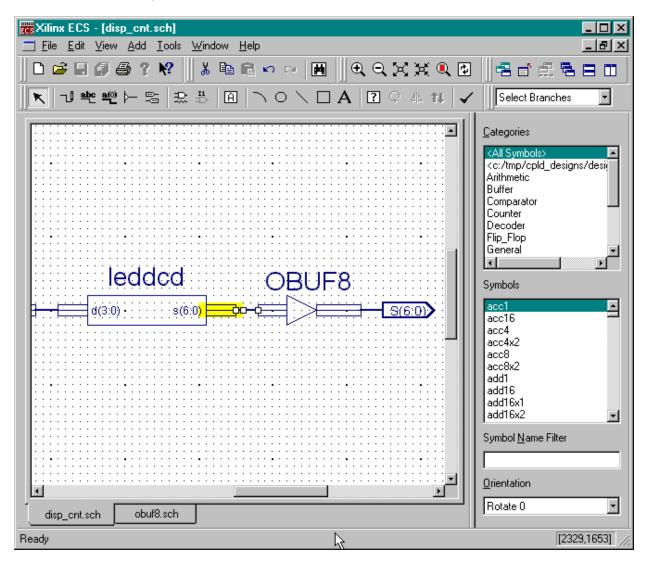

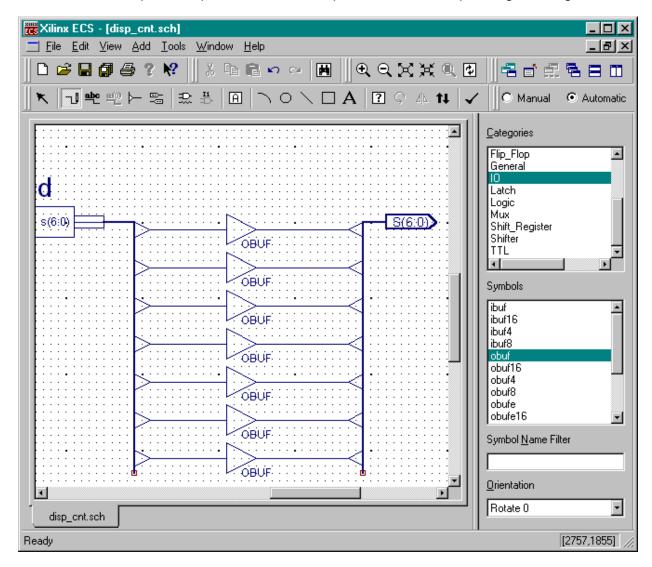

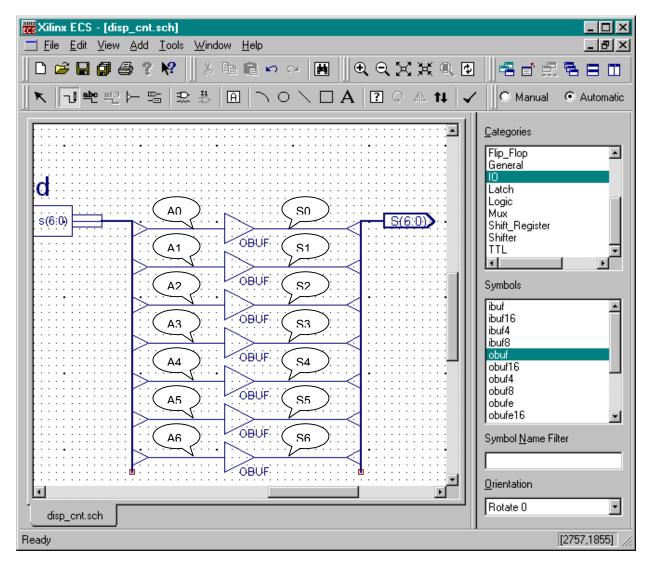

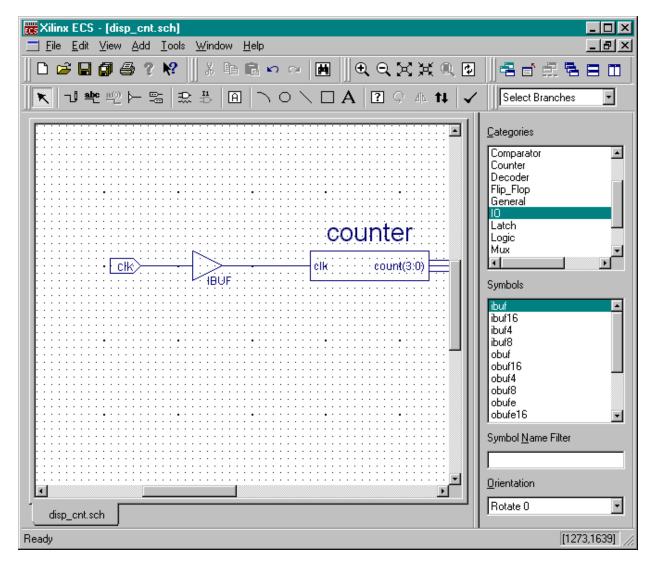

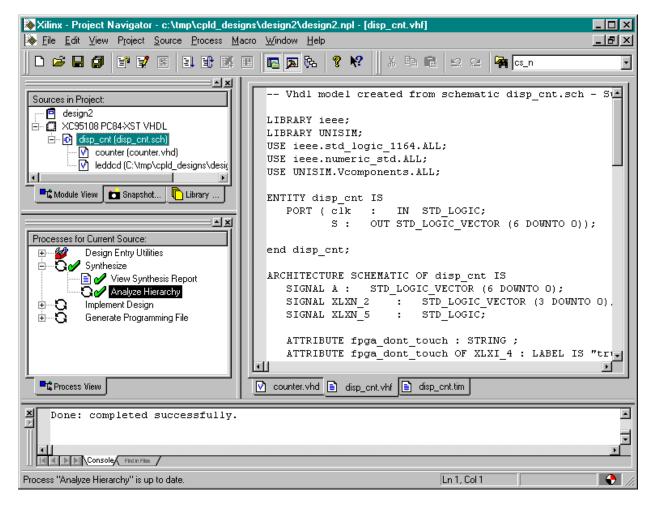

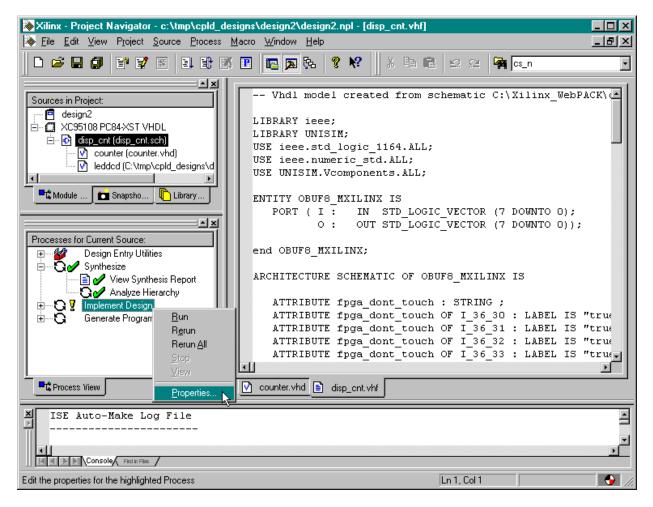

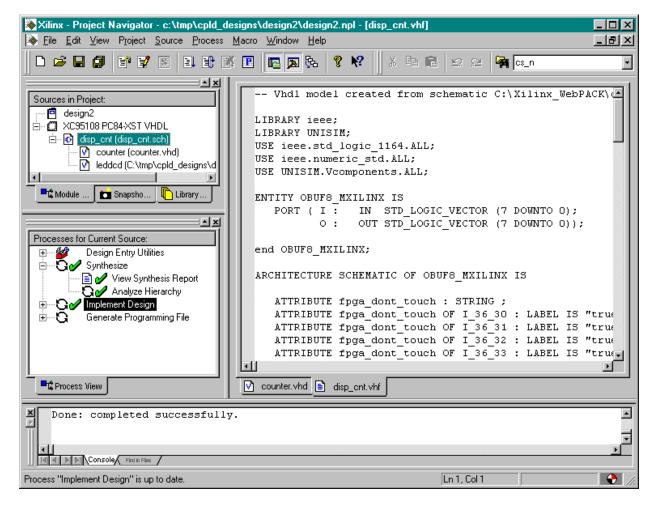

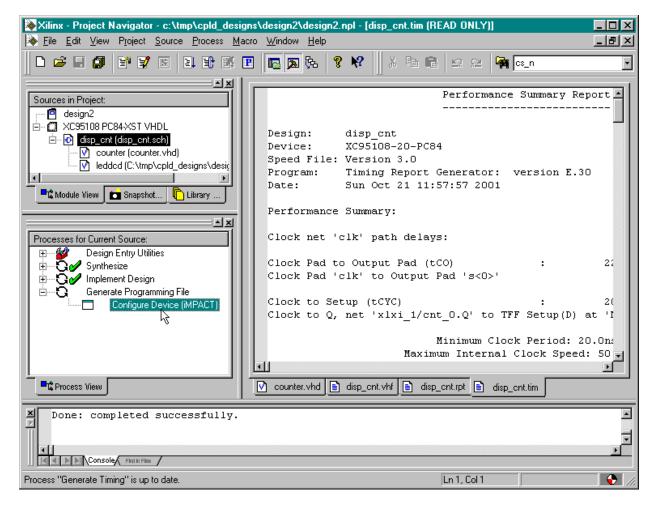

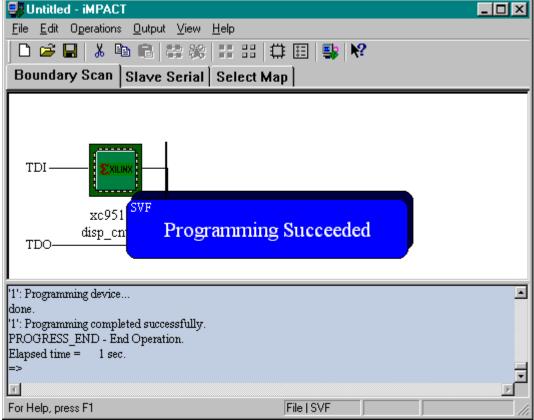

| Processes for Current Source:<br>Design Entry Utilities<br>Synthesize<br>View Synthesis Report<br>Analyze Hierarchy<br>Check Syntax<br>Implement Design<br>Generate Programming File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | begin<br>s <= "1110111" when d="0000" else<br>"0010010" when d="0001" else<br>"1011101" when d="0010" else<br>"1011011" when d="0011" else<br>"0111010" when d="0100" else<br>"1101011" when d="0101" else<br>"1010010" when d="0111" else                       | -<br>-<br>-    |